Die UDP Offload Engine ist ein IP-VHDL, das für die FPGA-Hardwareprogrammierung verwendet wird.

Diese IP ist ein UDP-IP-Stack-Beschleuniger und kann Daten über eine Ethernet-Verbindung senden und empfangen. Dieser Stack ist dank seiner konfigurierbaren Busgröße hochgradig konfigurierbar und kann mit Ethernet-Raten von bis zu 40 Gbit/s verwendet werden. Darüber hinaus ist es modular. Es implementiert verschiedene Protokolle und integrierte Testtools, die deaktiviert werden können, um Ressourcen zu sparen.

Dieses IP basiert auf Bausteinen, die der Thales-Strategie im Ingenieurwesen folgen. Sie erfüllen grundlegende Funktionen und ermöglichen die Unabhängigkeit von der Plattform/dem Ziel. Bei diesem Design werden keine Herstellerprimitive verwendet, alle werden abgeleitet.

Inhaltsverzeichnisse

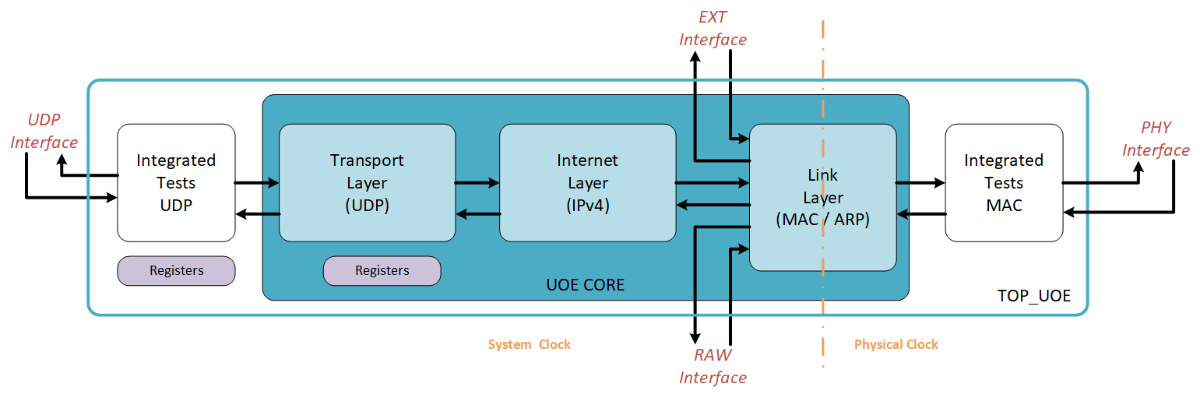

Diese Abbildung beschreibt die interne Architektur des IP. Die Hauptentität ist das Modul uoe_core . Es wurde in einen Top-Wrapper top_uoe gekapselt, der zusätzlich einige integrierte Testfunktionen instanziiert.

Funktionsteil

Integrierter Testteil (optional)

Die vollständige Dokumentation des Stacks finden Sie im Architekturhandbuch.

Konfigurierbare Busgröße

Behandeln Sie die folgenden Protokolle

Adressauflösungsprotokoll (ARP)

Internet Control Message Protocol (ICMP)

Berücksichtigen Sie Puffer auf der MAC-Schnittstelle und das Überschreiten der Taktdomäne

Filteroption für eingehenden Datenverkehr

Nutzung des Standardbusses

Das Design wurde mit verschiedenen generischen Parametern und für mehrere Ziele außerhalb des Kontexts synthetisiert und implementiert. Die Ergebnisse sind auf der Seite „Leistung“ verfügbar.

Dieses Repo integriert das folgende Designbeispiel:

Demnächst erhältlich ...

Wenn Sie daran interessiert sind, zu diesem Projekt beizutragen, lesen Sie zunächst die Richtlinien für Beiträge.