NOTIZ:

Die Dokumentation für dieses Projekt wird aktualisiert, um die Änderungen für die neu gestaltete Version von Caravel widerzuspiegeln.

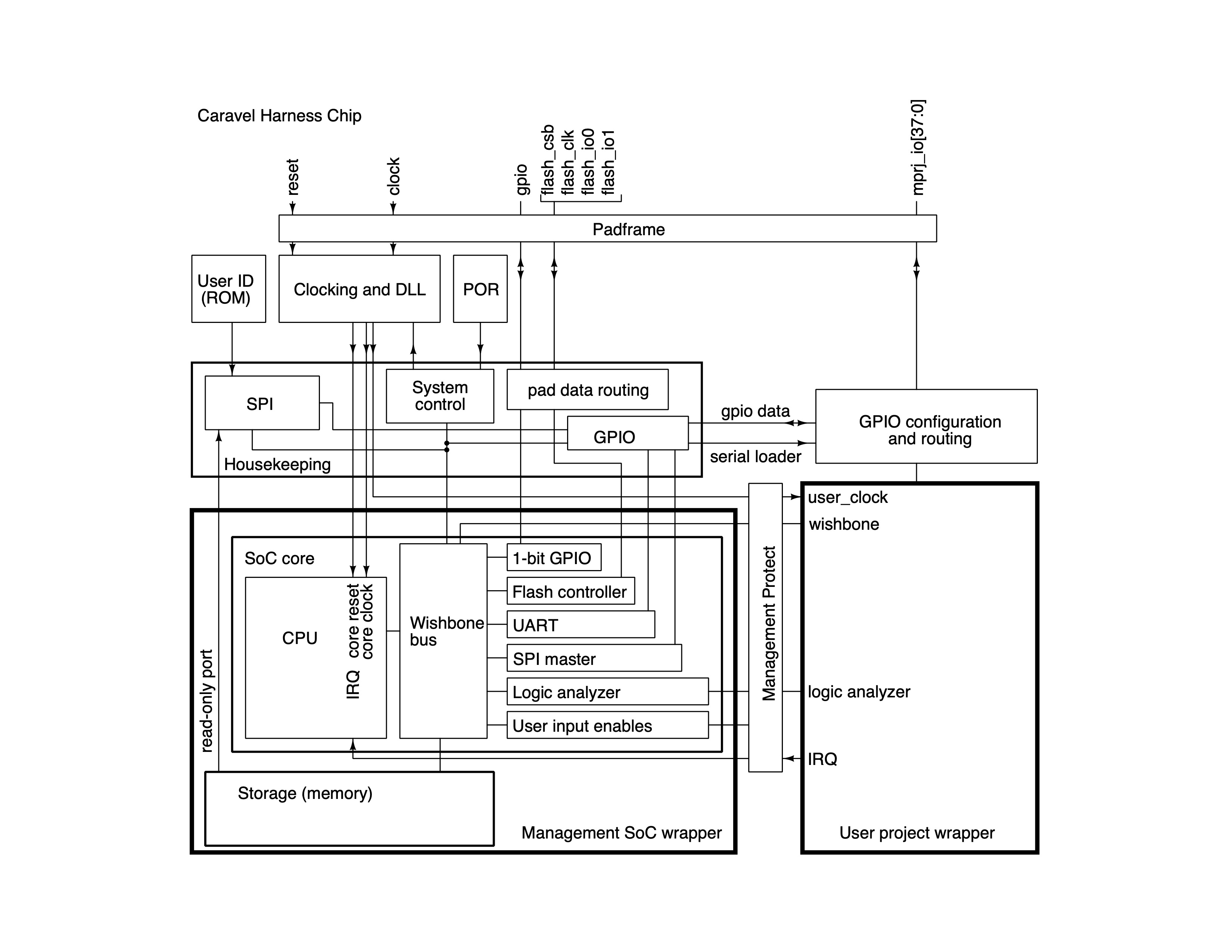

Caravel ist ein Template-SoC für Efabless Open MPW- und ChipIgnite-Shuttles, das auf dem Sky130-Knoten von SkyWater Technologies basiert. Die aktuelle SoC-Architektur ist unten angegeben.

Datenblatt und ausführliche Dokumentation finden Sie hier

Caravel besteht aus dem Kabelbaumrahmen und zwei Hüllen für Drop-In-Module für den Verwaltungsbereich und den Benutzerprojektbereich .

Der Kabelbaum selbst enthält das Taktmodul, DLL, Benutzer-ID, Housekeeping-SPI, POR und GPIO-Steuerung.

Die GPIO-Verwaltung wurde vom Management-SoC in SPI verlagert. SPI erhält eine Wishbone-Schnittstelle; Der Management-SoC kommuniziert mit dem SPI über Wishbone und nicht über die Übernahme der 4-Pin-SPI-Schnittstelle.

Ein neuer Block wie die ID hat den Modus beim Einschalten für jeden GPIO. Kann mit einer Textdatei konfiguriert werden. SPI-Pins sind für den Betrieb beim Start fixiert.

Beim Einschalten konfiguriert der SPI automatisch den GPIO. Manuelles Laden ist sowohl vom SPI als auch vom Wishbone-Bus möglich.

Alle Funktionen innerhalb des Kabelbaums, aber außerhalb des Management-SoCs, sind in einem großen Modul namens „Housekeeping“ integriert. Dazu gehören eine Reihe von Registern für alle enthaltenen Funktionen, mit einer „Front Door“-SPI-Schnittstelle, die über die GPIO-Pins 1 bis 4 mit dem Padframe verbunden ist, und einer „Back Door“-Querlenkerschnittstelle, die mit dem Management-SoC verbunden ist. Der Management-SOC reserviert den Speicherblock bei 0x26000000 für das Housekeeping-Modul. Das Housekeeping-Modul tauscht Daten mit dem Management-SoC über eine Schnittstelle aus, die die byteweiten SPI-Registerdaten nutzt. Eine kleine Zustandsmaschine liest vier zusammenhängende Wishbone-Adressen und ein Adressdecoder ermittelt das entsprechende SPI-Register. Die Zustandsmaschine blockiert den SoC, bis alle vier Bytes verarbeitet wurden, bevor sie das Bestätigungssignal zurückgibt.

Der Verwaltungsbereich ist ein Drop-In-Modul, das als separates Repo implementiert ist. Es umfasst typischerweise einen RISC-V-basierten SoC, der eine Reihe von Peripheriegeräten wie Timer, UART und GPIO umfasst. Im Verwaltungsbereich wird Firmware ausgeführt, die für Folgendes verwendet werden kann:

Der Managementbereich implementiert SRAM für den Management-SoC.

Die Standardinstanziierung für den Verwaltungskern finden Sie hier. Weitere Einzelheiten finden Sie in der Dokumentation des Verwaltungskerns.

Dies ist der Benutzerbereich. Es verfügt über eine begrenzte Siliziumfläche 2.92mm x 3.52mm sowie eine feste Anzahl von I/O-Pads 38 und Power-Pads 4 .

Der Benutzerbereich hat Zugriff auf die folgenden vom Management-SoC bereitgestellten Dienstprogramme:

38 IO-Ports128 Logikanalysator-Sonden Ihr Bereich ist der vollständige Benutzerbereich. Sie können also Ihr Projekt dort hinzufügen oder ein anderes Makro erstellen und es separat härten. Fügen Sie es dann in den user_project_wrapper für digitale Projekte oder in den user_project_analog_wrapper für analoge Projekte ein.

Wenn Sie ein digitales Projekt für den Benutzerbereich erstellen, sehen Sie sich ein Beispielprojekt unter caravel_user_project an.

Wenn Sie OpenLANE zum Härten Ihres Designs verwenden, gehen Sie die Anweisungen in dieser README-Datei durch.

Digitale Nutzerprojekte sollten folgende Anforderungen erfüllen:

user_project_wrapperuser_project_wrapper hält sich an die Pin-Reihenfolge, die unter Digital Wrapper Pin Order definiert ist.user_project_wrapper hält sich an die festen Designkonfigurationen unter „Digital Wrapper Fixed Configuration“.Wenn Sie ein analoges Projekt für den Benutzerbereich erstellen, sehen Sie sich ein Beispielprojekt unter caravel_user_project_analog an.

Analoge Benutzerprojekte sollten die folgenden Anforderungen erfüllen:

user_analog_project_wrapperuser_analog_project_wrapper verwendet den leeren analogen Wrapper.user_analog_project_wrapper folgt der gleichen Pin-Reihenfolge und Platzierung wie der leere analoge Wrapper. Bitte stellen Sie sicher, dass Sie make compress ausführen, bevor Sie etwas in Ihr Repository übertragen. Vermeiden Sie zwei Versionen von gds/user_project_wrapper.gds eine komprimierte und die andere nicht komprimierte.

Informationen zu Tools und Versionierung finden Sie unter tool-versioning.rst.

gds/ : Enthält alle vom Projekt verwendeten oder erstellten gds-Dateien.def : Enthält alle vom Projekt verwendeten oder erstellten Def-Dateien.lef/ : Enthält alle vom Projekt verwendeten oder erstellten LEF-Dateien.mag/ : Enthält alle im Projekt verwendeten oder erstellten Mag-Dateien.maglef : Enthält alle vom Projekt verwendeten oder erstellten Maglef-Dateien.spi/lvs/ : Enthält alle vom Projekt verwendeten oder erstellten Spice-Dateien.verilog/dv : Enthält alle Simulationsprüfstände und deren Ausführung.verilog/gl/ : Enthält alle synthetisierten/ausgearbeiteten Netzlisten.verilog/rtl : Enthält alle Verilog-RTLs und Quelldateien.openlane/<macro>/ : Enthält alle Konfigurationsdateien, die zum Ausführen von openlane in Ihrem Projekt verwendet werden.info.yaml : Enthält alle in diesem Beispiel erforderlichen Informationen. Bitte stellen Sie sicher, dass Sie auf eine ausgearbeitete Karavellen-Netzliste sowie eine synthetisierte Netzliste auf Gate-Ebene für den user_project_wrapper verweisenNOTIZ:

Wenn Sie Openlane verwenden, um Ihr Design zu härten, sollten die Verzeichnisseverilog/gldef/lef/gds/magmaglefautomatisch von Openlane gefüllt werden.

Suchen Sie in mpw-one-final nach der Karavelle, die für das mpw-one-Tapeout verwendet wird.

>make ship ist nicht mehr erforderlich.