Fühlen Sie sich frei, ein Problem oder PR zu öffnen, wenn Sie Vorschläge haben. Und wenn Sie es hilfreich fanden, möchten Sie möglicherweise einen dieser Links besuchen:

Ich habe diese zufällige Nerds -Seite immer als Referenz verwendet, für die ESP32 -Stifte sicher verwendet werden können.

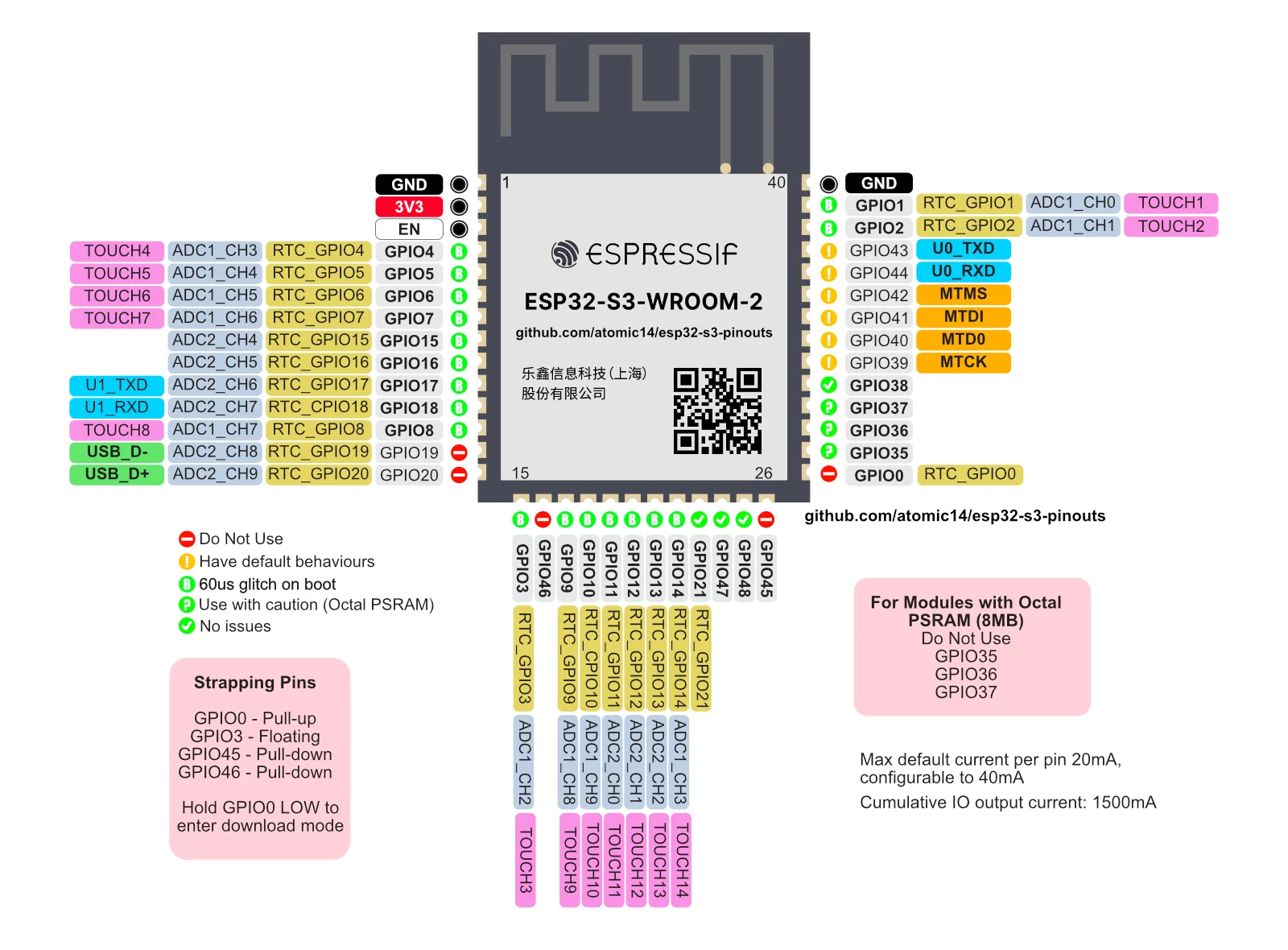

Aber ich habe keinen ähnlichen für den ESP32 -S3 gesehen - also dachte ich, ich sollte eines machen!

Der Großteil dieser Informationen stammt aus dem ESP32-S3-W-Room-Datenblatt mit zusätzlichen Informationen aus dem ESP32-S3-Datenblatt.

Sie können hier eine hochauflösende PDF -Version dieses Bildes herunterladen.

Das obige Bild ist ein Wroom -Modul mit den gekennzeichneten Stiften. Fett zeigt das Standardverhalten jedes Pin an. Ich habe einige der namens esoterischeren Pins -Namen geeignet, aber Sie finden die vollständige Liste im Datenblatt.

Mit dem ESP32-S3 gibt es viel mehr Flexibilität, sodass die meisten Stifte für jeden Peripheriegerät verwendet werden können. Es gibt jedoch immer noch einige Stifte, die ein lustiges Verhalten haben.

Vermeiden Sie diese, es sei denn, Sie haben keine Wahl.

| Pin -Name | Details |

|---|---|

| Gpio0 | Halten Sie diesen Tief während des Starts, um den Firmware -Download -Modus einzugeben. |

| Gpio3 | In Kombination mit EFUSE steuert das Standardverhalten der JTAG -Stifte. Sicher zu verwenden, es sei denn, Sie spielen mit Efusen |

| Gpio45 | VDD_SPI - Lassen Sie dies am besten getrennt |

| Gpio46 | ROM -Nachrichten drucken - am besten, um dies auch getrennt zu lassen. Verursacht Probleme mit dem Download der Firmware (siehe TOFT -MODE -Steuerungstabelle unten) |

Sie können diese Stifte als Eingänge oder Ausgänge verwenden, sobald das ESP gebootet ist. Aber seien Sie sich der Aufstände auf/ab (siehe unten).

Wenn Sie sie als Eingaben verwenden möchten, stellen Sie sicher, dass Sie während des BOOT nicht mit den Standardkonfigurationen in Konflikt stehen.

ZB Es ist sicher, dass eine Schaltfläche mit GPIO0 angeschlossen ist und diese Taste in Ihrem Code verwendet. Wenn Sie jedoch die Schaltfläche während des BOOT gedrückt halten, wird der Download -Modus des Firmware -Downloads eingegeben.

Wenn Sie sie als Ausgänge verwenden möchten, sind Sie sich des Standard -Pull -Up- oder Pull -Down -Widerstands bewusst.

| Boot -Modus | Gpio0 | Gpio46 |

|---|---|---|

| SPI -Boot (Standard) | 1 | Jeder Wert |

| Start herunterladen | 0 | 0 |

| Ungültige Kombination | 0 | 1 |

| Pin | Standardkonfiguration | Bitwert |

|---|---|---|

| Gpio0 | Pull-up | 1 |

| Gpio3 | Schwebend | - - |

| Gpio45 | Pulldown | 0 |

| Gpio46 | Pulldown | 0 |

Diese können alle GPIO-Stifte auf dem ESP32-S3 verwenden.

Gpio19, gpio20 - beide werden für die USB -Verbindung verwendet.

Für Module, die Octal PSRAM (jedes Modul mit 8 MB PSRAM) enthalten, dürfen Sie GPIO35, GPIO36 oder GPIO37 nicht verwenden.

Gpio39, gpio40, gpio41, gpio42

Das Verhalten dieser Stifte wird durch Efuse in Verbindung mit GPIO3 bestimmt. Wenn Sie noch keine Efuse verbrannt haben, sind diese Stifte sicher zu verwenden. JTAG wird über USB erhältlich sein.

Wenn Sie diese Pins für JTAG verwenden möchten, müssen Sie einige Efuse verbrennen und GPIO3 beim Start steuern. Ausführliche Informationen finden Sie im Abschnitt 2.6.4 im Datenblatt.

Gpio43, gpio44

Diese standardmäßig an UART0, bis sie von Ihrem Code verwendet werden.

Die ADC -Kanäle befinden sich alle auf festen Stiften. Wenn Sie WLAN verwenden, können Sie die ADC -Einheit 2 nicht verwenden

Die Stifte für die ADC -Einheit 1 sind:

| GPIO -Nummer | ADC -Kanal |

|---|---|

| Gpio1 | ADC1_CH0 |

| Gpio2 | ADC1_CH1 |

| Gpio3 | ADC1_CH2 |

| Gpio4 | ADC1_CH3 |

| Gpio5 | ADC1_CH4 |

| Gpio6 | ADC1_CH5 |

| Gpio7 | ADC1_CH6 |

| Gpio8 | ADC1_CH7 |

| Gpio9 | ADC1_CH8 |

Es gibt keinen DAC auf dem ESP32 -S3 - Sie können den analogen Ausgang mit PWM- oder I2S PDM simulieren.

Die folgenden Stifte haben Störungen während des Auftriebs.

Gpio1, gpio2, gpio3, gpio4, gpio5, gpio6, gpio7, gpio8, gpio9, gpio10, gpio11, gpio12, gpio13, gpio14, gpio15, gpio16, gpio17

Gpio18:

Gpio19, gpio20:

Siehe Tabelle-2-2 hier

Wenn Sie beim Ausführen Ihrer Software "Ihre" Software, aber nicht beim Ausführen einer einfachen Hello -Welt auf einigen Pins sehen, ist dies möglicherweise ein häufiger Fehler:

gpio_reset_pin ( RELAY1_SC );

gpio_set_direction ( RELAY1_SC , GPIO_MODE_OUTPUT );Diese Syntax kann hier z. B. Blink_example_main.c gefunden werden

Verwenden Sie stattdessen diese Syntax:

//zero-initialize the config structure.

gpio_config_t io_conf = {};

//disable interrupt

io_conf . intr_type = GPIO_INTR_DISABLE ;

//set as output mode

io_conf . mode = GPIO_MODE_OUTPUT ;

//bit mask of the pins that you want to set,e.g.GPIO18/19

io_conf . pin_bit_mask = ( 1ULL << RELAY1_SC );

//disable pull-down mode

io_conf . pull_down_en = 0 ;

//disable pull-up mode

io_conf . pull_up_en = 0 ;

//configure GPIO with the given settings

gpio_config ( & io_conf );Diese Syntax ist hier zu finden, z. B.: gpio_example_main.c

Es gibt Fälle, in denen der Pin standardmäßig mit einer Leistungsdomäne von A +3,3 V oder A +1,8 V angeschlossen ist. Beispiele sind gpio20 (d+) oder gpio48.

Sie können sie in einem sehr frühen Stadium im Bootloader ausschalten:

Siehe hier

mit zB dem folgenden Code:

void bootloader_before_init ( void ) {

/* Keep in my mind that a lot of functions cannot be called from here

* as system initialization has not been performed yet, including

* BSS, SPI flash, or memory protection. */

ESP_LOGI ( "HOOK" , "This hook is called BEFORE bootloader initialization" );

gpio_hal_iomux_func_sel ( GPIO_PIN_MUX_REG [ GPIO_NUM_20 ], PIN_FUNC_GPIO );

esp_rom_gpio_pad_select_gpio ( GPIO_NUM_48 );

gpio_ll_output_enable ( & GPIO , GPIO_NUM_48 );

gpio_ll_set_level ( & GPIO , GPIO_NUM_48 , 0 );

}Hier gibt es eine sehr praktische Tabelle von Mark Nowell mit Listen von ESP32-S3-Modulen und deren Pinouts.

| Pin -Name | PIN -Nummer | Typ | Beschreibung |

|---|---|---|---|

| GND | 1,40 | P | GND |

| EPAD | 41 | P | GND |

| 3v3 | 2 | P | Stromversorgung |

| En | 3 | ICH | Hoch: Ermöglicht den Chip. Niedrig: Aus dem Chip macht der Chip ab. HINWEIS: Lassen Sie den Bin nicht schweben. |

| Gpio0 | 27 | E/O/T | RTC_GPIO0, GPIO0 |

| Gpio1 | 39 | E/O/T | Rtc_gpio1, gpio1 , touch1, adc1_ch0 |

| Gpio2 | 38 | E/O/T | Rtc_gpio2, gpio2 , touch2, adc1_ch1 |

| Gpio3 | 15 | E/O/T | Rtc_gpio3, gpio3 , touch3, adc1_ch2 |

| Gpio4 | 4 | E/O/T | Rtc_gpio4, gpio4 , touch4, adc1_ch3 |

| Gpio5 | 5 | E/O/T | Rtc_gpio5, gpio5 , touch5, adc1_ch4 |

| Gpio6 | 6 | E/O/T | Rtc_gpio6, gpio6 , touch6, adc1_ch5 |

| Gpio7 | 7 | E/O/T | Rtc_gpio7, gpio7 , touch7, adc1_ch6 |

| Gpio8 | 12 | E/O/T | Rtc_gpio8, gpio8 , touch8, adc1_ch7, subspics1 |

| Gpio9 | 17 | E/O/T | Rtc_gpio9, gpio9 , touch9, adc1_ch8, fspihd, subspihd |

| Gpio10 | 18 | E/O/T | Rtc_gpio10, gpio10 , touch10, adc1_ch9, fspics0, fspiio4, subspics0 |

| Gpio11 | 19 | E/O/T | Rtc_gpio11, gpio11 , touch11, adc2_ch0, fspid, fspiio5, subspid |

| Gpio12 | 20 | E/O/T | RTC_GPIO12, GPIO12 , Touch12, ADC2_Ch1, FSPICLK, FSPIIO6, Subspiclk |

| Gpio13 | 21 | E/O/T | Rtc_gpio13, gpio13 , touch13, adc2_ch2, fspiq, fspiio7, subspiq |

| Gpio14 | 22 | E/O/T | Rtc_gpio14, gpio14 , touch14, adc2_ch3, fspiwp, fspidqs, subspiwp |

| Gpio15 | 8 | E/O/T | RTC_GPIO15, GPIO15 , U0RTS, ADC2_CH4, XTAL_32K_P |

| Gpio16 | 9 | E/O/T | RTC_GPIO16, GPIO16 , U0CTS, ADC2_CH5, XTAL_32K_N |

| Gpio17 | 10 | E/O/T | Rtc_gpio17, gpio17 , u1txd, adc2_ch6 |

| Gpio18 | 11 | E/O/T | Rtc_gpio18, gpio18 , u1rxd, adc2_ch7, clk_out3 |

| USB_D- | 13 | E/O/T | Rtc_gpio19, gpio19, u1rts, adc2_ch8, clk_out2, USB_D- |

| USB_D+ | 14 | E/O/T | RTC_GPIO20, GPIO20, U1CTS, ADC2_CH9, CLK_OUT1, USB_D+ |

| Gpio21 | 23 | E/O/T | RTC_GPIO21, GPIO21 |

| Spics1 | E/O/T | Spics1, gpio26 | |

| Gpio33 | E/O/T | Gpio33 | |

| Gpio34 | E/O/T | Gpio33 | |

| Gpio35 | 28 | E/O/T | Spiio6, gpio35 , fspid, subspid |

| Gpio36 | 29 | E/O/T | Spiio7, gpio36 , fspiclk, subspiclk |

| Gpio37 | 30 | E/O/T | SPIDQS, GPIO37 , FSPIQ, Subspiq |

| Gpio38 | 31 | E/O/T | Gpio38 , fspiwp, subspiwp |

| Mtck | 32 | E/O/T | MTCK , GPIO39, CLK_OUT3, Subspics1 |

| Mtdo | 33 | E/O/T | Mtdo , gpio40, clk_out2 |

| Mtdi | 34 | E/O/T | Mtdi , gpio41, clk_out1 |

| MTMS | 35 | E/O/T | MTMS , GPIO42 |

| U0TXD | 37 | E/O/T | U0txd , gpio43, clk_out1 |

| U0rxd | 36 | E/O/T | U0rxd , gpio44, clk_out2 |

| Gpio45 | 26 | E/O/T | Gpio45 |

| Gpio46 | 16 | E/O/T | Gpio46 |

| Gpio47 | 24 | E/O/T | Spiclk_p_diff, gpio47 , subspiclk_p_diff |

| Gpio48 | 25 | E/O/T | Spiclk_n_diff, gpio48 , subspiclk_n_diff |

Für Personen, die Videoinhalte bevorzugen - können Sie hier eine Videoversion sehen: