El motor de descarga UDP es un VHDL IP que se utiliza para la programación de hardware FPGA.

Esta IP es un acelerador de pila UDP-IP y puede enviar y recibir datos a través de un enlace Ethernet. Esta pila es altamente configurable para usarse con velocidades Ethernet de hasta 40 Gb/s gracias a su tamaño de bus configurable. Además es modular. Implementa diferentes protocolos y herramientas de prueba integradas que se pueden desactivar para ahorrar recursos.

Esta IP se basa en Building Blocks siguiendo la Estrategia Thales en ingeniería. Realizan funciones básicas y permiten ser independientes de la plataforma/objetivo. En este diseño no se utiliza ninguna primitiva del fabricante, todas se infieren.

Tablas de contenidos

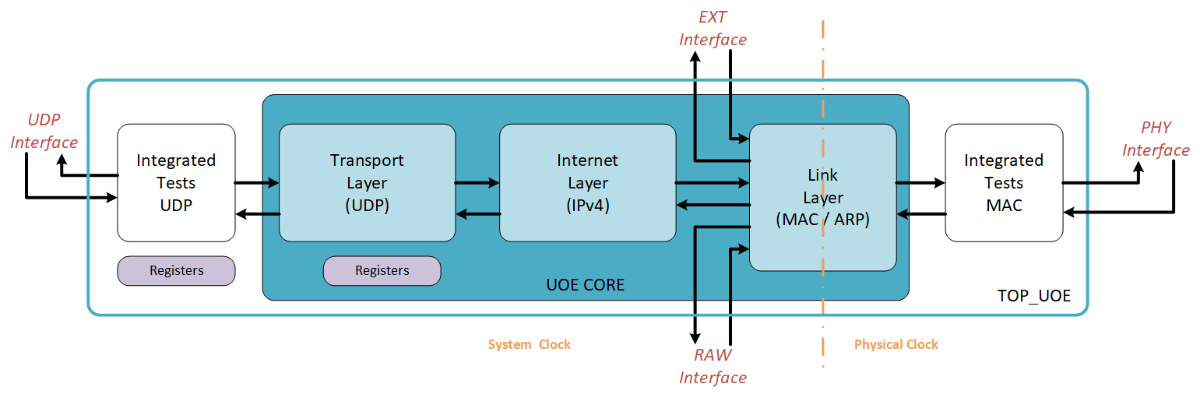

Esta figura describe la arquitectura interna de la IP. La entidad principal es el módulo uoe_core . Fue encapsulado en un contenedor superior top_uoe que además crea una instancia de algunas funciones de prueba integradas.

parte funcional

Pieza de prueba incorporada (opcional)

La documentación completa de la pila está disponible en la guía de arquitectura.

Tamaño de autobús configurable

Manejar los siguientes protocolos

Protocolo de resolución de direcciones (ARP)

Protocolo de mensajes de control de Internet (ICMP)

Tenga en cuenta los buffers en la interfaz MAC y el cruce de dominios de reloj

Opción de filtrado para el tráfico entrante.

Uso de autobús estándar

El diseño ha sido sintetizado e implementado con diferentes parámetros genéricos y para varios objetivos fuera de contexto. Los resultados están disponibles en la página Rendimiento.

Este repositorio integra el siguiente ejemplo de diseño:

Muy pronto ...

Si está interesado en contribuir a este proyecto, comience leyendo las Pautas de contribución.