NOTA:

La documentación de este proyecto se está actualizando para reflejar los cambios de la nueva versión rediseñada de Caravel.

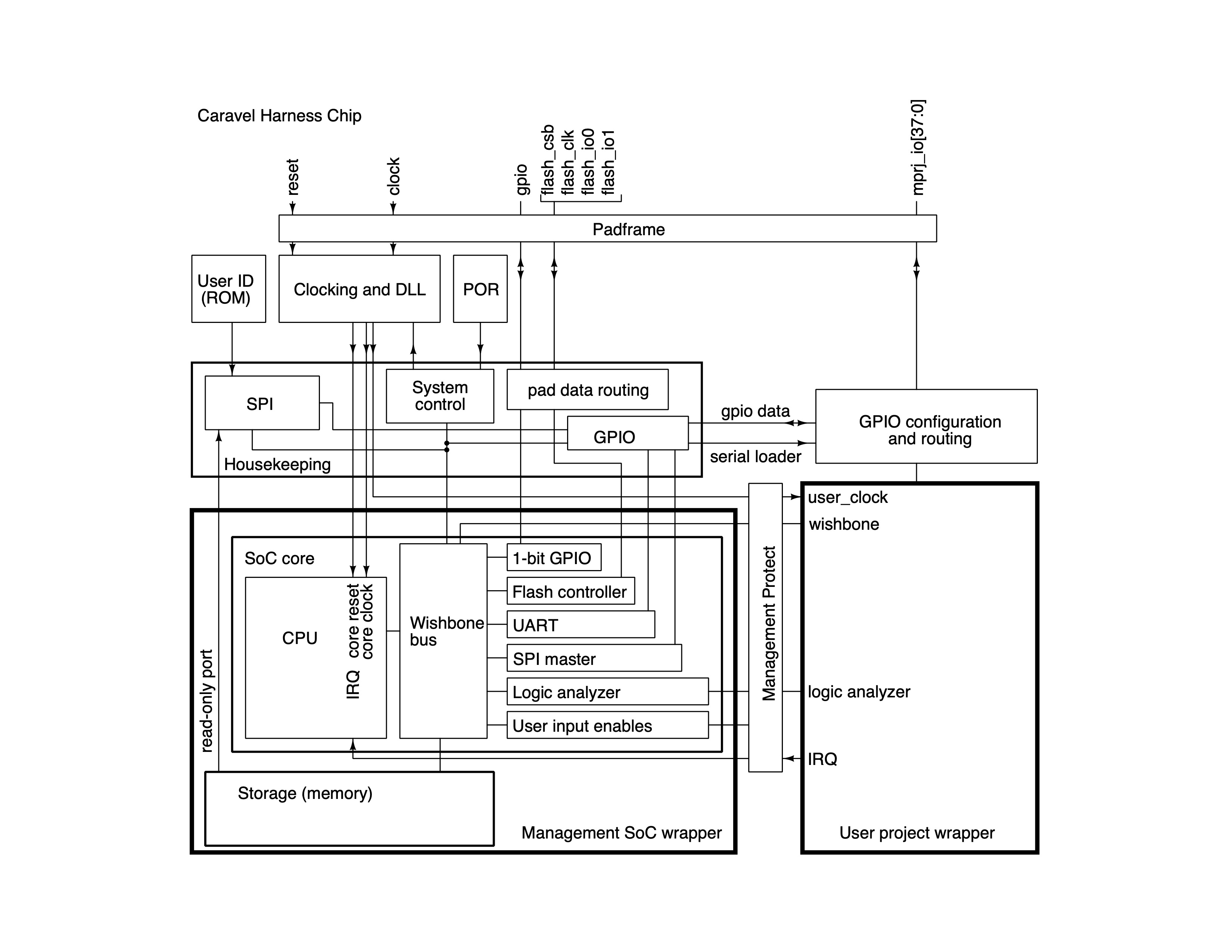

Caravel es un SoC de plantilla para Efabless Open MPW y lanzaderas chipIgnite basado en el nodo Sky130 de SkyWater Technologies. La arquitectura actual de SoC se detalla a continuación.

La hoja de datos y la documentación detallada existen aquí.

Caravel se compone del marco del arnés más dos envoltorios para módulos empotrables para el área de gestión y el área de proyectos del usuario .

El arnés en sí contiene el módulo de sincronización, DLL, ID de usuario, control SPI, POR y GPIO.

El manejo de GPIO pasó del SoC de administración a SPI. SPI obtiene una interfaz de horquilla; el SoC de administración se comunica con el SPI a través de la horquilla, no asumiendo la interfaz SPI de 4 pines.

Un nuevo bloque como el ID tiene el modo de encendido para cada GPIO. Se puede configurar con un archivo de texto. Los pines SPI están fijos para funcionar al inicio.

Al encenderse, el SPI configura automáticamente el GPIO. La carga manual es posible tanto desde el SPI como desde el bus transversal.

Todas las funciones dentro del arnés pero fuera del SoC de gestión están incorporadas en un gran módulo llamado "limpieza". Esto incluye una serie de registros para todas las funciones incluidas, con una interfaz SPI de "puerta frontal" conectada al padframe a través de los pines GPIO 1 a 4, y una interfaz de horquilla de "puerta trasera" conectada al SoC de administración. El Soc de gestión reserva el bloque de memoria en 0x26000000 para el módulo de limpieza. El módulo de limpieza intercambia datos con el SoC de gestión a través de una interfaz que utiliza datos de registro SPI de todo el byte. Una pequeña máquina de estados lee cuatro direcciones de horquilla contiguas y un decodificador de direcciones determina el registro SPI correspondiente. La máquina de estado detiene el SoC hasta que se hayan manejado los cuatro bytes antes de devolver la señal de reconocimiento.

El área de gestión es un módulo directo implementado como un repositorio independiente. Por lo general, incluye un SoC basado en RISC-V que incluye varios periféricos como temporizadores, uart y gpio. El área de gestión ejecuta firmware que se puede utilizar para:

El área de gestión implementa SRAM para el SoC de gestión.

La creación de instancias predeterminada para el núcleo de administración se puede encontrar aquí. Consulte la documentación del núcleo de gestión para obtener más detalles.

Este es el espacio del usuario. Tiene un área de silicio limitada 2.92mm x 3.52mm así como un número fijo de pads de E/S 38 y pads de alimentación 4 .

El espacio de usuario tiene acceso a las siguientes utilidades proporcionadas por el SoC de gestión:

38 puertos E/S128 sondas analizadoras lógicas Su área es el espacio de usuario completo, así que siéntase libre de agregar su proyecto allí o crear una macro diferente y reforzarla por separado, luego insértela en user_project_wrapper para proyectos digitales o insértela en user_project_analog_wrapper para proyectos analógicos.

Si está creando un proyecto digital para el espacio del usuario, consulte un proyecto de muestra en caravel_user_project.

Si va a utilizar OpenLANE para reforzar su diseño, siga las instrucciones de este archivo README.

Los proyectos de usuarios digitales deben cumplir los siguientes requisitos:

user_project_wrapperuser_project_wrapper se adhiere al orden de pines definido en Orden de pines de Digital Wrapper.user_project_wrapper se adhiere a las configuraciones de diseño fijas en Configuración fija de Digital Wrapper.Si está creando un proyecto analógico para el espacio de usuario, consulte un proyecto de muestra en caravel_user_project_analog.

Los proyectos de usuarios analógicos deben cumplir los siguientes requisitos:

user_analog_project_wrapperuser_analog_project_wrapper utiliza el contenedor analógico vacío.user_analog_project_wrapper se adhiere al mismo orden de pines y ubicación del contenedor analógico vacío. Asegúrese de ejecutar make compress antes de enviar algo a su repositorio. Evite tener 2 versiones de gds/user_project_wrapper.gds una comprimida y la otra no comprimida.

Para obtener información sobre herramientas y control de versiones, consulte tool-versioning.rst.

gds/ : incluye todos los archivos gds utilizados o producidos a partir del proyecto.def : incluye todos los archivos def utilizados o producidos a partir del proyecto.lef/ : incluye todos los archivos lef utilizados o producidos a partir del proyecto.mag/ : incluye todos los archivos mag utilizados o producidos a partir del proyecto.maglef : incluye todos los archivos maglef utilizados o producidos a partir del proyecto.spi/lvs/ : incluye todos los archivos de especias utilizados o producidos a partir del proyecto.verilog/dv : incluye todos los bancos de pruebas de simulación y cómo ejecutarlos.verilog/gl/ : incluye todas las netlists sintetizadas/elaboradas.verilog/rtl : incluye todos los archivos fuente y RTL de Verilog.openlane/<macro>/ : incluye todos los archivos de configuración utilizados para ejecutar openlane en su proyecto.info.yaml : incluye toda la información requerida en este ejemplo. Asegúrese de apuntar a una lista de redes de carabela elaborada, así como a una lista de redes de nivel de puerta sintetizada para user_project_wrapper.NOTA:

Si está utilizando openlane para reforzar su diseño, los directoriosverilog/gldef/lef/gds/magmaglefdeberían completarse automáticamente con openlane.

Consulte mpw-one-final para conocer la carabela utilizada para la cinta de mpw-one.

>make ship .