Le moteur de déchargement UDP est un VHDL IP utilisé pour la programmation matérielle FPGA.

Cette IP est un accélérateur de pile UDP-IP et est capable d'envoyer et de recevoir des données via une liaison Ethernet. Cette pile est hautement configurable pour être utilisée avec des débits Ethernet allant jusqu'à 40 Gb/s grâce à sa taille de bus configurable. De plus il est modulaire. Il implémente différents protocoles et outils de tests intégrés pouvant être désactivés afin d'économiser des ressources.

Cette IP est basée sur des Building Blocks suivant la stratégie de Thales en ingénierie. Ils remplissent des fonctions de base et permettent d’être indépendants de la plateforme/cible. Aucune primitive de fabricant n'est utilisée sur cette conception, toutes sont déduites.

Tables des matières

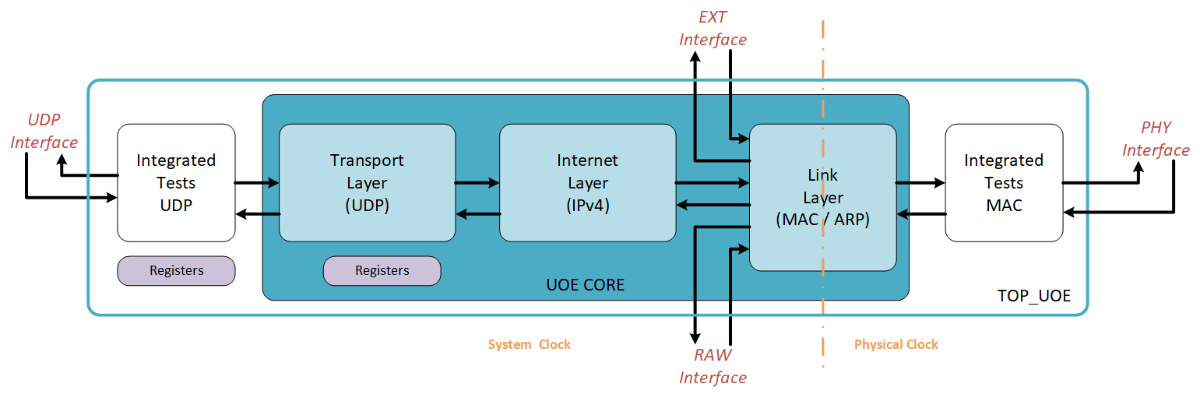

Cette figure décrit l'architecture interne de l'IP. L'entité principale est le module uoe_core . Il a été encapsulé dans un wrapper top_uoe qui instancie en outre certaines fonctions de tests intégrées.

Partie fonctionnelle

Pièce de test intégrée (en option)

La documentation complète de la stack est disponible sur le guide d'architecture.

Taille de bus configurable

Gérer les protocoles suivants

Protocole de résolution d'adresse (ARP)

Protocole de message de contrôle Internet (ICMP)

Prendre en compte les buffers sur l'interface MAC et le croisement de domaines d'horloge

Option de filtrage pour le trafic entrant

Utilisation du bus standard

Le design a été synthétisé et implémenté avec différents paramètres génériques et pour plusieurs cibles hors contexte. Les résultats sont disponibles sur la page Performances.

Ce dépôt intègre l'exemple de conception suivant :

À venir ...

Si vous souhaitez contribuer à ce projet, commencez par lire les directives de contribution.