NOTE:

La documentation de ce projet est en cours de mise à jour pour refléter les changements apportés à la nouvelle version repensée de Caravel.

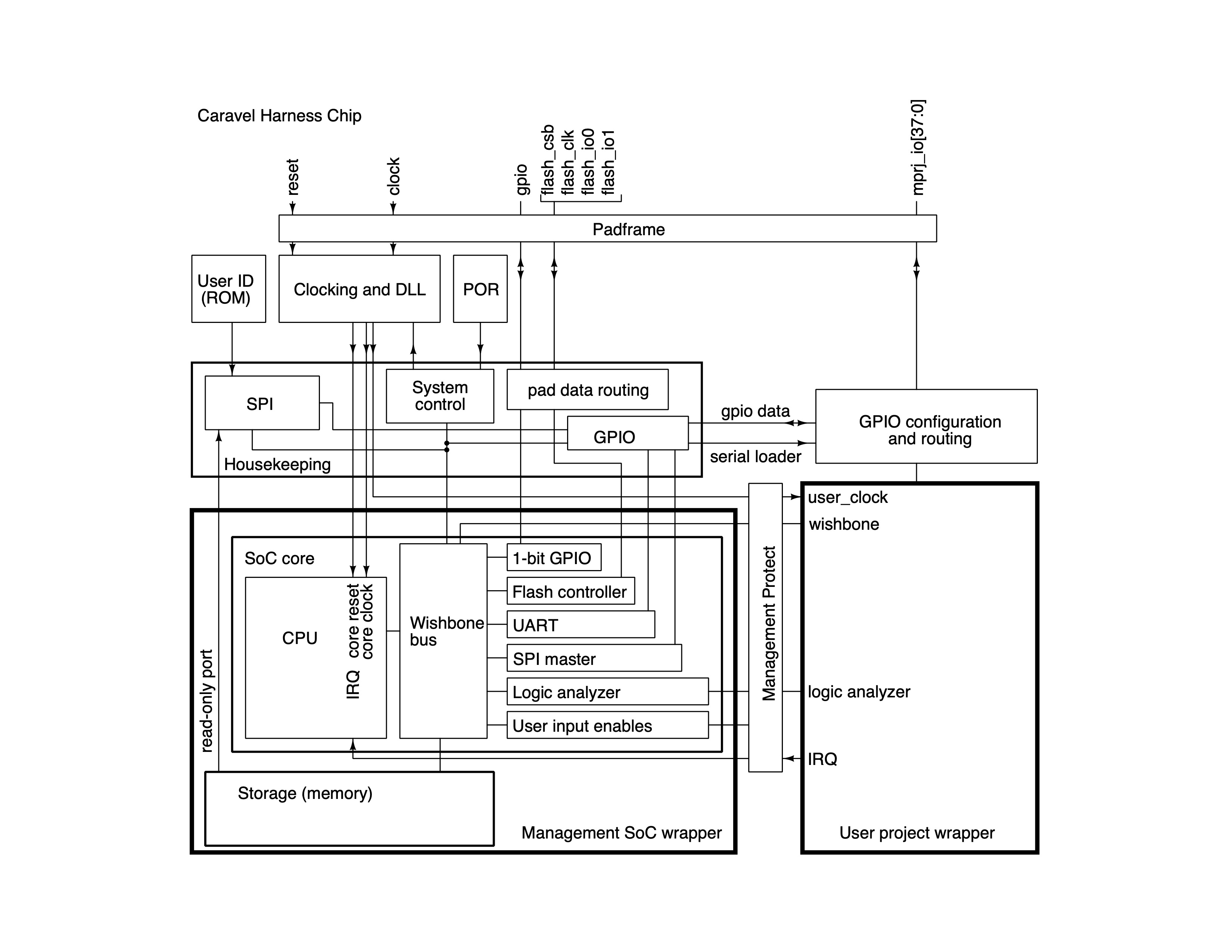

Caravel est un modèle de SoC pour les navettes Efabless Open MPW et chipIgnite basé sur le nœud Sky130 de SkyWater Technologies. L'architecture SoC actuelle est indiquée ci-dessous.

La fiche technique et la documentation détaillée existent ici

Caravel est composé du cadre de harnais et de deux enveloppes pour les modules intégrés pour la zone de gestion et la zone de projet utilisateur .

Le harnais lui-même contient le module de synchronisation, la DLL, l'ID utilisateur, le contrôle SPI, POR et GPIO.

La gestion GPIO est passée du SoC de gestion à SPI. SPI obtient une interface en forme de triangle ; le SoC de gestion communique avec le SPI via le wishbone, et non en prenant en charge l'interface SPI à 4 broches.

Un nouveau bloc comme l'ID a le mode à la mise sous tension pour chaque GPIO. Peut être configuré avec un fichier texte. Les broches SPI sont fixes pour fonctionner au démarrage.

A la mise sous tension, le SPI configure automatiquement le GPIO. Le chargement manuel est possible à la fois depuis le SPI et depuis le bus wishbone.

Toutes les fonctions au sein du harnais mais en dehors du SoC de gestion sont incorporées dans un grand module appelé « housekeeping ». Cela comprend un certain nombre de registres pour toutes les fonctions incluses, avec une interface SPI « porte d'entrée » connectée au padframe via les broches GPIO 1 à 4, et une interface wishbone « porte arrière » connectée au SoC de gestion. Le Soc de gestion réserve le bloc mémoire à 0x26000000 pour le module housekeeping. Le module de gestion interne échange des données avec le SoC de gestion via une interface qui utilise les données du registre SPI au niveau de l'octet. Une petite machine à états lit quatre adresses de wishbone contiguës et un décodeur d'adresses détermine le registre SPI correspondant. La machine à états bloque le SoC jusqu'à ce que les quatre octets aient été traités avant de renvoyer le signal d'accusé de réception.

La zone de gestion est un module d'insertion implémenté en tant que dépôt distinct. Il comprend généralement un SoC basé sur RISC-V qui comprend un certain nombre de périphériques tels que des minuteries, uart et gpio. La zone de gestion exécute un micrologiciel qui peut être utilisé pour :

La zone de gestion implémente SRAM pour le SoC de gestion.

L'instanciation par défaut du noyau de gestion peut être trouvée ici . Voir la documentation du noyau de gestion pour plus de détails.

C'est l'espace utilisateur. Il possède une zone de silicium limitée 2.92mm x 3.52mm ainsi qu'un nombre fixe de plages d'E/S 38 et de plages d'alimentation 4 .

L'espace utilisateur a accès aux utilitaires suivants fournis par le SoC de gestion :

38 ports E/S128 sondes analyseurs logiques Votre zone est l'espace utilisateur complet, alors n'hésitez pas à y ajouter votre projet ou à créer une macro différente et à la renforcer séparément, puis à l'insérer dans le user_project_wrapper pour les projets numériques ou à l'insérer dans user_project_analog_wrapper pour les projets analogiques.

Si vous créez un projet numérique pour l'espace utilisateur, consultez un exemple de projet sur caravel_user_project.

Si vous comptez utiliser OpenLANE pour renforcer votre conception, suivez les instructions de ce README.

Les projets d'utilisateurs numériques doivent respecter les exigences suivantes :

user_project_wrapperuser_project_wrapper adhère à l’ordre des broches défini dans Digital Wrapper Pin Order.user_project_wrapper adhère aux configurations de conception fixes de Digital Wrapper Fixed Configuration.Si vous créez un projet analogique pour l'espace utilisateur, consultez un exemple de projet sur caravel_user_project_analog.

Les projets d'utilisateurs analogiques doivent respecter les exigences suivantes :

user_analog_project_wrapperuser_analog_project_wrapper utilise le wrapper analogique vide.user_analog_project_wrapper adhère au même ordre de broches et au même emplacement du wrapper analogique vide. Veuillez vous assurer d'exécuter make compress avant de valider quoi que ce soit dans votre référentiel. Évitez d'avoir 2 versions de gds/user_project_wrapper.gds l'une compressée et l'autre non compressée.

Pour plus d’informations sur les outils et la gestion des versions, veuillez vous référer à tool-versioning.rst.

gds/ : inclut tous les fichiers gds utilisés ou produits à partir du projet.def : inclut tous les fichiers def utilisés ou produits à partir du projet.lef/ : inclut tous les fichiers lef utilisés ou produits à partir du projet.mag/ : inclut tous les fichiers mag utilisés ou produits à partir du projet.maglef : inclut tous les fichiers maglef utilisés ou produits à partir du projet.spi/lvs/ : inclut tous les fichiers spice utilisés ou produits à partir du projet.verilog/dv : comprend tous les bancs de tests de simulation et comment les exécuter.verilog/gl/ : inclut toutes les netlists synthétisées/élaborées.verilog/rtl : inclut tous les RTL et fichiers sources Verilog.openlane/<macro>/ : inclut tous les fichiers de configuration utilisés pour exécuter openlane sur votre projet.info.yaml : inclut toutes les informations requises dans cet exemple. Veuillez vous assurer que vous pointez vers une netlist de caravel élaborée ainsi qu'une netlist synthétisée au niveau de la porte pour le user_project_wrapper.NOTE:

Si vous utilisez openlane pour renforcer votre conception, les répertoiresverilog/gldef/lef/gds/magmaglefdoivent être automatiquement renseignés par openlane.

Vérifiez mpw-one-final pour la caravelle utilisée pour la sortie mpw-one.

>make ship n'est plus nécessaire.