***このプロジェクトは進行中の未完成の作業です。現在バグがあり、すべての機能がテストされていません。

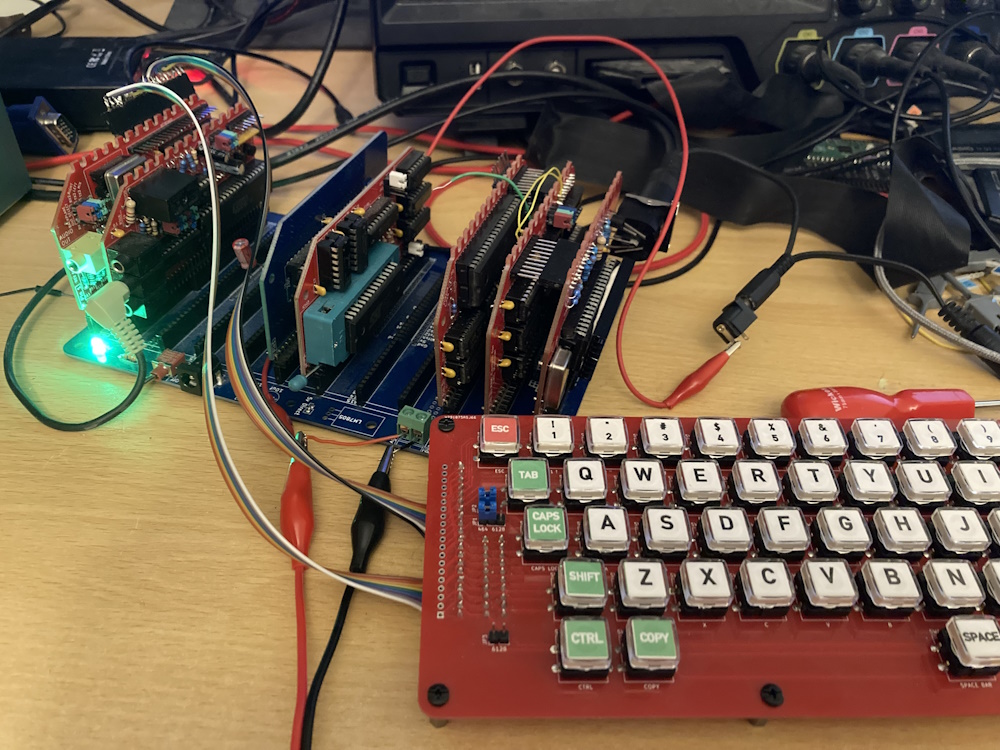

現在のモジュールは、わずかに変更された RC2014 Pro バックプレーンに適合するように設計されています。以下のテキストでは、プロジェクトの現在のステータス、プロジェクトを実行するために必要な回避策、および基本的なビルドの詳細について説明します。プロジェクトは進行中であるため、このドキュメントは意図的に簡潔になります。

このプロジェクトでは、ピン ヘッダー/ソケットを使用してサブシステム (ビデオ RAM サブシステムと IO サウンド サブシステム) 内のモジュールを接続します。これには、通常よりも長いピン ヘッダーが必要になります。

これは、わずかに変更された RC2014 Pro バックプレーンです。 CPC モジュラーは、ビデオ RAM サブシステムとローカル データ バス用の IO サウンド サブシステムの両方で D8 ~ D15 ラインを使用します。したがって:

これらのセクション間の D8 ~ D15 回線を切断する必要があります。

RC2014「Z80 CPUモジュール」を少し改造したものです。修正:

ボード上の抵抗を別の値に交換する必要があります。 2.2kΩでうまく動作するはずです。

このボードには 512Kb NORFLASH が含まれています。これには、フラッシュをその場で焼き付けることができる回路が含まれています (未テスト)。構成:

LK4 のピン 2 と LK5 のピン 2 をブリッジするジャンパを取り付ける必要があります。

フラッシュ書き込みを有効にするには、リンク LK1、LK2、および LK3 をインストールします。それ以外の場合は開いたままにしてください。

フラッシュへの書き込みに関するメモ (回路図ファイルから抜粋) は次のとおりです。

!!!標準の CPC システムではメモリ書き込みを無効にする方法はありません。したがって、WRITE_EN がアクティブなときに ROM に対して行うメモリ書き込みはすべて、RAM にも書き込まれます。

ただし、ROM はあらゆるメモリ バンクにマップされるため、ある程度の柔軟性が追加されます。また、書き込みは有効ですが、ROM からの読み取りは無効になることに注意してください。これは、ROM がアクティブな間、ROM の「下」にある RAM から読み取ることができることを意味します。

私が推奨するプログラミング手順は、ビデオ RAM アドレスを使用して ROM に書き込むことですが、メモリ範囲に意味のあるデータが含まれていない場合は、バンク 1 (&4000 ~ &7fff) のアドレスを使用して ROM に書き込むこともできます。 (書き込まれるデータがすでにこのアドレス範囲内にある場合、プログラマは単純にデータを読み取って (RAM)、同じアドレスに書き込む (ROM) ことができます。ただし、ROM に送信されるコマンドには注意が必要です。データは引き続きその下に破棄されます)。

プログラムするアドレスの RAM バイトを読み取ります。

ROMの書き込み許可をONにする

必要なデータをROMに書き込みます。

ROMの書き込み許可をオフにする

元のデータをROMに書き戻します。

ROM (NORFLASH) は、ファームウェア ROM に加えて最大 31 個の ROM を保持できます。チップをプログラミングするとき、ファームウェアはスロット 31 (アドレス &7c000 から始まる) に挿入する必要があります。 BASIC (インストールされている場合) はスロット 0 (アドレス &00000) に挿入する必要があります。 ROM スロットは &4000 バイトごとに配置されています。つまり、&00000、&04000、&08000、&0C000、&10000 などです。

XGPro ソフトウェアを使用して ROM を書き込む場合:

Select IC を使用して、使用する IC (SST39FS040) を選択します。

ツールバーの「ロード」ボタンをクリックします。

ロードするファイルを選択します。

ファイル形式: バイナリ (.ROM ファイルの場合)

リージョンへ: デフォルト

ロードモード: 通常

ファイル開始アドレスから: 0000

To Buffer Start Addr: ROM スロットの開始アドレス (ファームウェアの場合は &7C000、BASIC の場合は &00000)

ファイルのロード時にバッファをクリア: 「デフォルトでバッファをクリア」オプションを使用すると、以前にロードされたデータが上書きされます。 XGPro にロードされる最初の ROM にこれを使用します (ROM 全体が初期化されます)。他のすべての ROM については、「無効」を選択します (選択したスロットにのみデータがロードされます)。

「OK」をクリックし、ファイルが正しいアドレスにロードされ、上書きされていないことを確認します。

「PROG」(ツールバー)をクリックします。

「プログラム」をクリックします。

このボードにはゲート アレイとビデオ出力が収容されています。

JP901 では、DISPEN 信号と HSYNC 信号が、RAM コントロール ボード上の同等のヘッダーの信号と比較して交換されます。これは、RAM コントロール ボードで修正するのが最適です (下記を参照)。

ビデオ出力回路は CPC464 のものですが、どういうわけか CPC6128 の部品値を使用して、6128 のコンデンサを差し引いています。これはおそらく大きな違いはありません。

私のテストでは、Amstrads で通常使用しているものと同じ SCART to HDMI アダプターを使用していますが、ここでは白黒画像が表示されるか、画像がまったく表示されません。これは、ケーブルで使用されている PSU とアダプターの間の問題であると思われます。これは、CPC モジュラー ボードからケーブルに 5V 電力を供給することで修正できます。

このボードには、40007 と 40010 ゲート アレイの両方のフットプリントが含まれています (40008 も機能するはずです)。フットプリントはスペースを節約するために重なり合います。 2 列のピンを分離し、それらの間のウェビングを取り外すことで、両方のソケットを含めることができるはずですが、フットプリントが少し近すぎてこれを簡単に行うことができません。

DINソケット用のフットプリントの穴が少し小さすぎます。

このボードには、ビデオ データ バスと CPU データ バス間のリンクが収容され、信号が SRAM メモリに適したものとなるように信号が送信され、64k を超えるメモリ (未テスト) に必要なオプション コンポーネントが収容されます。

/RAMOEを駆動する回路が間違っています。それを修正するには:

U192 ピン 1 と 13 の間の配線をカットします。

U192 ピン 11 と U193 ピン 1 の間の配線をカットします。

U192 ピン 1 と U195 ピン 9 の間にワイヤを取り付けます

U195 ピン 8 と U193 ピン 1 の間にワイヤを取り付けます。

ビデオ ボードについて説明したように、DISPEN ピンと HSYNC ピンはボード間のコネクタ上で交換されます。これを修正するには:

J1 ピン 2 と J2 ピン 2 の間の配線をカットします。

J1 ピン 3 と J2 ピン 3 の間の配線をカットします。

J1 ピン 2 と J2 ピン 3 の間にワイヤを取り付けます。

J1 ピン 3 と J2 ピン 2 の間にワイヤを取り付けます

64k 以下の RAM を使用するには、リンク LK5、LK6、および LK7 をインストールします。その場合は、IC118 と U194 を挿入しないでください。

64k を超える RAM を使用するには、LK5、LK6、LK7 を開いたままにし、IC118 と U194 をインストールします。 IC118 は標準の Amstrad HAL/PAL です。

/RAMOE を駆動する正しい回路は次のとおりです。

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

テキスト形式: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD は U195 ピン 8 から供給できます。

このボードには 6845 CRTC、アドレス マルチプレクサ、および 512Kb SRAM が搭載されています。ここには問題はなく、構成は必要ありません。

必要に応じて、CURSOR および LPEN のヘッダーをインストールできます。おそらくそうではありません。

このボードには 8255 PIO とテープ インターフェイスが搭載されています。 I/O アドレスを構成可能にするために、はんだリンクとジャンパーが取り付けられています。

このボードは、IO ボードをその「上/前」に取り付けることができるように設計されていますが、リレーの高さがそれを可能にするほどではありません。したがって、J902 をボードの背面に取り付けることをお勧めします (これはサウンド ボードへのコネクタです)。

ボードの背面で、アドレス ピンのすぐ上のはんだリンクを見つけます。各リンクでは、「高」アドレス パッド (A7(原文どおり) ~ A15 のラベルが付いている) を中央パッドにはんだ付けする必要があります。 「低」アドレス パッド (A0..A7) をセンター パッドに接続してはなりません。

ボードの前面で、U1 と D302 の間にあるリンクを見つけます。 A3 というラベルのリンクの「ロー」リンク (センター ピンへ) をジャンパし、その他 (A2、A4、A5、A6、A7) のリンク (センター ピンへ) のハイ リンクをジャンパする必要があります。

C315 と J901 の間にあるリンクを見つけます。どの信号がジャック ソケットに送信され、どの信号がバックプレーンに送信されるかを設定します。推奨される設定は次のとおりです。

INT (ernal) と TO、TI、/MO (テープアウト、テープイン、モーター) の中間ピンの間にリンクを取り付けます。

/EXP リンクは開いたままにしておきます。

J901 を使用すると、さまざまな 8255 入力信号にアクセスできます。デフォルトでは、これらの行にはすべてプルアップがあり、無視できます。

RG0、RG1、RG2は地域設定です。

VHz はビデオ出力の 50Hz/60Hz 設定です。

/EXP は /EXP 信号です。

PBSY はプリンタービジー信号です。 CPC モジュラーにはパラレル ポートが含まれていません。必要に応じて、この信号を拡張に使用できます。

J1、J2、J3 はテープ I/O ジャックです。 J3 (モーター) は 2.5 mm ジャック ソケットである必要がありますが、設置面積は 3.5 mm ソケット用です。

このボードには、AY-3-8910 サウンド ジェネレーターと関連出力、さらにキーボードとジョイスティック コネクタが収容されています。

IO ボードについて説明したように、ボード間コネクタ (J902) は、シルクスクリーンに示されているように背面ではなく、このボードの上部に取り付ける必要があります。

このボードには、AY のクロック入力にオンボード発振器を使用する機能があります。 CPC モジュラーの場合: X1 を省略し、JP3 の CLK2 端にジャンパーを取り付けます (バックプレーンを介して送信されるゲート アレイからのクロック信号を使用するようにボードを構成します)。

J103 (オーディオ出力ジャック) 上のジャンパにより、さまざまなオーディオ信号をさまざまなバックプレーン ピンに送信できます。ほとんどの場合、これらは開いたままにしておくことができます。一部の設定は、IO ボードのバックプレーンを介してルーティングされるテープ信号と競合する可能性があることに注意してください。

オーディオ ジャックが取り付けられている場合、LEFT 信号と RIGHT 信号はバックプレーンに送信されません (送信するように構成されている場合 - 前の項目を参照)。ただし、オーディオ MIX は引き続き送信されます (そのように設定されている場合)。

CP2はキーボードコネクタです。これは、オリジナルの Amstrad CPC464 (PCB キーボード) と同じピン配置を使用します。

J102はジョイスティックコネクタです。ここのコネクタは少し「内側」に取り付けられすぎており、次のソケットの PCB をショートさせる可能性があります。

ハル/パル:

オリジナルのコード: https://www.cpcwiki.eu/index.php/PAL16L8

WiP の置き換え: https://github.com/Bread80/GreenHAL

WiP の置き換え: https://www.cpcwiki.eu/forum/index.php?msg=231084

ゲートアレイ:

WiP FPGA ベースの置き換え: https://github.com/codedchip/AMSGateArray

ROM イメージ: https://www.cpcwiki.eu/index.php/ROM_List

ライセンス: CERN-OHL-P

著作権©マイク・サットン、2023

ウェブサイト:https://bread80.com

ソーシャルメディア(マストドン):https://mstdn.social/@bread80

ここを越えて役に立つものは何もありません。しかし、ここまでやってきたのなら、おそらくそのまま進み続けるでしょう。

TX/RX=サウンド (左、右) **ジャンパあり (オプション) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC (ビデオから IO) USR4=

/WAIT=READY (すでにそうなっています!) CLOCK2=/CPU_ADDR (RAM ボード; サウンド用 1MHz クロック) RX2=テープ イン **ジャンパー (オプション) TX2=テープ アウト **ジャンパー (オプション) USR5=RAMDIS MOVED USR6=/ RAMRD MOVED USR7=モーター **ジャンパあり (オプション)

D8-D15=ビデオバス

D8-D15=IO バス ???制御信号???

位置 = 基本的な RC2014 ヘッダー ピンの中心から 45.72 mm 上の穴の一番上の列、左端のピン = A9 と A8 の間の中点 ピン 1 を右へ 1 GND 2 HSYNC (インチ) 3 DISPEN (インチ) 4 GND 5 /RAS (出力) 6 /CAS (出力) 7 /MWE (出力) 8 /CCLK (出力) 9 /244EN (出力) 10グランド

位置 = 拡張ヘッダー ピンの中心から 43.18 mm 上の穴の最上列、左端のピン = D2 ピンと D3 ピンの間の中間点、ピン 1 は左側、最上列はすべてグランドです。 1=GND 2=HSYNC (入力) 3=DISPEN (入力) 4=/CCLK (出力) 5=/XCPU_ADDR (出力) 6=/RAMCS (出力) 7=GND 8=/RAMOE (出力) 9=GND 10 =/RAMWE (出力) 11=RAMA14 (出力) 12=RAMA15 (出力) 13=RAMA16 (出力) 14=RAMA17 (出力) 15=GND 16=RAMA18 (出力)

1=GND 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=GND

Amstrad/MX4 ピン配置

GND サウンド Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK READY Y Y BRST RSET Y?え?え?え?え? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS カーソル Y LPEN Y EXP Y Y GND CLK4 Y Y

追加 (ビデオ RAM): RD7..RD0 Y Y Y RAS Y Y CAS Y Y MWE Y Y 244EN Y Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y (24 行)

追加 (ビデオ RAM および IO サウンド): CPU_ADDR(1MHz) Y Y Y VSYNC Y Y Y (2 行)

追加 (IO-Sound): PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y LEFT Y RIGHT Y (20 行)

ディスク:内部的に約14行必要

ビデオ/RAM: 50 + 24 + 2 = 76 ライン!合計。不要なものが少ない: 合計 69 (70 プラス予備 1!) IO/サウンド: 50 + 20 + 2 = 合計 72 ライン。不要なものが少ない: 合計 50 (予備の数枚を含む) ディスク: 50 + 14 = 合計 64 ライン

注: 76 ピン エッジ コネクタ: 基板幅 = 99.06mm

ボード: MX4 セクション: CPU ROM スペア RC2014 エッジ コネクタ

ビデオセクション(ゲートアレイ):ビデオRAM RAMコントロール

ビデオセクション (RP2040): ビデオ信号 RAM トランシーバー

ディスクセクション: コントローラーコネクター/バッファー

IOサウンドセクション: PPI AY Tape オーディオアンプ/ミキサー