注記:

このプロジェクトのドキュメントは、Caravel の新しい再設計バージョンの変更を反映するために更新されています。

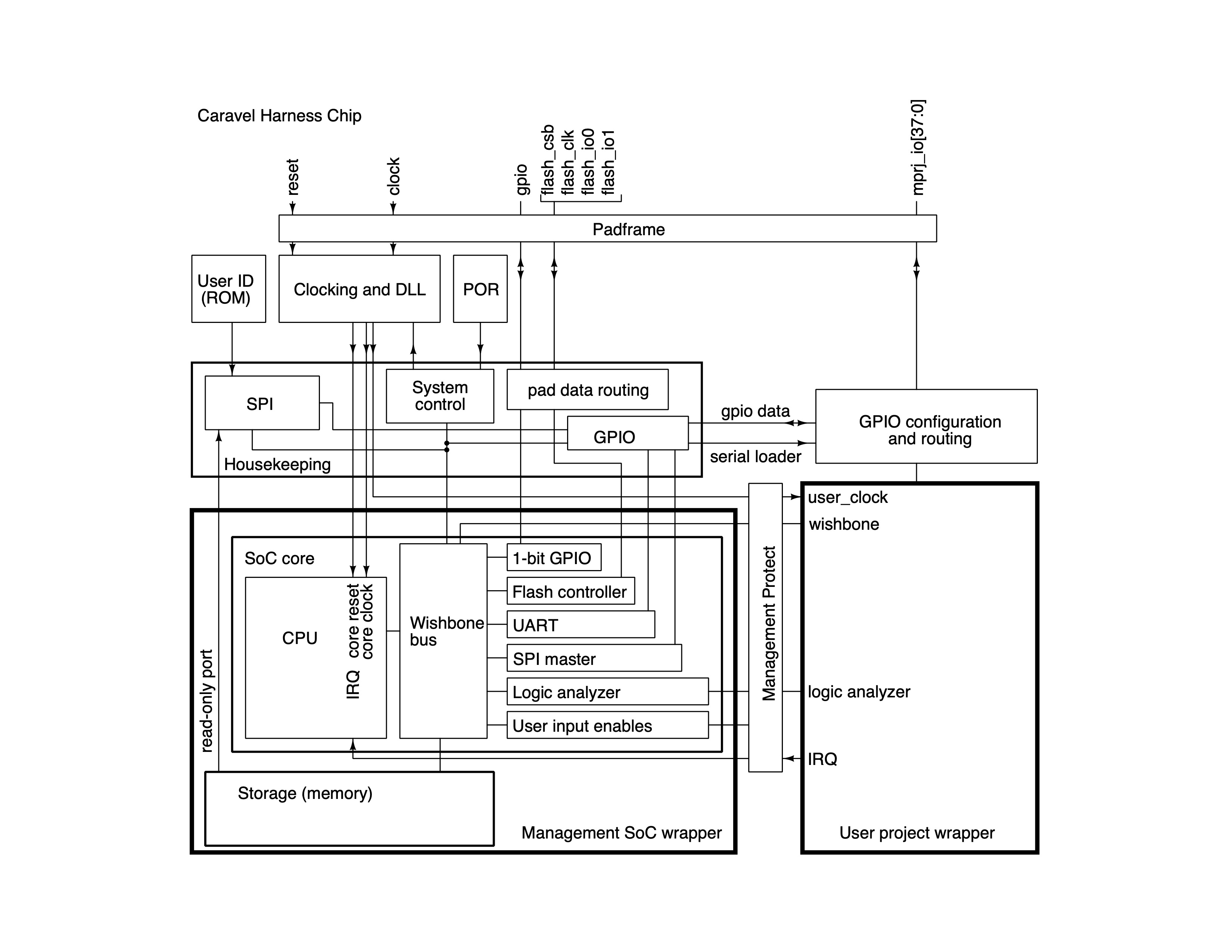

Caravel は、SkyWater Technologies の Sky130 ノードに基づく Efabless Open MPW および ChipIgnite シャトル用のテンプレート SoC です。現在の SoC アーキテクチャを以下に示します。

データシートと詳細なドキュメントはここにあります

Caravel は、ハーネス フレームと、管理領域およびユーザー プロジェクト領域のドロップイン モジュール用の 2 つのラッパーで構成されます。

ハーネス自体には、クロッキング モジュール、DLL、ユーザー ID、ハウスキーピング SPI、POR、および GPIO コントロールが含まれています。

GPIO 処理は管理 SoC から SPI に移動されました。 SPI はウィッシュボーン インターフェイスを取得します。管理 SoC は、4 ピン SPI インターフェイスを引き継ぐのではなく、ウィッシュボーンを通じて SPI と通信します。

ID のような新しいブロックには、各 GPIO の電源投入時のモードがあります。テキストファイルで設定可能です。 SPI ピンは起動時の動作用に固定されています。

電源投入時に、SPI は GPIO を自動的に構成します。 SPI とウィッシュボーン バスの両方から手動ロードが可能です。

ハーネス内を除く管理 SoC の外にあるすべての機能は、「ハウスキーピング」と呼ばれる 1 つの大きなモジュールに組み込まれています。これには、含まれるすべての機能用の多数のレジスタが含まれており、GPIO ピン 1 ~ 4 を介してパッドフレームに接続された「フロント ドア」SPI インターフェイスと、管理 SoC に接続された「バック ドア」ウィッシュボーン インターフェイスを備えています。管理 Soc は、ハウスキーピング モジュール用に 0x26000000 のメモリ ブロックを予約します。ハウスキーピング モジュールは、バイト幅の SPI レジスタ データを使用するインターフェイスを介して管理 SoC とデータを交換します。小さなステート マシンが 4 つの連続するウィッシュボーン アドレスを読み取り、アドレス デコーダが対応する SPI レジスタを決定します。ステート マシンは、4 バイトすべてが処理されるまで SoC をストールさせてから、アクノリッジ信号を返します。

管理領域は、別のリポジトリとして実装されるドロップイン モジュールです。通常、タイマー、UART、GPIO などの多数の周辺機器を含む RISC-V ベースの SoC が含まれています。管理領域では、次の目的で使用できるファームウェアが実行されます。

管理領域には管理 SoC 用の SRAM が実装されています。

管理コアのデフォルトのインスタンス化は、ここにあります。詳細については、管理コアのドキュメントを参照してください。

ここはユーザースペースです。それは、 2.92mm x 3.52mmの限られたシリコン領域と、固定数のI/Oパッド38および電源パッド4を有する。

ユーザー空間は、管理 SoC によって提供される次のユーティリティにアクセスできます。

38 IO ポート128ロジック アナライザ プローブあなたの領域は完全なユーザー空間なので、自由にそこにプロジェクトを追加するか、別のマクロを作成して個別に強化してから、デジタル プロジェクトの場合はuser_project_wrapperに挿入し、アナログ プロジェクトの場合はuser_project_analog_wrapperに挿入します。

ユーザー空間用のデジタル プロジェクトを構築している場合は、caravel_user_project でサンプル プロジェクトを確認してください。

OpenLANE を使用して設計を強化する場合は、この README の手順に従ってください。

デジタル ユーザー プロジェクトは、次の要件に従う必要があります。

user_project_wrapperですuser_project_wrapper 、Digital Wrapper Pin Order で定義されたピン順序に従います。user_project_wrapper 、Digital Wrapper の固定構成での固定設計構成に従います。ユーザー空間のアナログ プロジェクトを構築している場合は、caravel_user_project_analog でサンプル プロジェクトを確認してください。

アナログ ユーザー プロジェクトは、次の要件に従う必要があります。

user_analog_project_wrapperですuser_analog_project_wrapper空のアナログ ラッパーを使用します。user_analog_project_wrapper空のアナログ ラッパーと同じピンの順序と配置に従います。 リポジトリに何かをコミットする前に、必ずmake compress実行してください。圧縮されたバージョンと圧縮されていないバージョンのgds/user_project_wrapper.gdsを 2 つ存在させることは避けてください。

ツールとバージョン管理の詳細については、tool-versioning.rst を参照してください。

gds/ : プロジェクトで使用または生成されたすべての gds ファイルが含まれます。def : プロジェクトで使用または生成されたすべての def ファイルが含まれます。lef/ : プロジェクトで使用または生成されたすべての lef ファイルが含まれます。mag/ : プロジェクトで使用または生成されたすべての mag ファイルが含まれます。maglef : プロジェクトで使用または生成されたすべての Magref ファイルが含まれます。spi/lvs/ : プロジェクトで使用または生成されたすべてのスパイス ファイルが含まれます。verilog/dv : すべてのシミュレーション テスト ベンチとその実行方法が含まれています。verilog/gl/ : すべての合成/詳細化されたネットリストが含まれます。verilog/rtl : すべての Verilog RTL とソース ファイルが含まれます。openlane/<macro>/ : プロジェクトで openlane を実行するために使用されるすべての構成ファイルが含まれます。info.yaml : この例で必要なすべての情報が含まれています。 user_project_wrapper の合成されたゲート レベル ネットリストだけでなく、精緻化されたキャラベル ネットリストを指していることを確認してください。注記:

openlane を使用してデザインを強化している場合は、verilog/gldef/lef/gds/magmaglefディレクトリが openlane によって自動的に設定される必要があります。

mpw-one テープアウトに使用される caravel については、mpw-one-final を確認してください。

>make shipを実行する必要はなくなりました。