O UDP Offload Engine é um IP VHDL usado para programação de hardware FPGA.

Este IP é um acelerador de pilha UDP-IP e é capaz de enviar e receber dados através de link Ethernet. Esta pilha é altamente configurável para ser usada com taxas Ethernet de até 40 Gb/s graças ao seu tamanho de barramento configurável. Além disso, é modular. Implementa diversos protocolos e ferramentas de teste integradas que podem ser desativadas para economizar recursos.

Este IP é baseado em Building Blocks seguindo a Estratégia Thales em engenharia. Desempenham funções básicas e permitem ser independentes da plataforma/target. Nenhuma primitiva de fabricante é usada neste projeto, todas são inferidas.

Índices

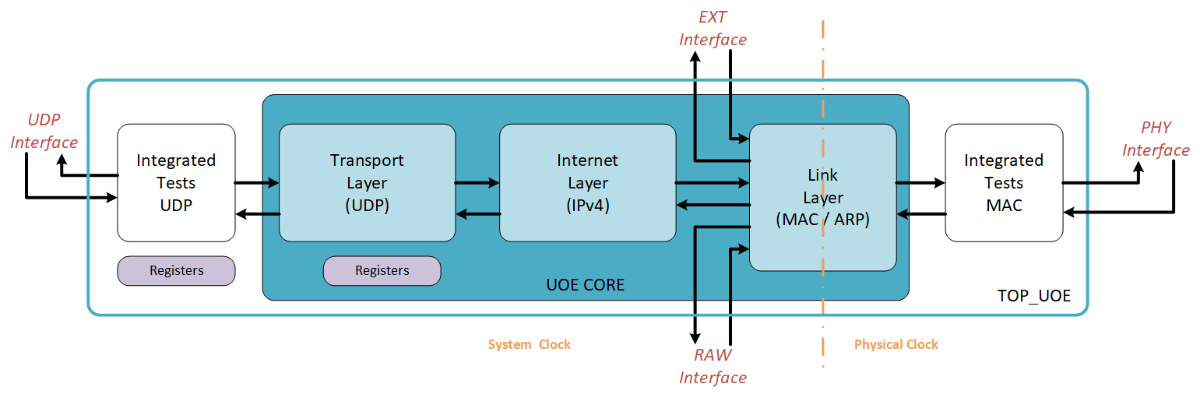

Esta figura descreve a arquitetura interna do IP. A entidade principal é o módulo uoe_core . Ele foi encapsulado em um wrapper top_uoe que adicionalmente instancia algumas funções de testes integradas.

Parte funcional

Parte de teste integrada (opcional)

A documentação completa da pilha está disponível no guia de arquitetura.

Tamanho do barramento configurável

Lidar com os seguintes protocolos

Protocolo de resolução de endereço (ARP)

Protocolo de mensagens de controle da Internet (ICMP)

Leve em consideração os buffers na interface MAC e o cruzamento do domínio do relógio

Opção de filtragem para tráfego de entrada

Uso de ônibus padrão

O design foi sintetizado e implementado com diferentes parâmetros genéricos e para diversos alvos fora de contexto. Os resultados estão disponíveis na página Desempenho.

Este repositório integra o seguinte exemplo de design:

Em breve ...

Se você estiver interessado em contribuir para este projeto, comece lendo as diretrizes de contribuição.