UDP Offload Engine — это IP VHDL, используемый для аппаратного программирования FPGA.

Этот IP-адрес представляет собой ускоритель стека UDP-IP и может отправлять и получать данные через канал Ethernet. Этот стек легко настраивается для использования со скоростью Ethernet до 40 Гбит/с благодаря настраиваемому размеру шины. Более того, он модульный. Он реализует различные протоколы и интегрированные инструменты тестирования, которые можно деактивировать в целях экономии ресурсов.

Этот IP основан на строительных блоках, соответствующих стратегии Thales в области инженерии. Они выполняют базовые функции и позволяют быть независимыми от платформы/цели. В этой конструкции не используются примитивы производителя, все они подразумеваются.

Оглавление

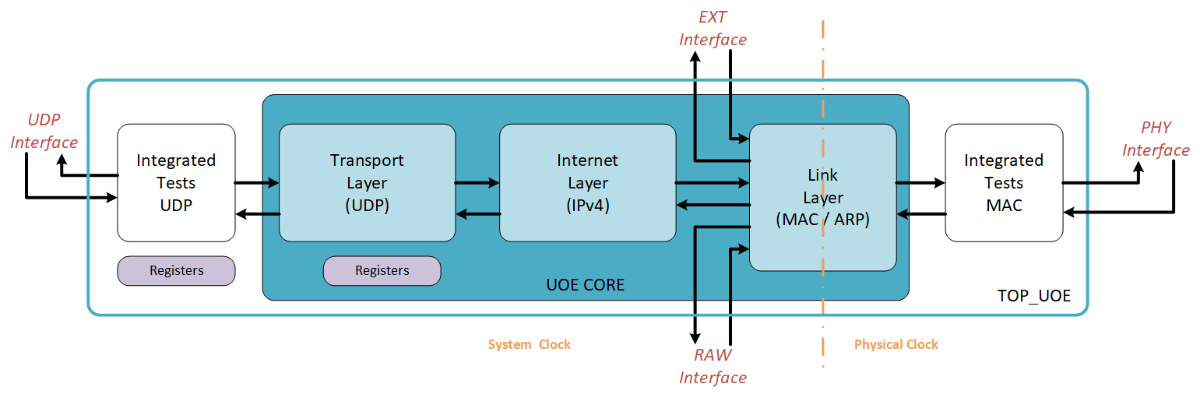

На этом рисунке описана внутренняя архитектура IP. Основной сущностью является модуль uoe_core . Он был инкапсулирован в верхнюю обертку top_uoe , которая дополнительно создает экземпляры некоторых встроенных функций тестирования.

Функциональная часть

Встроенная тестовая часть (дополнительно)

Полная документация стека доступна в руководстве по архитектуре.

Настраиваемый размер шины

Обработка следующих протоколов

Протокол разрешения адресов (ARP)

Протокол управляющих сообщений Интернета (ICMP)

Учитывайте буферы на интерфейсе MAC и пересечение тактовой области.

Возможность фильтрации входящего трафика

Использование стандартного автобуса

Проект был синтезирован и реализован с различными универсальными параметрами и для нескольких целей вне контекста. Результаты доступны на странице Производительность.

В этот репозиторий включен следующий пример дизайна:

Вскоре ...

Если вы заинтересованы в участии в этом проекте, начните с прочтения Руководства по участию.