ПРИМЕЧАНИЕ:

Документация по этому проекту обновляется, чтобы отразить изменения в новой переработанной версии Caravel.

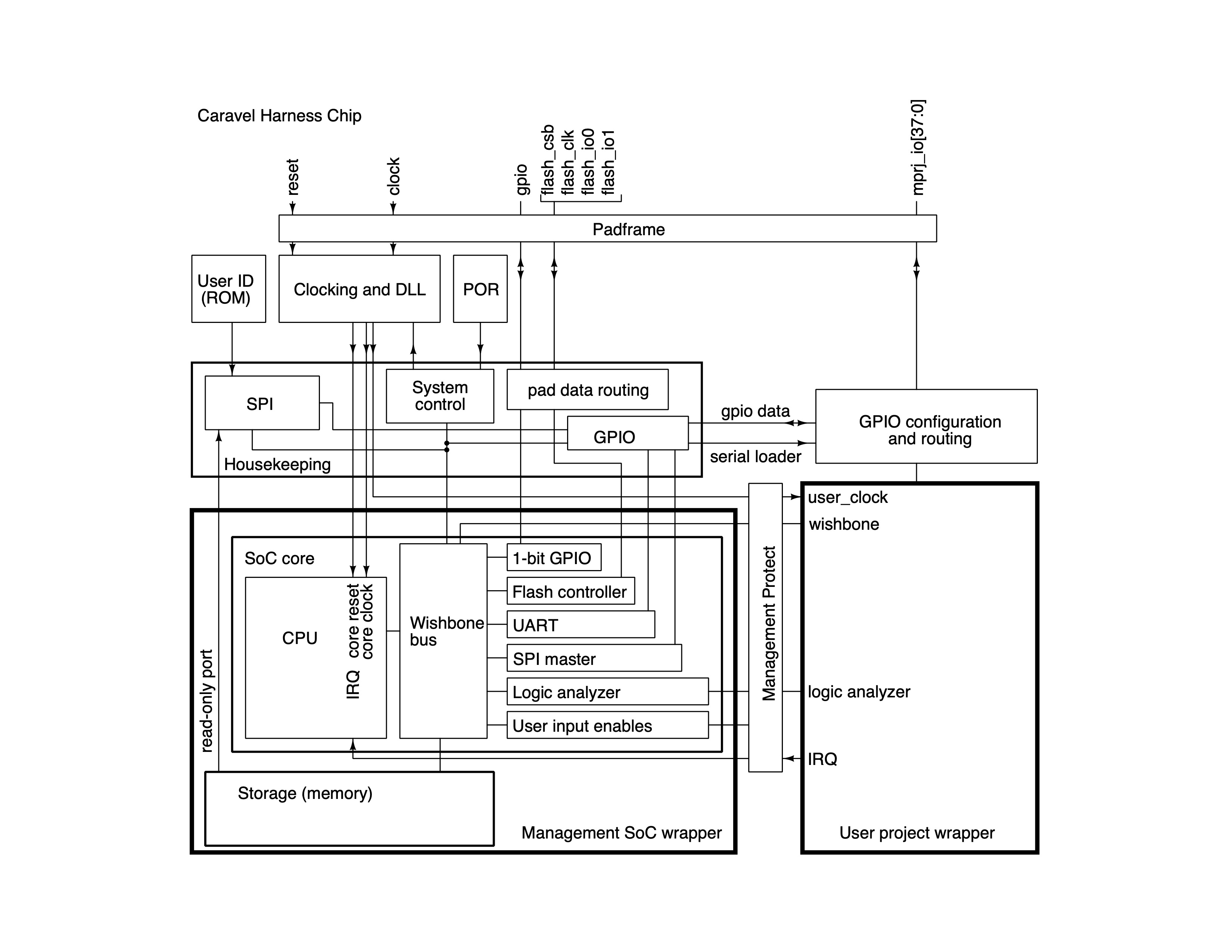

Caravel — это шаблон SoC для шаттлов Efabless Open MPW и ChipIgnite на базе узла Sky130 от SkyWater Technologies. Текущая архитектура SoC приведена ниже.

Техническое описание и подробная документация доступны здесь.

Caravel состоит из каркаса и двух оберток для вставных модулей для области управления и области пользовательских проектов .

Сама жгут содержит модуль синхронизации, DLL, идентификатор пользователя, служебный SPI, POR и управление GPIO.

Обработка GPIO перенесена из управления SoC в SPI. SPI получает поперечный интерфейс; SoC управления взаимодействует с SPI через рычаг, а не через 4-контактный интерфейс SPI.

Новый блок, такой как ID, имеет режим при включении питания для каждого GPIO. Можно настроить с помощью текстового файла. Выводы SPI фиксированы для работы при запуске.

При включении питания SPI автоматически настраивает GPIO. Ручная загрузка возможна как от SPI, так и от поперечной шины.

Все функции внутри системы, но за пределами SoC управления, объединены в один большой модуль, называемый «обслуживание». Сюда входит ряд регистров для всех включенных функций: интерфейс SPI «входной двери», подключенный к планшету через контакты GPIO с 1 по 4, и интерфейс поперечного рычага «черной двери», подключенный к SoC управления. Soc управления резервирует блок памяти по адресу 0x26000000 для модуля обслуживания. Модуль управления обменивается данными с SoC управления через интерфейс, который использует данные регистра SPI шириной в байт. Небольшой конечный автомат считывает четыре последовательных адреса поперечных рычагов, а декодер адреса определяет соответствующий регистр SPI. Конечный автомат останавливает работу SoC до тех пор, пока все четыре байта не будут обработаны, прежде чем вернуть сигнал подтверждения.

Область управления представляет собой встраиваемый модуль, реализованный в виде отдельного репозитория. Обычно он включает в себя SoC на базе RISC-V, который включает в себя ряд периферийных устройств, таких как таймеры, UART и gpio. В области управления работает встроенное ПО, которое можно использовать для:

Область управления реализует SRAM для SoC управления.

Экземпляр ядра управления по умолчанию можно найти здесь. Дополнительную информацию см. в документации ядра управления.

Это пространство пользователя. Он имеет ограниченную площадь кремния 2.92mm x 3.52mm а также фиксированное количество площадок ввода-вывода 38 и площадок питания 4 .

Пользовательское пространство имеет доступ к следующим утилитам, предоставляемым SoC управления:

38 портов ввода-вывода128 пробников логического анализатора Ваша область — это полное пространство пользователя, поэтому смело добавляйте туда свой проект или создайте другой макрос и закрепите его отдельно, а затем вставьте его в user_project_wrapper для цифровых проектов или вставьте в user_project_analog_wrapper для аналоговых проектов.

Если вы создаете цифровой проект для пользовательского пространства, проверьте образец проекта на сайте caravel_user_project.

Если вы будете использовать OpenLANE для усиления безопасности вашего проекта, следуйте инструкциям в этом README.

Цифровые пользовательские проекты должны соответствовать следующим требованиям:

user_project_wrapperuser_project_wrapper придерживается порядка выводов, определенного в разделе «Порядок выводов цифровой оболочки».user_project_wrapper придерживается фиксированных конфигураций дизайна в фиксированной конфигурации Digital Wrapper.Если вы создаете аналоговый проект для пользовательского пространства, проверьте пример проекта по адресу caravel_user_project_analog.

Аналоговые пользовательские проекты должны соответствовать следующим требованиям:

user_analog_project_wrapperuser_analog_project_wrapper использует пустую аналоговую оболочку.user_analog_project_wrapper придерживается того же порядка выводов и размещения, что и пустая аналоговая оболочка. Обязательно запустите make compress перед тем, как что-либо фиксировать в репозитории. Не используйте две версии gds/user_project_wrapper.gds : одну сжатую, а другую несжатую.

Информацию об инструментах и управлении версиями см. на сайтеtool-versioning.rst.

gds/ : включает все файлы gds, используемые или созданные в проекте.def : включает все файлы def, используемые или созданные в проекте.lef/ : включает все файлы lef, использованные или созданные в проекте.mag/ : включает все файлы mag, используемые или созданные в проекте.maglef : включает все файлы maglef, используемые или созданные в проекте.spi/lvs/ : включает все файлы специй, используемые или созданные в проекте.verilog/dv : содержит все стенды для моделирования и способы их запуска.verilog/gl/ : включает все синтезированные/разработанные списки соединений.verilog/rtl : включает все RTL Verilog и исходные файлы.openlane/<macro>/ : включает все файлы конфигурации, используемые для запуска openlane в вашем проекте.info.yaml : включает всю информацию, необходимую в этом примере. Пожалуйста, убедитесь, что вы указываете на тщательно продуманный список соединений каравеллы, а также синтезированный список соединений уровня шлюза для user_project_wrapper.ПРИМЕЧАНИЕ:

Если вы используете openlane для усиления безопасности вашего проекта, каталогиverilog/gldef/lef/gds/magmaglefдолжны быть автоматически заполнены openlane.

Проверьте mpw-one-final на предмет каравеллы, использованной для записи mpw-one.

>make ship больше не требуется.