يطبق هذا الريبو مجموعة من المكونات المتعلقة بشبكة Ethernet في Bluespec SystemVerilog(BSV) لمعالجة الحزم عالية الأداء على FPGA. على وجه التحديد، يوفر هذا الريبو وحدات لإنشاء وتحليل حزم UDP/IP/Ethernet. يتم أيضًا توفير وحدة معالجة ARP مع ذاكرة تخزين مؤقت غير محظورة لتخزين معلومات العنوان للتعامل مع دقة عنوان MAC تلقائيًا. إلى جانب بناء حزمة UDP/IP/Ethernet القياسية، يضيف Blue-Ethernet دعمًا لـ RoCE (RDMA عبر Ethernet المتقاربة): 1) دمج إنشاء والتحقق من ICRC (التكرار الدوري الثابت) في معالجة حزم UDP/IP؛ 2) توفير وحدات للتعامل مع PFC (التحكم في التدفق ذو الأولوية) لتحقيق نقل الشبكة بدون فقدان. وأخيرًا، يتم توفير وحدات تحويل الواجهة أيضًا لمولد الحزم والمحلل اللغوي للتفاعل مع نظام Xilinx 100G Ethernet الفرعي (CMAC).

بعض الدلائل الرئيسية لهذا الريبو موضحة أدناه:

├── lib # external libraries/repos

│ ├── blue-crc # high-performance CRC hardware implementation

│ └── blue-wrapper # BSV wrappers for generating ready-to-use Verilog interface

├── scripts # scripts used to build project

├── src # design source files

│ └── includes # files containing some commonly-used BSV types and modules

├── syn # scripts for vivado synthesis and implementation

└── test # source files for verification

├── bluesim # testbenches based on bluesim

├── cocotb # python testbenches based on cocotb

└── vivado # co-simulation with cmac using vivadoفيما يلي قائمة ببعض ملفات المصدر المهمة:

./src

├── ArpCache.bsv # Cache implementation storing MAC addresses got from ARP

├── ArpProcessor.bsv # processing unit handling ARP requests and responses

├── includes

│ ├── CompletionBuf.bsv

│ ├── ContentAddressMem.bsv

│ ├── EthernetTypes.bsv # numeric and struct types about protocol definition

│ ├── PortConversion.bsv # interface conversion modules used to generate ready-to-use Verilog

│ ├── Ports.bsv # numeric and struct types about in/output ports of modules

│ ├── RFile.bsv

│ ├── StreamHandler.bsv # modules implemented for manipulating data stream

│ └── EthUtils.bsv # utility functions and modules

├── MacLayer.bsv # generator and parser for Ethernet packet

├── PfcUdpIpArpEthRxTx.bsv # generator and parser for UDP/IP/Ethernet packet with PFC

├── PriorityFlowControl.bsv # modules handling PFC

├── UdpIpArpEthRxTx.bsv # generator and parser for UDP/IP/Ethernet packet

├── UdpIpEthRx.bsv # parser for UDP/IP/Ethernet packet

├── UdpIpEthTx.bsv # generator for UDP/IP/Ethernet packet

├── UdpIpLayer.bsv # parser and generator for UDP/IP packet

├── UdpIpLayerForRdma.bsv # parser and generator for UDP/IP packet with support for RoCE

└── XilinxCmacRxTxWrapper.bsv # bridge modules between parser/generator and Xilinx CMACيقدم هذا القسم وصفًا تفصيليًا لبعض المكونات المهمة التي يتم تنفيذها في شبكة إيثرنت الزرقاء، بما في ذلك وظائفها وواجهتها وبنية الأجهزة الخاصة بها.

ما تفعله مكونات الأجهزة المرتبطة بشبكة Ethernet هو في الأساس سلسلة من عمليات معالجة التدفق. يكون منشئ الحزم مسؤولاً عن إدخال تدفق الرأس في رأس تدفق الحمولة النافعة لإنشاء تدفق حزم كامل. على العكس من ذلك، ما يفعله المحلل اللغوي هو استخراج تدفق الرأس ودفق الحمولة من تدفق الحزمة. أما بالنسبة لإضافة المجموع الاختباري لحزمة ما، فسيتم تمرير تدفق الحزمة إلى حاسبة CRC ثم يتم إلحاق قيمة CRC الإخراج بذيل تدفق الحزمة.

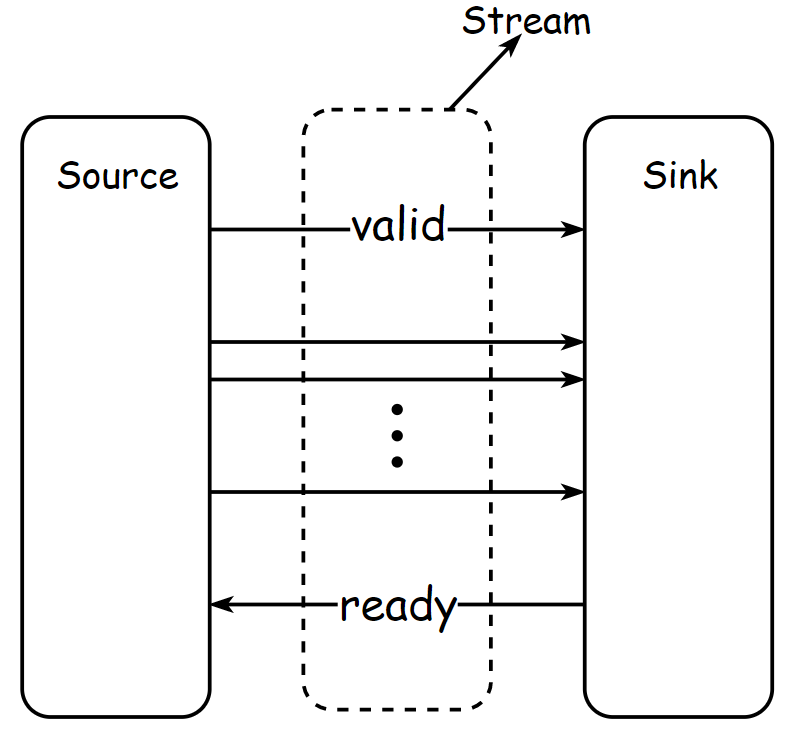

إن كيان الأجهزة المطابق للتدفق الذي نذكره هنا هو في الواقع مجموعة من إشارات البيانات التي يحرسها زوج إشارة التحكم الصالحة والجاهزة. تشير الإشارة الصالحة إلى أن المكون المصدر يريد نقل البيانات. والجاهزية تشير إلى أن الحوض جاهز لاستقبال البيانات من المصدر. يحدث النقل بين المصدر والمصرف بنجاح فقط عندما يكون كل من الصالح والجاهز مرتفعًا. إذا كان حجم البيانات المراد إرسالها أكبر من حجم عملية نقل واحدة، فيجب تجزئة البيانات ونقلها في سلسلة من عمليات النقل.

الجزء الأكثر صعوبة وعرضة للخطأ في معالجة التدفق هو كيفية التعامل مع إشارات التحكم الصالحة والجاهزة للتدفقات المختلفة. في BSV، يتم تنفيذ معالجة إشارات التحكم بواسطة المترجم وهي غير مرئية على المستوى النحوي، مما يساعد المصممين على التركيز على منطق معالجة الدفق.

يتم تغليف إشارات البيانات المستخدمة لنقل تدفق الحزمة بين المكونات المختلفة في بنية DataStream ، والتي تتضمن إشارة بيانات 256 بت، وإشارة تمكين بايت 32 بت، وتمثل إشارتان منطقيتان ما إذا كان هذا النقل هو الأخير أو الأول من تدفق الحزمة.

typedef 256 DATA_BUS_WIDTH ;

typedef TDiv # ( DATA_BUS_WIDTH , 8 ) DATA_BUS_BYTE_WIDTH ;

typedef Bit # ( DATA_BUS_WIDTH ) Data ;

typedef Bit # ( DATA_BUS_BYTE_WIDTH ) ByteEn ;

typedef struct {

Data data ;

ByteEn byteEn ;

Bool isFirst ;

Bool isLast ;

} DataStream deriving ( Bits , Bounded , Eq , FShow ) ; module mkAppendDataStreamHead # (

IsSwapEndian swapDataStream ,

IsSwapEndian swapAppendData ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( dType ) appendDataIn

)( FifoOut # ( DataStream )) ; module mkAppendDataStreamTail # (

IsSwapEndian swapDataStream ,

IsSwapEndian swapAppendData ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( dType ) appendDataIn ,

FifoOut # ( Bit # ( streamLenWidth )) streamLengthIn

)( FifoOut # ( DataStream )) ; interface ExtractDataStream # ( type dType ) ;

interface FifoOut # ( dType ) extractDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkExtractDataStreamHead # (

FifoOut # ( DataStream ) dataStreamIn

)( ExtractDataStream # ( dType )) ;يتم تنفيذ الوحدات الموجودة في حزمة UdpIpLayer لإنشاء حزمة UDP/IP وتحليلها.

يأخذ منشئ الحزم UdpIpMetaData الذي يحتوي على معلومات رأس UDP/IP ودفق الحمولة النافعة ومخرجات دفق حزم UDP/IP الكامل. يعمل محلل الحزم بالطريقة المعاكسة عن طريق استخراج UdpIpMetaData ودفق الحمولة من دفق حزم UDP/IP.

typedef struct {

UdpLength dataLen ; # The Length of payload data

IpAddr ipAddr ; # Desitnation IP address

IpDscp ipDscp ; # DSCP field used for PFC

IpEcn ipEcn ; # ECN field

UdpPort dstPort ; # Destination port number

UdpPort srcPort ; # Source port number

} UdpIpMetaData ;الإشارات المغلفة في بنية UdpIpMetaData لا تغطي جميع الحقول المحددة في رأس UDP/IP. يتم إصلاح بعض حقول الرأس لجهاز شبكة محدد، والتي يتم تغليفها في بنية UdpConfig وتحتاج إلى تكوينها قبل إرسال أو استقبال أي حزم. وبعض المجالات الأخرى ثابتة ومشفرة في مكونات الأجهزة.

typedef struct {

EthMacAddr macAddr ; # Source MAC address

IpAddr ipAddr ; # Source IP address

IpNetMask netMask ; # IP netmask

IpGateWay gateWay ; # IP gateway

} UdpConfig ; module mkUdpIpStream # (

UdpConfig udpConfig ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( UdpIpMetaData ) udpIpMetaDataIn ,

function UdpIpHeader genHeader ( UdpIpMetaData meta , UdpConfig udpConfig , IpID ipId )

)( FifoOut # ( DataStream )) ; interface UdpIpMetaDataAndDataStream ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkUdpIpMetaDataAndDataStream # (

UdpConfig udpConfig ,

FifoOut # ( DataStream ) udpIpStreamIn ,

function UdpIpMetaData extractMetaData ( UdpIpHeader hdr )

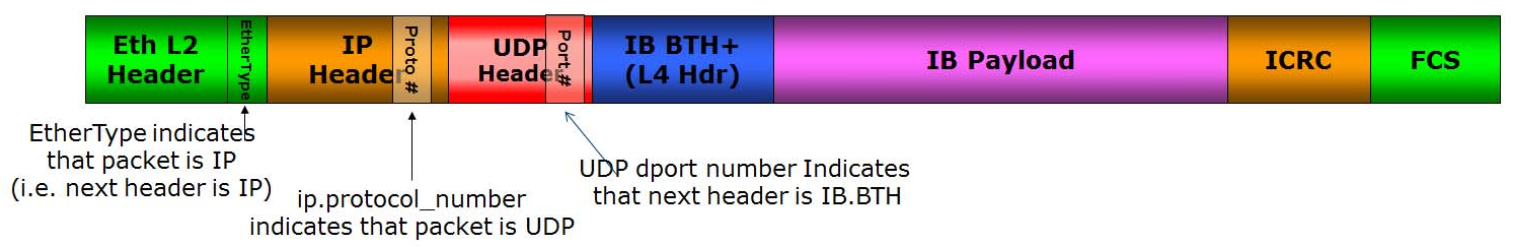

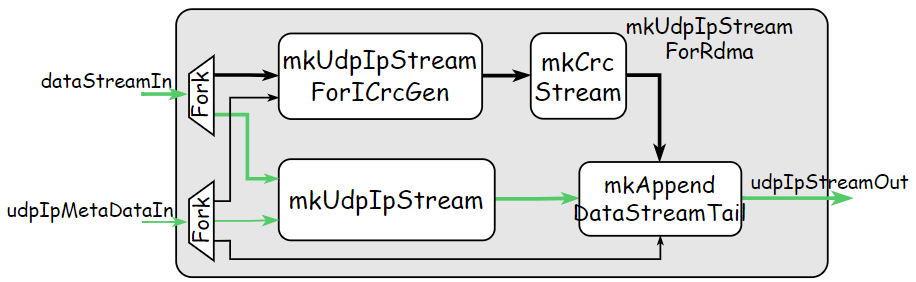

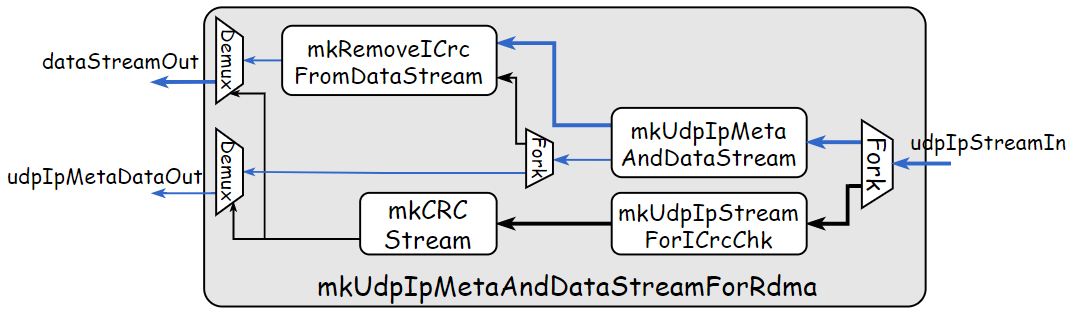

)( UdpIpMetaDataAndDataStream ) ; يتم تنفيذ الوحدات النمطية في حزمة UdpIpLayerForRdma استنادًا إلى UdpIpLayer مع دعم RoCE(RDMA عبر شبكة Ethernet المتقاربة). الوظيفة الإضافية المضافة لدعم RoCE هي إنشاء والتحقق من ICRC (Invariant CRC) المطلوبة لحزم RoCE. يتم تعريف تنسيق حزمة RoCE على النحو التالي:

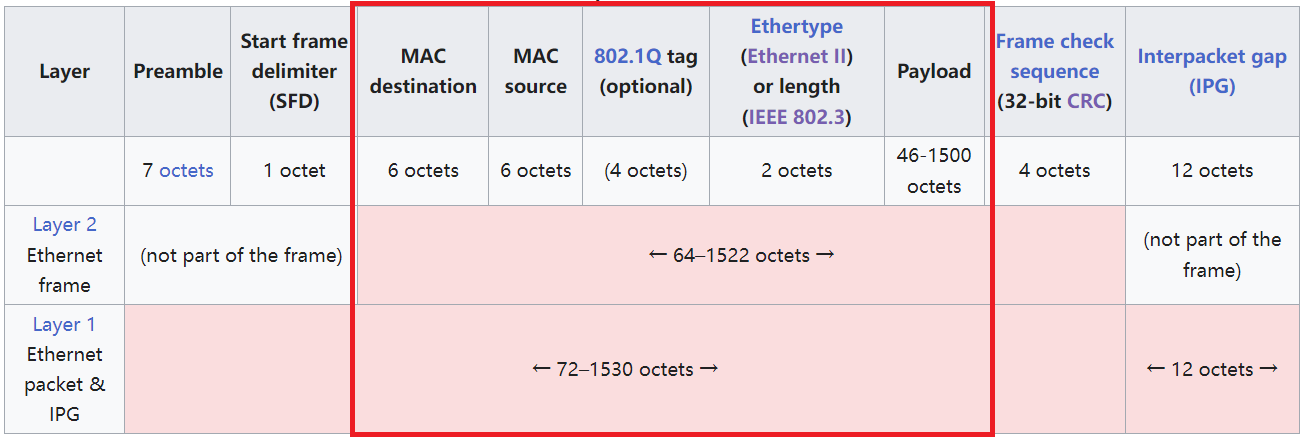

يتم تنفيذ الوحدات الموجودة في حزمة MacLayer لإنشاء حزمة Ethernet وتحليلها. يقوم المولد بإدخال رأس Ethernet إلى رأس دفق حزم UDP/IP لإنشاء دفق حزم Ethernet. يقوم المحلل اللغوي باستخراج رأس Ethernet ودفق حزم UDP/IP من دفق حزم Ethernet.

يتم تعريف معلومات الرأس المستخدمة لإنشاء حزمة Ethernet في بنية MacMetaData .

typedef struct {

EthMacAddr macAddr ; # Destination MAC address

EthType ethType ; # Type of Ethernet frame

} MacMetaData deriving ( Bits , Eq , FShow ) ;تجدر الإشارة إلى أن حزمة Ethernet التي يتم التعامل معها في MacLayer تغطي فقط الحقول الموضحة في المستطيل الأحمر في الشكل أدناه. يتم ترك الحقول الأخرى لتتم معالجتها بواسطة Xilinx CMAC IP.

module mkMacStream # (

FifoOut # ( DataStream ) udpIpStreamIn ,

FifoOut # ( MacMetaData ) macMetaDataIn ,

UdpConfig udpConfig

)( FifoOut # ( DataStream )) ; interface MacMetaDataAndUdpIpStream ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface FifoOut # ( DataStream ) udpIpStreamOut ;

endinterface

module mkMacMetaDataAndUdpIpStream # (

FifoOut # ( DataStream ) macStreamIn ,

UdpConfig udpConfig

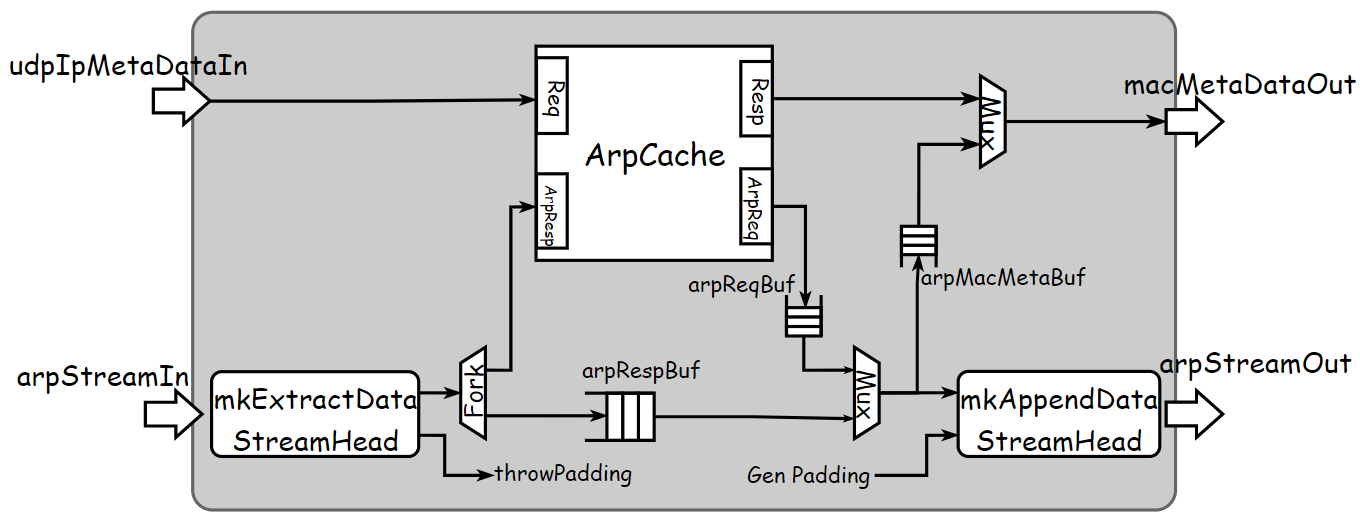

)( MacMetaDataAndUdpIpStream ) ; يتم استخدام بروتوكول تحليل العنوان (ARP) لاكتشاف عنوان MAC المرتبط بعنوان IP معين. في شبكة الإيثرنت الزرقاء، يتم تنفيذ الوحدة النمطية mkArpProcessor لمعالجة ARP، والتي تدمج مولد حزم ARP والمحلل اللغوي ووحدة mkArpCache التي تخزن عناوين MAC.

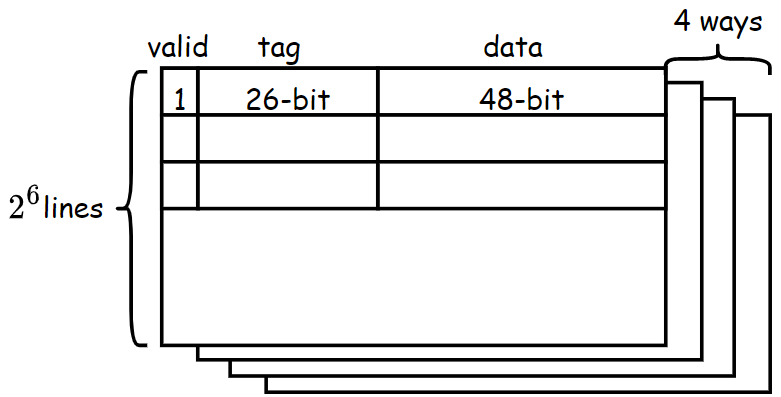

بالنسبة لذاكرة التخزين المؤقت المستخدمة في معالجة ARP، يتوافق عنوان IP 32 بت مع عنوان ذاكرة التخزين المؤقت وعنوان MAC 48 بت يتوافق مع بيانات ذاكرة التخزين المؤقت. يظهر أدناه الترتيب الافتراضي لمصفوفة الذاكرة لذاكرة التخزين المؤقت ARP، وهو عبارة عن بنية ترابطية رباعية الاتجاهات، تحتوي كل طريقة على 64 سطرًا ويتضمن كل سطر 1 بت صالحًا وعلامة 26 بت وبيانات 48 بت. يبلغ الحجم الإجمالي لتكوين الصفيف الافتراضي هذا حوالي 1.2 كيلو بايت. إنه مدعوم لتغيير حجم مجموعة الذاكرة عن طريق تحديد عدد الخطوط والطرق. استنادًا إلى مصفوفة الذاكرة هذه، تم تصميم ذاكرة التخزين المؤقت بحيث لا تكون محظورة، وتدعم الطلبات المعلقة (الطلبات المتعددة أثناء الرحلة) وتستخدم خوارزمية LRU الزائفة لاستبدال خط ذاكرة التخزين المؤقت.

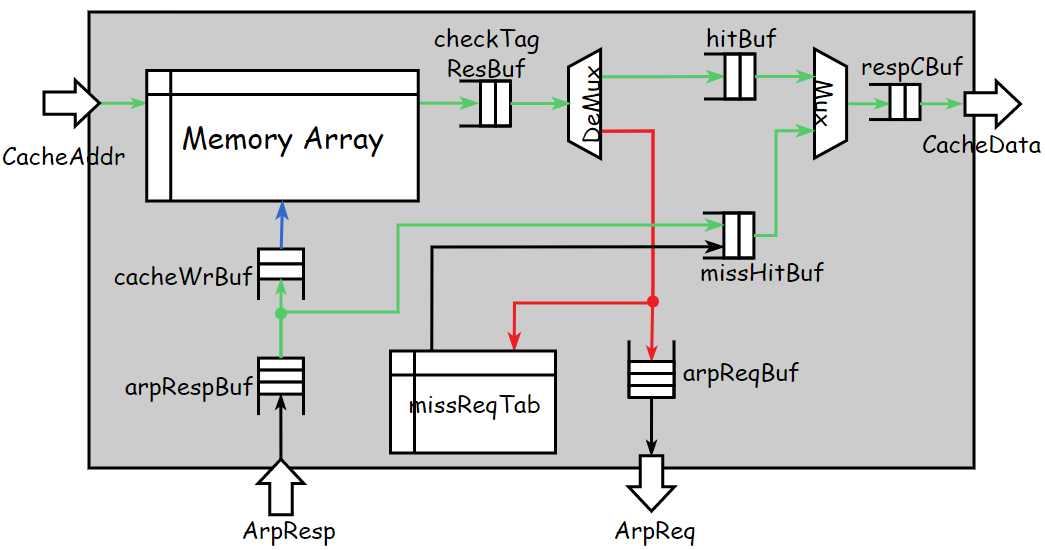

يظهر أدناه تعريف الواجهة والمخطط الهيكلي المبسط لوحدة mkArpCache . يحتوي ArpCache على واجهتين فرعيتين: يتعامل CacheServer مع التفاعلات مع المكونات التي توفر خدمة تحليل عنوان MAC؛ ويتعامل arpClient مع التفاعلات مع mkArpProcessor لبدء طلب ARP والحصول على عنوان MAC من استجابة ARP. سير العمل الأساسي لوحدة mkArpCache هو كما يلي:

عندما تتلقى ذاكرة التخزين المؤقت طلب قراءة، فإنها تبحث أولاً في مصفوفة الذاكرة للحصول على جميع العلامات والبيانات المقابلة لعنوان IP المحدد. ثم يقوم بفحص العلامات لمعرفة ما إذا كانت البيانات التي نحتاجها مخزنة في ذاكرة التخزين المؤقت. إذا تم الوصول إلى ذاكرة التخزين المؤقت، فسيتم إرسال البيانات التي تم جلبها إلى hitBuf . أو يتم إرسال عنوان IP إلى arpReqBuf لبدء طلب ARP. وعندما تعود استجابة ARP، تتم كتابة البيانات ومعلومات العنوان التي تحملها إلى CacheWrBuf و missHitBuf لتحديث مصفوفة الذاكرة وإرجاع استجابة قراءة ذاكرة التخزين المؤقت.

interface ArpCache ;

interface Server # ( CacheAddr , CacheData ) cacheServer ;

interface Client # ( CacheAddr , ArpResp ) arpClient ;

endinterface

أصعب جزء في تنفيذ ذاكرة التخزين المؤقت هو دعم الميزة المتميزة، وهي دعم طلبات القراءة المتعددة أثناء الرحلة. المشكلة الناجمة عن المعلقة هي أن وقت الاستجابة يختلف لكل طلب ARP على متن الطائرة، مما يعني أن الطلب المتأخر قد يتلقى استجابته أولاً. لذلك هناك حاجة إلى آلية إعادة الطلب لضمان المراسلات بين عنوان الطلب وبيانات الاستجابة عند حدوث ضياع في ذاكرة التخزين المؤقت. لتحقيق الاستجابة بالترتيب، تم دمج المخزن المؤقت للإكمال respCBuf والذاكرة القابلة للتوجيه للمحتوى MissReqTab في تدفق البيانات. يعمل المخزن المؤقت للإكمال مثل FIFO مع دعم إضافي لوظيفة الحجز. قبل تشغيل قائمة الانتظار الفعلية، يمكننا أولاً حجز أمر في المخزن المؤقت للإكمال. وتتبع عملية dequeue الترتيب المحجوز بغض النظر عن الترتيب المتسلسل الفعلي لعمليات enqueue. بالنسبة لكل طلب قراءة، يتم عكس ترتيب قائمة الانتظار في respCBuf بمجرد استلامه. ونظرًا لأن طلب ARP لا يمكنه حمل معلومات الطلب، يتم تطبيق MissReqTab لتخزينها.

يمكن للوحدة أن تعمل كعميل وخادم ARP. كخادم، يحتاج المعالج إلى إنشاء طلب ARP إذا كان عنوان MAC الخاص بـ IP الهدف غير معروف ثم ينتظر استجابة ARP من الجهاز المستهدف. كعميل، يتلقى معالج ARP طلب ARP من الأجهزة الأخرى ويرسل استجابة ARP تحمل عنوان MAC الخاص به.

interface ArpProcessor ;

interface FifoOut # ( DataStream ) arpStreamOut ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface Put # ( UdpConfig ) udpConfig ;

endinterface

module mkArpProcessor # (

FifoOut # ( DataStream ) arpStreamIn ,

FifoOut # ( UdpIpMetaData ) udpIpMetaDataIn

)( ArpProcessor ) ; يتم تنفيذ الوحدات الموجودة في حزمة UdpIpEthRx لتلقي حزم UDP/IP/Ethernet وتحليلها.

interface UdpIpEthRx ;

interface Put # ( UdpConfig ) udpConfig ;

interface Put # ( AxiStream512 ) axiStreamIn ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkGenericUdpIpEthRx # ( Bool isSupportRdma )( UdpIpEthRx )

يتم تنفيذ الوحدات الموجودة في حزمة UdpIpEthTx لإنشاء وإرسال حزم UDP/IP/Ethernet.

interface UdpIpEthTx ;

interface Put # ( UdpConfig ) udpConfig ;

interface Put # ( UdpIpMetaData ) udpIpMetaDataIn ;

interface Put # ( MacMetaData ) macMetaDataIn ;

interface Put # ( DataStream ) dataStreamIn ;

interface AxiStream512FifoOut axiStreamOut ;

endinterface

module mkGenericUdpIpEthTx # ( Bool isSupportRdma )( UdpIpEthTx ) ;

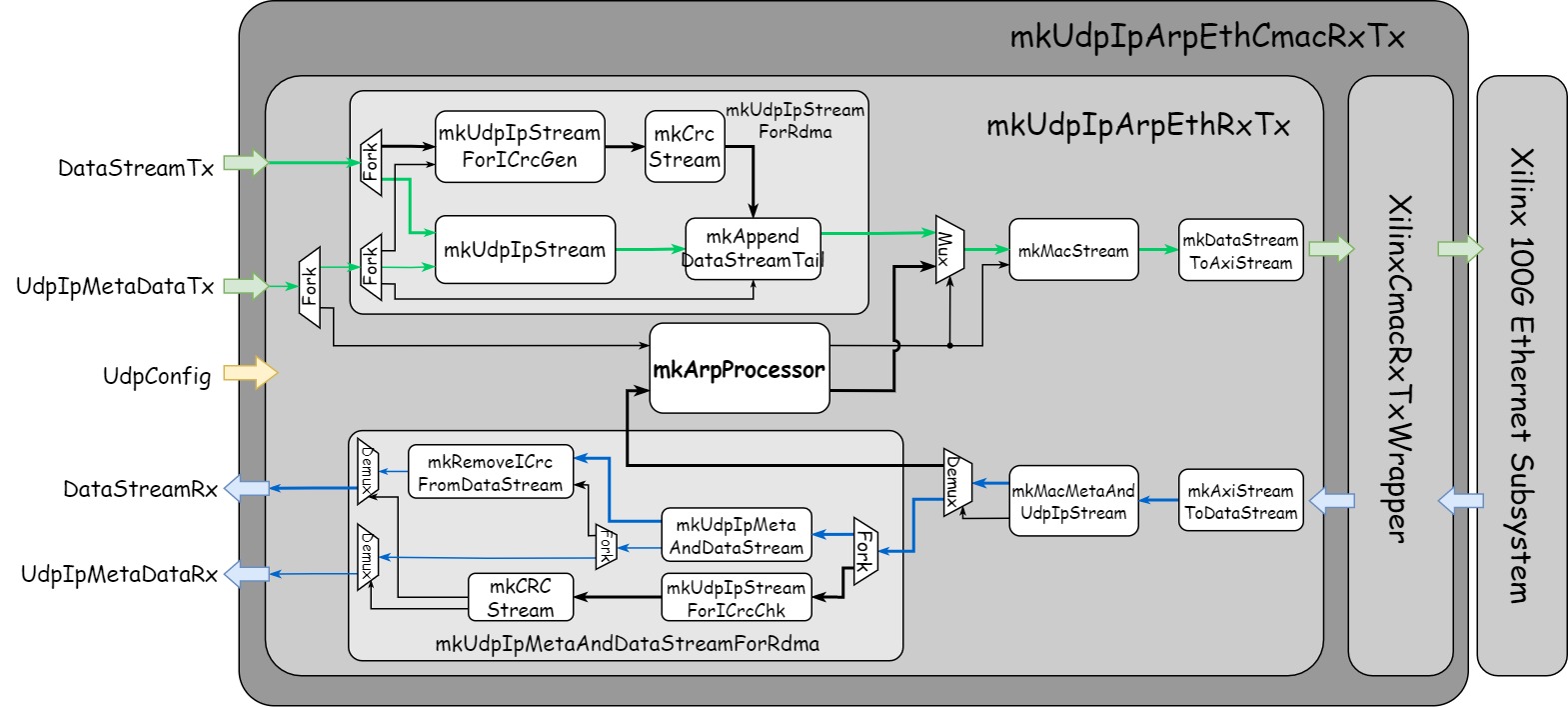

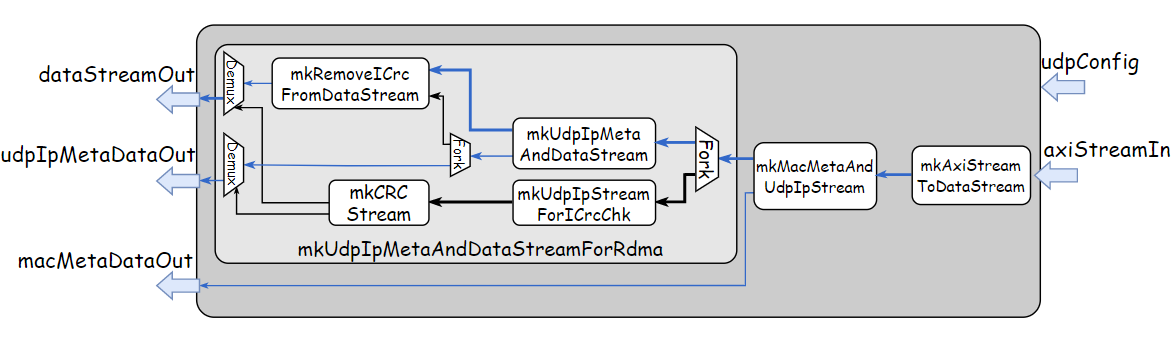

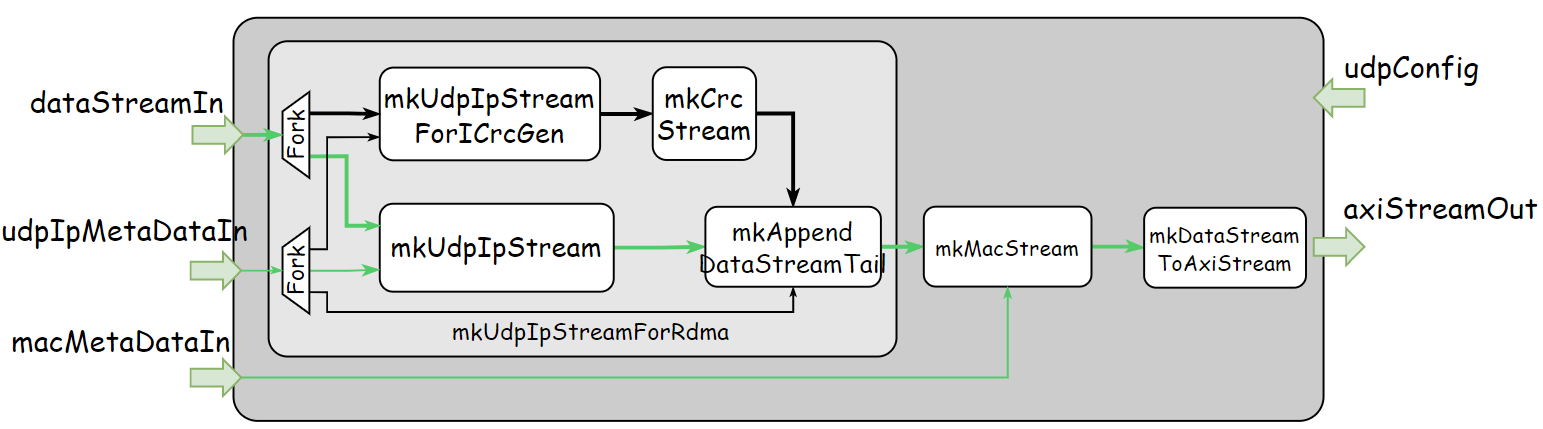

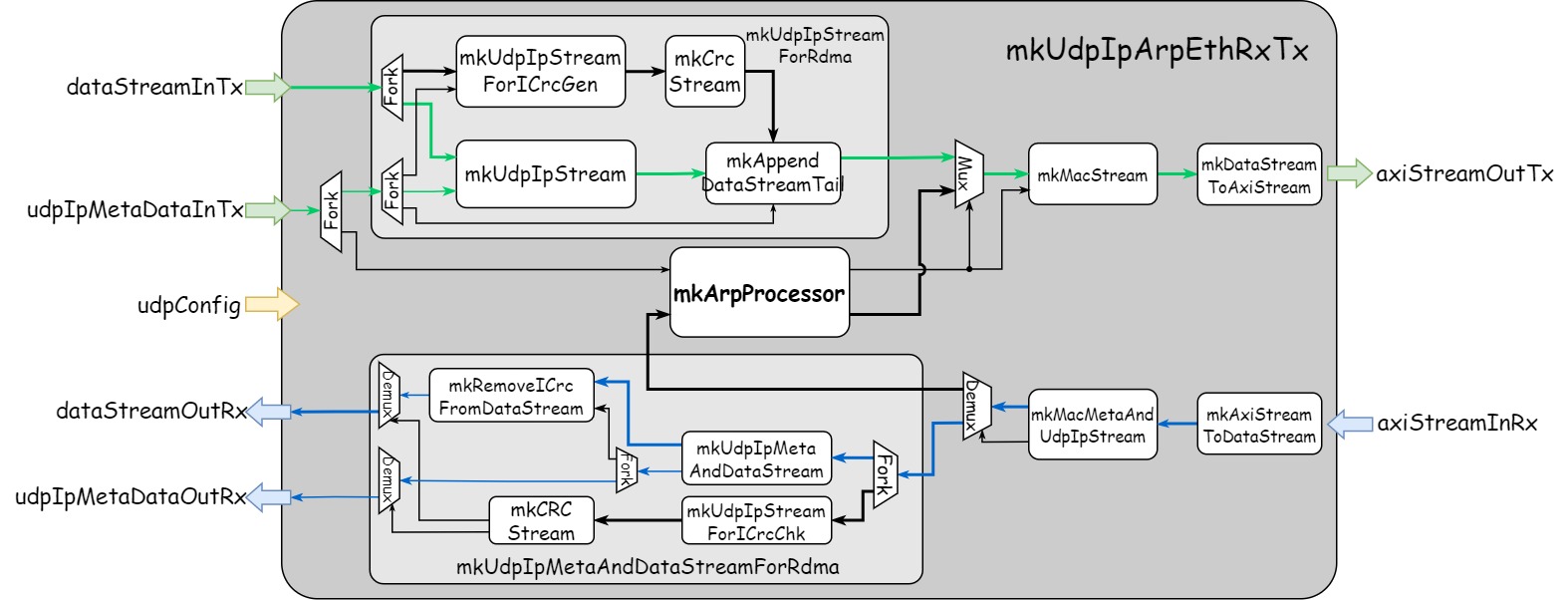

تم تصميم الوحدات المتوفرة في حزمة UdpIpArpEthRxTx لاستقبال وإرسال حزم UDP/IP/Ethernet والتعامل مع طلب ARP والاستجابة في نفس الوقت.

يمكن تقسيم الوحدة إلى مسارين متعاكسين للتدفقات، بما في ذلك مسار الإرسال ومسار الاستقبال:

بالنسبة لمسار النقل، فإنه يأخذ دفق الحمولة النافعة dataStreamInTx و udpIpMetaDataIn الذي يحمل دفق معلومات الرأس وينشئ axiStreamOutTx الذي يحمل دفق حزم UDP/IP/Ethernet. ليست هناك حاجة لتوفير MacMetaData الذي يحتوي على معلومات رأس Ethernet كوحدة mkUdpIpEthTx ، لأن mkArpProcessor مسؤول عن معالجة تحليل عنوان MAC وإنشاء معلومات رأس Ethernet.

بالنسبة لمسار الاستقبال، فإنه يعمل بالطريقة المعاكسة عن طريق استخراج دفق الحمولة النافعة dataStreamOutRx و udpIpMetaDataOutRx الذي يحمل دفق معلومات الرأس من axiStreamInRx الذي يحمل دفق حزم UDP/IP/Ethernet.

تتم مشاركة مولد حزم Ethernet والمحلل اللغوي بواسطة كل من حزمة UDP/IP وحزمة ARP، لذلك هناك حاجة إلى Mux و Demux إضافيين في مسار الإرسال والاستقبال لتحكيم الدفق وتوزيعه. تحدد معلمة الوحدة النمطية isSupportRdma ما إذا كانت تدعم معالجة حزم RoCE أم لا. إذا تم تعطيل دعم RDMA، فسنحتاج فقط إلى mkUdpIpStream و mkUdpIpMetaAndDataStream في مسار الإرسال والاستقبال على التوالي.

interface UdpIpArpEthRxTx ;

interface Put # ( UdpConfig ) udpConfig ;

// Tx

interface Put # ( UdpIpMetaData ) udpIpMetaDataInTx ;

interface Put # ( DataStream ) dataStreamInTx ;

interface AxiStream512FifoOut axiStreamOutTx ;

// Rx

interface Put # ( AxiStream512 ) axiStreamInRx ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOutRx ;

interface FifoOut # ( DataStream ) dataStreamOutRx ;

endinterface

module mkGenericUdpIpArpEthRxTx # ( Bool isSupportRdma )( UdpIpArpEthRxTx ) ;

تلتف الوحدة النمطية mkGenericUdpIpArpEthRxTx باستخدام الوحدات المتوفرة في الغلاف الأزرق بحيث تنشئ واجهة Verilog جاهزة للاستخدام.

تدمج الوحدة كلا من وحدة mkGenericUdpIpArpEthRxTx ووحدة mkXilinxCmacTxWrapper . إنه مصمم للتفاعل مع Xilinx CMAC IP لإرسال واستقبال حزم UDP/IP/Ethernet من وإلى الوسائط المادية.

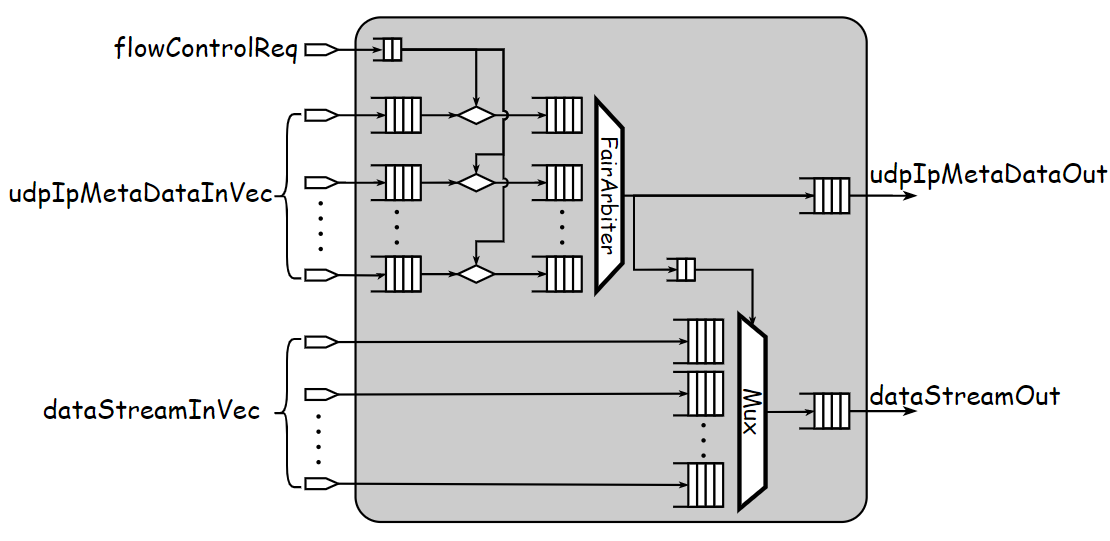

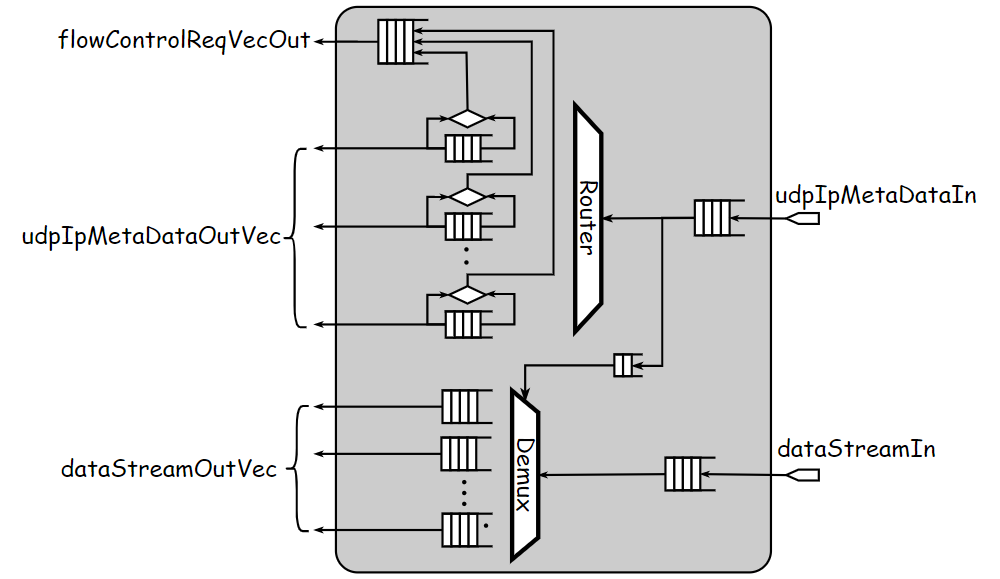

يتم تنفيذ الوحدات الموجودة في حزمة PriorityFlowControl لتحقيق آلية التحكم في التدفق ذات الأولوية لضمان نقل الشبكة بدون فقدان.

interface PriorityFlowControlTx ;

interface Get # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface Get # ( DataStream ) dataStreamOut ;

endinterface

module mkPriorityFlowControlTx # (

FifoOut # ( FlowControlReqVec ) flowControlReqVecIn ,

Vector # ( VIRTUAL_CHANNEL_NUM , DataStreamFifoOut ) dataStreamInVec ,

Vector # ( VIRTUAL_CHANNEL_NUM , UdpIpMetaDataFifoOut ) udpIpMetaDataInVec

)( PriorityFlowControlTx ) ;

interface PriorityFlowControlRx # (

numeric type bufPacketNum ,

numeric type maxPacketFrameNum ,

numeric type pfcThreshold

) ;

interface FifoOut # ( FlowControlReqVec ) flowControlReqVecOut ;

interface Vector # ( VIRTUAL_CHANNEL_NUM , Get # ( DataStream )) dataStreamOutVec ;

interface Vector # ( VIRTUAL_CHANNEL_NUM , Get # ( UdpIpMetaData )) udpIpMetaDataOutVec ;

endinterface

module mkPriorityFlowControlRx # (

DataStreamFifoOut dataStreamIn ,

UdpIpMetaDataFifoOut udpIpMetaDataIn

)( PriorityFlowControlRx # ( bufPacketNum , maxPacketFrameNum , pfcThreshold )) ;

يدمج mkGenericPfcUdpIpArpEthRxTx mkPriorityFlowControlRx/Tx و mkGenericUdpIpArpEthRxTx لتوفير وظيفة إنشاء حزم UDP/IP/Ethernet وتحليلها مع دعم التحكم في التدفق ذي الأولوية. بالنسبة لنقل الحزم، يستغرق الأمر ثماني قنوات من تدفق الحمولة النافعة ومعلومات رأس UDP/IP، ويخرج تدفق حزمة UDP/IP/Ethernet واحد. بالنسبة لاستقبال الحزم، فإنه يأخذ تدفق حزمة UDP/IP/Ethernet واحدًا ويوجه رأس UDP/IP المستخرج وتيار الحمولة إلى واحدة من قنوات الإخراج الثماني.

يدمج mkPfcUdpIpArpEthCmacRxTx كلاً من وحدة mkGenericPfcUdpIpArpEthRxTx ووحدة mkXilinxCmacTxWrapper . إنه مصمم للتفاعل مع Xilinx CMAC IP لإرسال واستقبال حزم UDP/IP/Ethernet من وإلى الوسائط المادية.

يتم تنفيذ تركيب وتنفيذ الوحدة الرئيسية mkGenericUdpIpArpEthRxTx على أساس جهاز Xilinx xcvu9p باستخدام Vivado. وتظهر النتائج أن الدائرة يمكن أن تصل إلى تردد العمل البالغ 500 ميجا هرتز وتوفر ذروة إنتاجية تبلغ 128 جيجابت في الثانية. يتم سرد استخدام موارد الأجهزة على النحو التالي:

CLB Logic

+----------------------------+-------+-------+------------+-----------+-------+

| Site Type | Used | Fixed | Prohibited | Available | Util % |

+----------------------------+-------+-------+------------+-----------+-------+

| CLB LUTs | 63886 | 0 | 0 | 1182240 | 5.40 |

| LUT as Logic | 41242 | 0 | 0 | 1182240 | 3.49 |

| LUT as Memory | 22644 | 0 | 0 | 591840 | 3.83 |

| LUT as Distributed RAM | 22644 | 0 | | | |

| LUT as Shift Register | 0 | 0 | | | |

| CLB Registers | 44099 | 0 | 0 | 2364480 | 1.87 |

| Register as Flip Flop | 44099 | 0 | 0 | 2364480 | 1.87 |

| Register as Latch | 0 | 0 | 0 | 2364480 | 0.00 |

| CARRY8 | 73 | 0 | 0 | 147780 | 0.05 |

| F7 Muxes | 194 | 0 | 0 | 591120 | 0.03 |

| F8 Muxes | 28 | 0 | 0 | 295560 | < 0.01 |

| F9 Muxes | 0 | 0 | 0 | 147780 | 0.00 |

+----------------------------+-------+-------+------------+-----------+-------+

BLOCKRAM

+-------------------+------+-------+------------+-----------+-------+

| Site Type | Used | Fixed | Prohibited | Available | Util % |

+-------------------+------+-------+------------+-----------+-------+

| Block RAM Tile | 4.5 | 0 | 0 | 2160 | 0.21 |

| RAMB36 / FIFO * | 4 | 0 | 0 | 2160 | 0.19 |

| RAMB36E2 only | 4 | | | | |

| RAMB18 | 1 | 0 | 0 | 4320 | 0.02 |

| RAMB18E2 only | 1 | | | | |

| URAM | 0 | 0 | 0 | 960 | 0.00 |

+-------------------+------+-------+------------+-----------+-------+يقدم هذا القسم كيفية البدء بهذا المشروع. قبل القيام بأي خطوات أخرى، تحتاج أولاً إلى إعداد بيئة تطوير تشير إلى البرنامج النصي setup.sh. فيما يلي قائمة بالتبعيات:

بعد إعداد البيئة، انسخ هذا الريبو إلى دليل محدد. نشير هنا إلى هذا الدليل باسم BLUE_ETH:

git clone --recursive https://github.com/wengwz/blue-ethernet.git $( BLUE_ETH ) هناك ثلاثة مستويات مختلفة من مقاعد الاختبار المتوفرة في شبكة إيثرنت الزرقاء:

# Specify TARGET to the name of target component

cd $( BLUE_ETH ) /test/bluesim

make TARGET=ArpCache # Run tests of UdpIpEthRx/Tx

# Enable/Disable support for RDMA by setting SUPPORT_RDAM to True/False

cd $( BLUE_ETH ) /test/cocotb

make cocotb TARGET=UdpIpEthTx SUPPORT_RDMA=TRUE

# Run simulation on virtual network

# Change NET_IFC in run_docker_net_test.sh to the name of your network card

cd $( BLUE_ETH ) /test/cocotb

docker build -f ./build_docker/Dockerfile -t ethernet-test ./build_docker

./run_docker_net_test.sh # Available TARGET includes UdpIpArpEthCmacRxTx/PfcUdpIpArpEthCmacRxTx

# Enable/Disable support for RDMA by setting SUPPORT_RDAM to True/False

cd $( BLUE_ETH ) /test/vivado

make sim TARGET=UdpIpArpEthCmacRxTx SUPPORT_RDMA=Falseيتم توفير البرامج النصية المستخدمة لتشغيل التوليف وتنفيذ التصاميم في الدليل $(BLUE_ETH)/syn.

# TARGET specifies the top module to be synthsized or implemented

# SUPPORT_RDMA specifies whether modules supports RoCE packet processing

# ONLYSYNTH decides whether or not run implemetation after synthesis

cd $( BLUE_ETH ) /syn

make vivado TARGET=UdpIpArpEthRxTx SUPPORT_RDMA=False ONLYSYNTH=0 # TARGET specifies the name of top module to be generated

# Specify SUPPORT_RDMA if needed

cd $( BLUE_ETH ) /test/cocotb

make verilog TARGET=UdpIpEthTx SUPPORT_RDMA=TRUEbsc -p +: $( BLUE_ETH ) /src: $( BLUE_ETH ) /src/includes ...يتضمن تنفيذ Blue-Ethernet استخدام المكتبات الخارجية التالية: