ملحوظة:

يتم تحديث وثائق هذا المشروع لتعكس التغييرات في الإصدار الجديد المعاد تصميمه من Caravel.

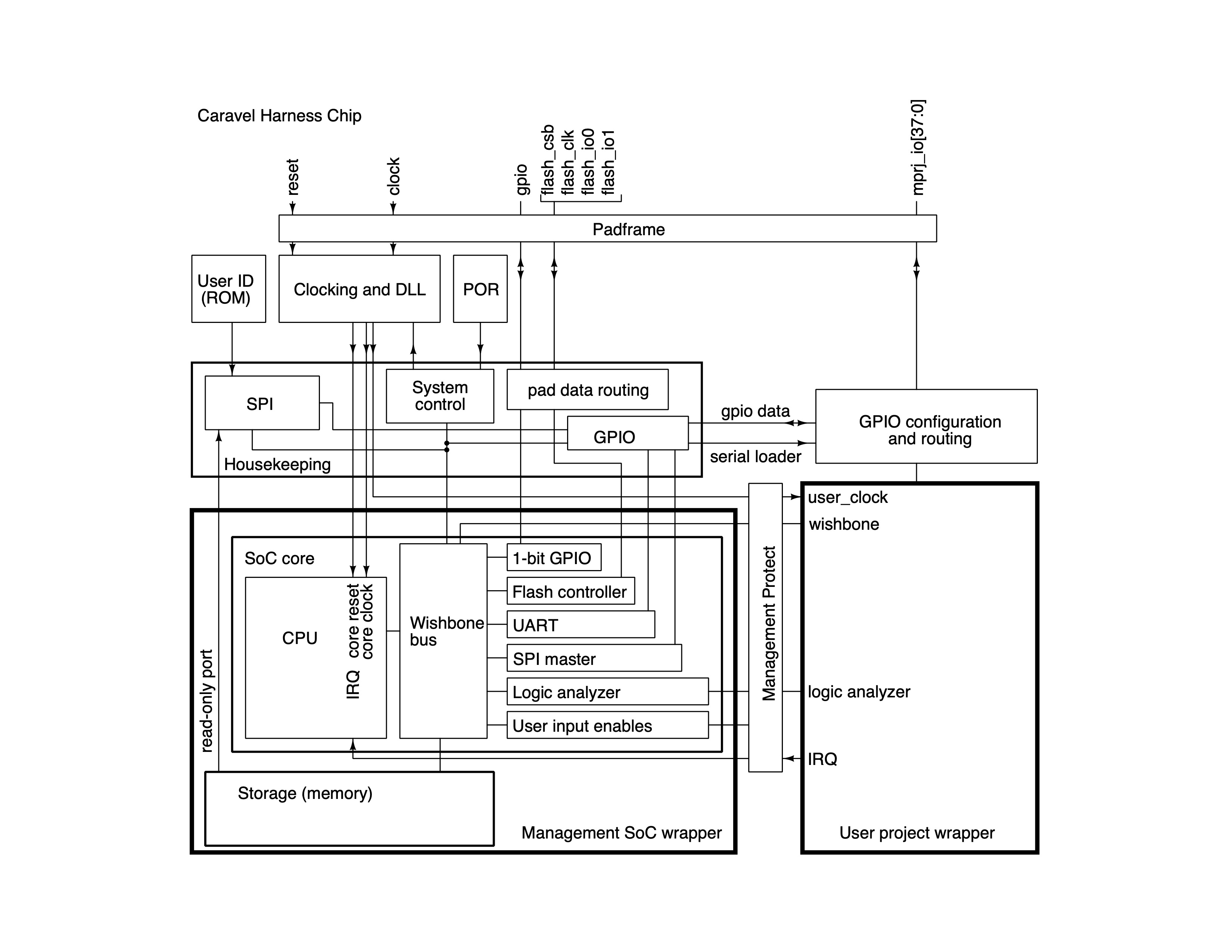

Caravel هو قالب SoC لمكوكات Efabless Open MPW وchipIgnite استنادًا إلى عقدة Sky130 من SkyWater Technologies. تم توضيح بنية SoC الحالية أدناه.

ورقة البيانات والوثائق التفصيلية موجودة هنا

يتكون Caravel من إطار الحزام بالإضافة إلى غلافين للوحدات المنسدلة لمنطقة الإدارة ومنطقة مشروع المستخدم .

يحتوي الحزام نفسه على وحدة تسجيل الوقت، وDLL، ومعرف المستخدم، وSPI للتدبير المنزلي، وPOR، والتحكم في GPIO.

انتقلت معالجة GPIO من إدارة SoC إلى SPI. يحصل SPI على واجهة عظم الترقوة؛ تتحدث شركة SoC للإدارة إلى SPI من خلال عظم الترقوة، وليس عن طريق الاستيلاء على واجهة SPI ذات 4 سنون.

تحتوي الكتلة الجديدة مثل المعرف على وضع التشغيل لكل GPIO. يمكن تهيئتها بملف نصي. يتم إصلاح دبابيس SPI للتشغيل عند بدء التشغيل.

عند تشغيل الطاقة، يقوم SPI تلقائيًا بتكوين GPIO. التحميل اليدوي ممكن من كل من SPI ومن ناقل عظم الترقوة.

تم دمج جميع الوظائف داخل الحزام ولكن خارج شركة نفط الجنوب الخاصة بالإدارة في وحدة واحدة كبيرة تسمى "التدبير المنزلي". يتضمن ذلك عددًا من السجلات لجميع الوظائف المضمنة، مع واجهة SPI "للباب الأمامي" متصلة بإطار الوسادة من خلال دبابيس GPIO من 1 إلى 4، وواجهة عظم الترقوة "للباب الخلفي" متصلة بـ SoC للإدارة. تحتفظ شركة الإدارة بكتلة الذاكرة عند 0x26000000 لوحدة التدبير المنزلي. تقوم وحدة التدبير المنزلي بتبادل البيانات مع شركة نفط الجنوب للإدارة عبر واجهة تستخدم بيانات تسجيل SPI على مستوى البايت. تقرأ آلة الحالة الصغيرة أربعة عناوين عظم الترقوة المتجاورة ويحدد جهاز فك تشفير العناوين سجل SPI المقابل. تقوم آلة الحالة بإيقاف SoC حتى تتم معالجة جميع البايتات الأربعة قبل إرجاع إشارة الإقرار.

منطقة الإدارة عبارة عن وحدة نمطية يتم تنفيذها كمستودع منفصل. وهو يشتمل عادةً على SoC يعتمد على RISC-V والذي يتضمن عددًا من الأجهزة الطرفية مثل أجهزة ضبط الوقت وuart وgpio. تقوم منطقة الإدارة بتشغيل البرامج الثابتة التي يمكن استخدامها من أجل:

تطبق منطقة الإدارة SRAM لإدارة SoC.

يمكن العثور على الإنشاء الافتراضي لنواة الإدارة هنا. راجع وثائق الإدارة الأساسية لمزيد من التفاصيل.

هذه هي مساحة المستخدم. تحتوي على مساحة سيليكون محدودة 2.92mm x 3.52mm بالإضافة إلى عدد ثابت من وسادات الإدخال / الإخراج 38 ومنصات الطاقة 4 .

تتمتع مساحة المستخدم بإمكانية الوصول إلى الأدوات المساعدة التالية التي توفرها شركة SoC للإدارة:

38 منفذ إدخال/إخراج128 تحقيقات محلل المنطق منطقتك هي مساحة المستخدم الكاملة، لذا لا تتردد في إضافة مشروعك هناك أو إنشاء ماكرو مختلف وتقويته بشكل منفصل ثم أدخله في user_project_wrapper للمشاريع الرقمية أو أدخله في user_project_analog_wrapper للمشاريع التناظرية.

إذا كنت تقوم بإنشاء مشروع رقمي لمساحة المستخدم، فراجع نموذج المشروع على caravel_user_project.

إذا كنت ستستخدم OpenLANE لتعزيز تصميمك، فاتبع الإرشادات الواردة في هذا الملف التمهيدي.

يجب أن تلتزم مشاريع المستخدم الرقمي بالمتطلبات التالية:

user_project_wrapperuser_project_wrapper بترتيب الدبوس المحدد في Digital Wrapper Pin Order.user_project_wrapper بتكوينات التصميم الثابتة في Digital Wrapper Fixed Configuration.إذا كنت تقوم بإنشاء مشروع تمثيلي لمساحة المستخدم، فراجع نموذج المشروع على caravel_user_project_analog.

يجب أن تلتزم مشاريع المستخدم التناظرية بالمتطلبات التالية:

user_analog_project_wrapperuser_analog_project_wrapper الغلاف التناظري الفارغ.user_analog_project_wrapper بنفس ترتيب الدبوس وموضع الغلاف التناظري الفارغ. برجاء التأكد من تشغيل make compress قبل الالتزام بأي شيء في مستودعك. تجنب وجود إصدارين من gds/user_project_wrapper.gds أحدهما مضغوط والآخر غير مضغوط.

للحصول على معلومات حول الأدوات والإصدارات، يرجى الرجوع إلى tool-versioning.rst.

gds/ : يشمل جميع ملفات gds المستخدمة أو المنتجة من المشروع.def : يشمل جميع ملفات def المستخدمة أو المنتجة من المشروع.lef/ : يتضمن جميع ملفات lef المستخدمة أو المنتجة من المشروع.mag/ : يتضمن جميع ملفات mag المستخدمة أو المنتجة من المشروع.maglef : يشمل جميع ملفات maglef المستخدمة أو المنتجة من المشروع.spi/lvs/ : يتضمن كافة ملفات التوابل المستخدمة أو المنتجة من المشروع.verilog/dv : يشمل جميع مقاعد اختبار المحاكاة وكيفية تشغيلها.verilog/gl/ : يتضمن كافة قوائم الشبكة المُركبة/المفصلة.verilog/rtl : يشمل جميع ملفات Verilog RTLs والملفات المصدر.openlane/<macro>/ : يتضمن كافة ملفات التكوين المستخدمة لتشغيل openlane في مشروعك.info.yaml : يتضمن جميع المعلومات المطلوبة في هذا المثال. يرجى التأكد من أنك تشير إلى قائمة شبكة كارافيل مفصلة بالإضافة إلى قائمة شبكة مركبة على مستوى البوابة لـ user_project_wrapperملحوظة:

إذا كنت تستخدم openlane لتعزيز تصميمك، فيجب ملء أدلةverilog/gldef/lef/gds/magmaglefتلقائيًا بواسطة openlane.

تحقق من mpw-one-final لمعرفة الكارافيل المستخدم لشريط mpw-one.

>make ship مطلوبًا.