***Dieses Projekt ist noch nicht abgeschlossen. Es weist derzeit Fehler auf und es wurden noch nicht alle Funktionen getestet!

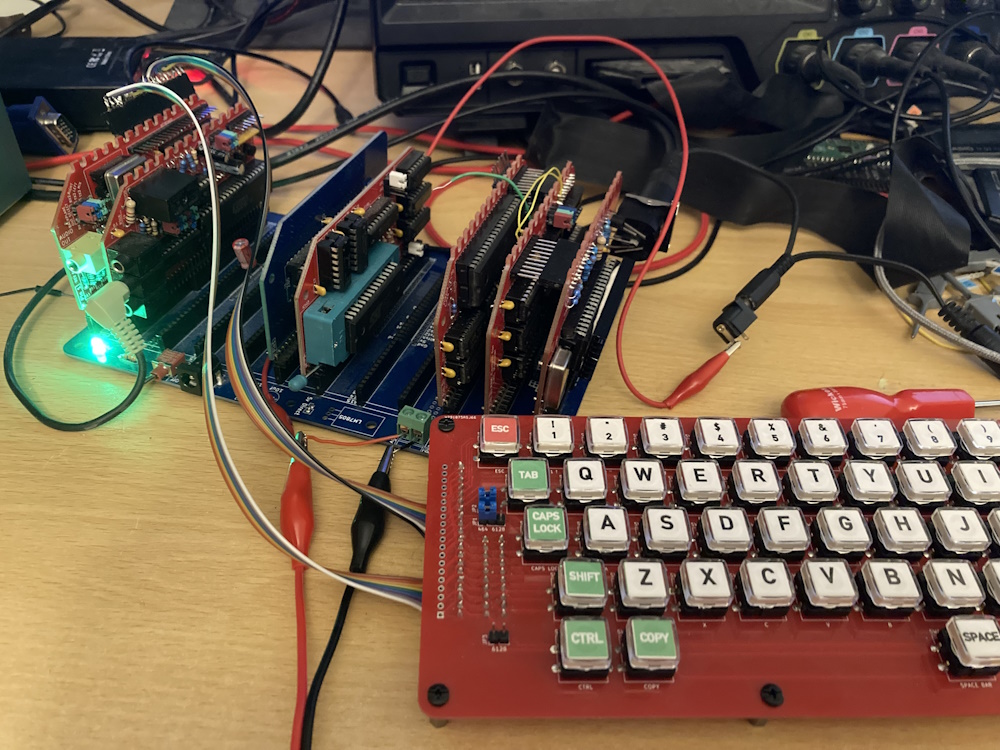

Die aktuellen Module sind so konzipiert, dass sie auf eine leicht modifizierte RC2014 Pro-Backplane passen. Im folgenden Text werde ich den aktuellen Status des Projekts, die erforderlichen Problemumgehungen, um es zum Laufen zu bringen, und grundlegende Build-Details erläutern. Da das Projekt noch in Bearbeitung ist, wird dieses Dokument absichtlich knapp gehalten.

Das Projekt verwendet Stiftleisten/Buchsen, um Module innerhalb von Subsystemen (dem Video-RAM-Subsystem und dem IO-Sound-Subsystem) zu verbinden. Dies erfordert einen längeren Stiftkopf als üblich.

Dies ist eine leicht modifizierte RC2014 Pro-Backplane. Der CPC Modular nutzt die Leitungen D8 bis D15 sowohl im Video-RAM-Subsystem als auch im IO-Sound-Subsystem für lokale Datenbusse. Daher:

Sie müssen die Linien D8 bis D15 zwischen diesen Abschnitten durchtrennen.

Dies ist ein leicht modifiziertes RC2014 „Z80 CPU-Modul“. Änderung:

Die Widerstände auf der Platine müssen durch einen anderen Wert ersetzt werden. 2,2 kOhm sollten gut funktionieren.

Dieses Board enthält 512 KB NORFLASH. Es enthält Schaltkreise, mit denen der Blitz vor Ort gebrannt werden kann (ungetestet). Konfiguration:

Es muss eine Brücke installiert werden, die Pin 2 von LK4 und Pin 2 von LK5 überbrückt.

Um das Flash-Brennen zu ermöglichen, installieren Sie die Links LK1, LK2 und LK3. Ansonsten offen lassen.

Meine Notizen zum Schreiben in den Flash (aus der Schaltplandatei entnommen) sind:

!!! Es gibt keine Möglichkeit, Speicherschreibvorgänge auf dem Standard-CPC-System zu deaktivieren. Daher werden alle Speicherschreibvorgänge, die wir in das ROM ausführen, während WRITE_EN aktiv ist, auch in den RAM schreiben.

Da das ROM jedoch allen Speicherbänken zugeordnet ist, bietet dies ein gewisses Maß an Flexibilität. Beachten Sie außerdem, dass das Lesen aus dem ROM deaktiviert ist, während das Schreiben aktiviert ist. Das bedeutet, dass wir aus dem RAM „unter“ dem ROM lesen können, während das ROM aktiv ist.

Mein empfohlenes Programmierverfahren besteht darin, mit Video-RAM-Adressen in das ROM zu schreiben. Das ROM könnte jedoch mit Adressen in Bank 1 (&4000-&7fff) schreiben, wenn dieser Speicherbereich keine aussagekräftigen Daten enthält. (Wenn sich die zu schreibenden Daten bereits in diesem Adressbereich befinden, kann der Programmierer die Daten einfach lesen (RAM) und dann an derselben Adresse schreiben (ROM). Bei Befehlen, die an das ROM gesendet werden, wie diesen, ist jedoch Vorsicht geboten werden weiterhin Daten darunter verwerfen).

Lesen Sie das RAM-Byte an der zu programmierenden Adresse.

Schalten Sie die Schreibfreigabe für das ROM ein

Schreiben Sie die benötigten Daten in das ROM.

Schalten Sie die Schreibfreigabe für das ROM aus

Schreiben Sie die Originaldaten zurück in das ROM.

Das ROM (NORFLASH) kann bis zu 31 ROMs plus das Firmware-ROM enthalten. Beim Programmieren des Chips muss die Firmware in Steckplatz 31 (beginnend bei Adresse &7c000) eingefügt werden. BASIC (falls installiert) muss in Steckplatz 0 (Adresse &00000) eingefügt werden. ROM-Slots befinden sich alle &4000 Bytes, also &00000, &04000, &08000, &0C000, &10000 usw.

Beim Brennen von ROMs mit der XGPro-Software:

Verwenden Sie „IC auswählen“, um den verwendeten IC auszuwählen (SST39FS040).

Klicken Sie auf die Schaltfläche „LOAD“ in der Symbolleiste.

Wählen Sie die zu ladende Datei aus.

Dateiformat: Binär (für .ROM-Dateien)

In die Region: Standard

Lademodus: Normal

Ab Dateistartadresse: 0000

To Buffer Start Addr: Die Startadresse des ROM-Steckplatzes (&7C000 für die Firmware, &00000 für BASIC)

Puffer beim Laden der Datei löschen: Die Option „Puffer mit Standard löschen“ überschreibt alle zuvor geladenen Daten! Verwenden Sie dies für das erste ROM, das in XGPro geladen wird (wodurch das gesamte ROM initialisiert wird). Für alle anderen ROMs wählen Sie „Deaktivieren“ (wodurch Daten nur in den ausgewählten Steckplatz geladen werden).

Klicken Sie auf „OK“ und vergewissern Sie sich, dass Ihre Datei(en) an die richtige(n) Adresse(n) geladen und nicht überschrieben wurden.

Klicken Sie auf PROG (Symbolleiste).

Klicken Sie auf Programm.

Auf dieser Platine sind das Gate-Array und der Videoausgang untergebracht.

Bei JP901 sind die DISPEN- und HSYNC-Signale im Vergleich zu denen auf dem entsprechenden Header auf der RAM-Steuerplatine vertauscht. Dies lässt sich am besten auf der RAM-Control-Platine beheben (siehe unten).

Der Videoausgangsschaltkreis ist der des CPC464, aber irgendwie habe ich die Komponentenwerte des CPC6128 verwendet, jedoch ohne die Kondensatoren des 6128. Das macht wahrscheinlich keinen wesentlichen Unterschied.

In meinen Tests verwende ich denselben SCART-zu-HDMI-Adapter, den ich normalerweise für Amstrads verwende, aber hier wird ein Schwarzweißbild oder überhaupt kein Bild angezeigt. Dies scheint ein Problem zwischen dem vom Kabel verwendeten Netzteil und dem Adapter zu sein. Das Problem kann behoben werden, indem dem Kabel von der CPC-Modularplatine 5 V Strom zugeführt wird.

Die Platine enthält Footprints für die Gate-Arrays 40007 und 40010 (und ein 40008 sollte auch funktionieren). Die Stellflächen überlappen sich, um Platz zu sparen. Sie sollten in der Lage sein, Steckdosen für beide zu integrieren, indem Sie die beiden Stiftreihen trennen und das dazwischen liegende Gewebe entfernen. Allerdings liegen die Grundflächen etwas zu nahe beieinander, als dass dies problemlos möglich wäre.

Die Löcher im Footprint für die DIN-Buchse sind etwas zu klein.

Dieses Board beherbergt die Verbindung zwischen dem Videodatenbus und dem CPU-Datenbus, verarbeitet die Signale, um sie für den SRAM-Speicher geeignet zu machen, und beherbergt die optionalen Komponenten, die für Speicher größer als 64 KB (ungetestet) erforderlich sind.

Die Schaltungsansteuerung /RAMOE ist falsch. Um das Problem zu beheben:

Schneiden Sie die Leiterbahn zwischen den U192-Pins 1 und 13 ab

Schneiden Sie die Leiterbahn zwischen U192 Pin 11 und U193 Pin 1 ab

Installieren Sie einen Draht zwischen U192 Pin 1 und U195 Pin 9

Installieren Sie einen Draht zwischen U195 Pin 8 und U193 Pin 1

Wie bei der Videoplatine erwähnt, sind die DISPEN- und HSYNC-Pins an den Anschlüssen zwischen den Platinen vertauscht. Um dies zu beheben:

Schneiden Sie die Leiterbahn zwischen J1 Pin 2 und J2 Pin 2 ab

Schneiden Sie die Leiterbahn zwischen J1 Pin 3 und J2 Pin 3 ab

Installieren Sie einen Draht zwischen J1 Pin 2 und J2 Pin 3

Installieren Sie einen Draht zwischen J1 Pin 3 und J2 Pin 2

Um <= 64 KB RAM zu verwenden, installieren Sie die Links LK5, LK6 und LK7. Wenn ja, fügen Sie IC118 und U194 NICHT ein

Um mehr als 64 KB RAM zu verwenden, lassen Sie LK5, LK6, LK7 offen und installieren Sie IC118 und U194. IC118 ist ein Standard-Amstrad-HAL/PAL.

Die richtige Schaltung zum Ansteuern von /RAMOE ist:

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

In Textform: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD kann von U195 Pin 8 bezogen werden.

Dieses Board beherbergt den 6845 CRTC, Adressmultiplexer und 512 KB SRAM. Hier gibt es keine Probleme und es ist keine Konfiguration erforderlich.

Bei Bedarf können Header für CURSOR und LPEN installiert werden. Das sind sie wahrscheinlich nicht.

Auf dieser Platine sind das 8255 PIO und die Bandschnittstelle untergebracht. Um die I/O-Adresse konfigurierbar zu machen, sind Lötverbindungen und Jumper angebracht:

Die Platine wurde so konzipiert, dass die E/A-Platine „über/vor“ ihr montiert werden kann, aber das Relais ist dafür zu hoch. Daher würde ich empfehlen, J902 auf der Rückseite der Platine zu montieren (dies ist der Anschluss zur Soundplatine).

Auf der Rückseite der Platine finden Sie die Lötverbindungen direkt über den Adressstiften. Auf jeder Verbindung müssen Sie das „hohe“ Adresspad (beschriftet mit A7 (sic) bis A15) mit dem zentralen Pad verlöten. Die „niedrigen“ Adresspads (A0..A7) dürfen NICHT mit den mittleren Pads verbunden werden.

Auf der Vorderseite der Platine finden Sie die Verbindungen zwischen U1 und D302. Sie müssen den „Low“-Link (zum mittleren Pin) für den Link mit der Bezeichnung A3 und den High-Link (zum mittleren Pin) für die anderen (A2, A4, A5, A6, A7) überbrücken.

Finden Sie die Verbindungen zwischen C315 und J901. Sie konfigurieren, welche Signale an die Klinkenbuchsen und welche an die Backplane geleitet werden. Das empfohlene Setup ist:

Installieren Sie Verbindungen zwischen dem INT (ernal) und den mittleren Pins für TO, TI und /MO (Tape Out, Tape In und Motor).

Lassen Sie den Link /EXP geöffnet.

J901 ermöglicht den Zugriff auf verschiedene 8255-Eingangssignale. Standardmäßig verfügen alle diese Zeilen über Pull-Ups und können ignoriert werden.

RG0, RG1, RG2 sind die Regionseinstellungen.

VHz ist die 50Hz/60Hz-Einstellung für die Videoausgabe.

/EXP ist das /EXP-Signal.

PBSY ist das Drucker-Besetzt-Signal. Der CPC Modular verfügt über keinen parallelen Port. Dieses Signal kann bei Bedarf zur Erweiterung genutzt werden.

J1, J2 und J3 sind die Tape-I/O-Buchsen. J3 (Motor) sollte eine 2,5-mm-Klinkenbuchse sein, der Platzbedarf ist jedoch für eine 3,5-mm-Buchse ausgelegt.

Auf dieser Platine sind der Klanggenerator AY-3-8910 und die zugehörigen Ausgänge sowie die Tastatur- und Joystick-Anschlüsse untergebracht.

Wie für die E/A-Platine erwähnt: Sie sollten den Interboard-Anschluss (J902) oben auf dieser Platine montieren, nicht auf der Rückseite, wie im Siebdruck gezeigt.

Das Board verfügt über die Möglichkeit, einen integrierten Oszillator für den Takteingang des AY zu verwenden. Im CPC Modular: Lassen Sie X1 weg und installieren Sie einen Jumper am CLK2-Ende von JP3 (der die Platine so konfiguriert, dass sie das Taktsignal vom Gate-Array verwendet, das über die Rückwandplatine gesendet wird).

Mit den Jumpern über J103 (Audioausgangsbuchse) können verschiedene Audiosignale an verschiedene Backplane-Pins gesendet werden. In den meisten Fällen können diese offen gelassen werden. Beachten Sie, dass es bei einigen Einstellungen zu Konflikten mit Bandsignalen kommen kann, die über die Rückwandplatine auf der E/A-Karte geleitet werden.

Wenn eine Audio-Buchse installiert ist, werden die Signale LINKS und RECHTS NICHT an die Rückwandplatine gesendet (falls dafür konfiguriert – siehe vorheriger Punkt). Der Audio-MIX wird jedoch weiterhin gesendet (falls so konfiguriert).

CP2 ist der Tastaturanschluss. Dies verwendet die gleiche Pinbelegung wie das ursprüngliche Amstrad CPC464 (PCB-Tastatur).

J102 ist der Joystick-Anschluss. Der Stecker ist hier etwas zu „innen“ montiert und könnte eine Platine im nächsten Sockel kurzschließen.

HAL/PAL:

Code für Original: https://www.cpcwiki.eu/index.php/PAL16L8

WiP-Ersatz: https://github.com/Bread80/GreenHAL

WiP-Ersatz: https://www.cpcwiki.eu/forum/index.php?msg=231084

Gate-Array:

WiP FPGA-basierter Ersatz: https://github.com/codedchip/AMSGateArray

ROM-Bilder: https://www.cpcwiki.eu/index.php/ROM_List

Lizenz: CERN-OHL-P

Urheberrecht © Mike Sutton, 2023

Website: https://bread80.com

Soziale Medien (Mastodon): https://mstdn.social/@bread80

Dahinter gibt es nichts Nützliches. Aber wenn Sie es bis hierher geschafft haben, werden Sie wahrscheinlich trotzdem weitermachen.

TX/RX=Ton (Links, rechts) **Jumpered (optional) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC (Video zu IO) USR4=

/WAIT=READY (es ist bereits!) CLOCK2=/CPU_ADDR (RAM-Board; 1 MHz Takt für Sound) RX2=Tape in **Jumpered (optional) TX2=Tape out **Jumpered (optional) USR5=RAMDIS MOVED USR6=/ RAMRD MOVED USR7=Motor **Jumpered (optional)

D8-D15=Videobus

D8-D15=IO-Bus ???Steuersignale???

Position = Obere Lochreihe @ 45,72 mm über der Mitte der grundlegenden RC2014-Stiftleisten, Pins ganz links = Mittelpunkt zwischen A9 und A8 Pin 1 nach rechts 1 GND 2 HSYNC (in) 3 DISPEN (in) 4 GND 5 /RAS ( aus) 6 /CAS (aus) 7 /MWE (aus) 8 /CCLK (aus) 9 /244EN (aus) 10 GND

Position = Obere Lochreihe @ 43,18 mm über der Mitte der verlängerten Stiftleisten, Stifte ganz links = Mittelpunkt zwischen den Stiften D2 und D3. Stift 1 links, alle Erdungen in der obersten Reihe. 1=GND 2=HSYNC (Eingang) 3=DISPEN (Eingang) 4=/CCLK (Ausgang) 5=/XCPU_ADDR (Ausgang) 6=/RAMCS (Ausgang) 7=GND 8=/RAMOE (Ausgang) 9=GND 10 =/RAMWE (aus) 11=RAMA14 (aus) 12=RAMA15 (aus) 13=RAMA16 (aus) 14=RAMA17 (aus) 15=GND 16=RAMA18 (aus)

1=GND 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=GND

Amstrad/MX4-Pinbelegung

GND SOUND Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK READY Y Y BRST RSET Y? Ja? Ja? Ja? Ja? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS CURSOR Y LPEN Y EXP Y Y GND CLK4 Y Y

Extra (Video-RAM): RD7..RD0 Y Y J RAS Y Y CAS Y Y MWE Y Y 244EN Y Y

Extra (Video-RAM und IO-Sound): CPU_ADDR(1MHz) Y Y Y VSYNC Y Y Y (2 Zeilen)

Extra (IO-Sound): PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y LINKS Y RECHTS Y (20 Zeilen)

Disc: Intern sind ca. 14 Zeilen erforderlich

Video/RAM: 50 + 24 + 2 = 76 Zeilen! gesamt. Weniger nicht benötigt: 69 insgesamt (70 plus ein Ersatz!) IO/Sound: 50 + 20 + 2 = insgesamt 72 Zeilen. Weniger Unnötiges: insgesamt 50 (inkl. ein paar Ersatzzeilen) Disc: 50 + 14 = insgesamt 64 Zeilen

Hinweise: 76-poliger Kantenstecker: Platinenbreite = 99,06 mm

Platinen: MX4-Abschnitt: CPU-ROM-Ersatzteile RC2014 Edge-Anschluss

Videoabschnitt (Gate-Array): Video-RAM-RAM-Steuerung

Videobereich (RP2040): Videosignale RAM-Transceiver

Disc-Bereich: Controller-Anschlüsse/Puffer

IO-Sound-Bereich: PPI AY Tape Audio-Verstärker/Mixer