***Este proyecto es un trabajo inacabado en progreso. ¡Actualmente tiene errores y no se han probado todas las funciones!

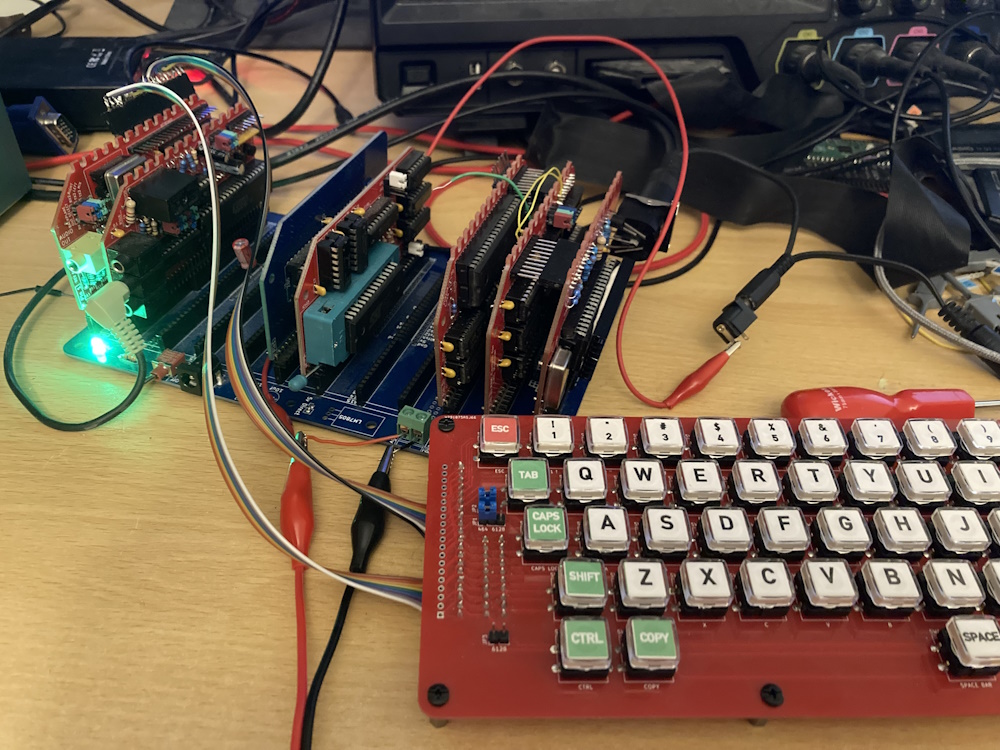

Los módulos actuales están diseñados para adaptarse a un backplane RC2014 Pro ligeramente modificado. En el texto siguiente explicaré el estado actual del proyecto, las soluciones necesarias para ponerlo en funcionamiento y los detalles básicos de compilación. Debido al estado del trabajo en progreso del proyecto, este documento será intencionalmente conciso.

El proyecto utiliza un conector/enchufe de clavija para conectar módulos dentro de los subsistemas (el subsistema de video-RAM y el subsistema de sonido IO). Esto requiere un cabezal de clavija más largo de lo habitual.

Este es un backplane RC2014 Pro ligeramente modificado. El CPC Modular utiliza las líneas D8 a D15 tanto dentro del subsistema de video-RAM como del subsistema IO-Sound para buses de datos locales. Por lo tanto:

Deberá cortar las líneas D8 a D15 entre estas secciones.

Este es un "Módulo de CPU Z80" RC2014 ligeramente modificado. Modificación:

Será necesario reemplazar las resistencias de la placa con un valor diferente. 2,2 k ohmios deberían funcionar bien.

Esta placa contiene NORFLASH de 512Kb. Incluye circuitos para permitir que el flash se queme in situ (no probado). Configuración:

Es necesario instalar un puente que puentee el pin 2 de LK4 y el pin 2 de LK5.

Para habilitar la grabación flash, instale los enlaces LK1, LK2 y LK3. De lo contrario déjelo abierto.

Mis notas para escribir en Flash (tomada del archivo esquemático) son:

!!! No hay forma de desactivar las escrituras en memoria en el sistema CPC estándar. Por lo tanto, CUALQUIER escritura de memoria que hagamos en la ROM mientras WRITE_EN está activo también escribirá en la RAM.

Sin embargo, dado que la ROM se asigna a todos y cada uno de los bancos de memoria, esto agrega cierta flexibilidad. También tenga en cuenta que la lectura desde la ROM está deshabilitada mientras la escritura está habilitada. Esto significa que podemos leer desde la RAM 'debajo' de la ROM mientras la ROM está activa.

Mi procedimiento de programación recomendado es escribir en la ROM usando direcciones de RAM de video; sin embargo, la ROM podría escribir usando direcciones en el banco 1 (&4000-&7fff) si ese rango de memoria no contiene datos significativos. (Si los datos a escribir ya están en este rango de direcciones, entonces el programador puede simplemente leer los datos (RAM) y luego escribir (ROM) en la misma dirección. Sin embargo, se debe tener cuidado con los comandos enviados a la ROM, ya que estos aún eliminará los datos que se encuentran debajo).

Lea el byte de RAM en la dirección a programar.

Active la habilitación de escritura para la ROM

Escriba los datos necesarios en la ROM.

Desactive la habilitación de escritura para la ROM

Vuelva a escribir los datos originales en la ROM.

La ROM (NORFLASH) puede contener hasta 31 ROMS más la ROM del firmware. Al programar el chip, el firmware debe ir a la ranura 31 (comenzando en la dirección &7c000). BASIC (si está instalado) debe ir a la ranura 0 (dirección &00000). Las ranuras de ROM están ubicadas cada &4000 bytes, es decir, &00000, &04000, &08000, &0C000, &10000, etc.

Si graba ROM con el software XGPro:

Utilice Seleccionar IC para seleccionar el IC que se está utilizando (SST39FS040).

Haga clic en el botón CARGAR de la barra de herramientas.

Seleccione el archivo para cargar.

Formato de archivo: Binario (para archivos .ROM)

A región: predeterminado

Modo de carga: Normal

Desde la dirección de inicio del archivo: 0000

A la dirección de inicio del búfer: la dirección de inicio de la ranura ROM (&7C000 para el firmware, &00000 para BASIC)

Borrar el búfer al cargar el archivo: ¡La opción 'Borrar el búfer con el valor predeterminado' sobrescribirá cualquier dato cargado previamente! Úselo para la primera ROM cargada en XGPro (que inicializará toda la ROM). Para todas las demás ROM, seleccione 'Desactivar' (lo que cargará datos sólo en la ranura seleccionada).

Haga clic en Aceptar y verifique que sus archivos se hayan cargado en las direcciones correctas y no se hayan sobrescrito.

Haga clic en PROG (barra de herramientas)

Haga clic en Programa.

Esta placa alberga el conjunto de puertas y la salida de vídeo.

En JP901, las señales DISPEN y HSYNC se intercambian en comparación con las del encabezado equivalente en la placa RAM-Control. Esto se soluciona mejor en la placa RAM-Control (ver más abajo).

El circuito de salida de video es el del CPC464 pero, de alguna manera, he usado valores de componentes del CPC6128 pero menos los capacitores del '6128. Probablemente esto no haga una diferencia significativa.

En mis pruebas estoy usando el mismo adaptador SCART a HDMI que normalmente uso para Amstrads pero aquí muestra una imagen en blanco y negro, o ninguna imagen. Esto parece ser un problema entre la fuente de alimentación utilizada por el cable y el adaptador. Se puede arreglar alimentando 5V al cable desde la placa modular CPC.

La placa incluye huellas para los conjuntos de puertas 40007 y 40010 (y un 40008 también debería funcionar). Las huellas se superponen para ahorrar espacio. Debería poder incluir enchufes para ambos separando las dos filas de clavijas y quitando las correas entre ellas; sin embargo, las huellas están demasiado juntas para hacerlo fácilmente.

Los agujeros en la huella para el conector DIN son un poco pequeños.

Esta placa alberga el enlace entre el bus de datos de vídeo y el bus de datos de la CPU, masajea las señales para hacerlas adecuadas para la memoria SRAM y alberga los componentes opcionales necesarios para memorias superiores a 64k (no probado).

El circuito de conducción /RAMOE es incorrecto. Para solucionarlo:

Cortar el rastro entre los pines 1 y 13 de U192.

Cortar el rastro entre el pin 11 de U192 y el pin 1 de U193.

Instale un cable entre el pin 1 de U192 y el pin 9 de U195.

Instale un cable entre el pin 8 de U195 y el pin 1 de U193.

Como se señaló para la placa de video, los pines DISPEN y HSYNC se intercambian en los conectores entre las placas. Para solucionar esto:

Cortar el rastro entre J1 pin 2 y J2 pin 2

Cortar el rastro entre J1 pin 3 y J2 pin 3

Instale un cable entre J1 pin 2 y J2 pin 3

Instale un cable entre J1 pin 3 y J2 pin 2

Para utilizar <= 64k RAM, instale los enlaces LK5, LK6 y LK7. Si es así NO inserte IC118 y U194

Para usar > 64k RAM, deje LK5, LK6, LK7 abiertos e instale IC118 y U194. IC118 es un Amstrad HAL/PAL estándar.

El circuito correcto para conducir /RAMOE es:

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

En forma de texto: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD puede obtenerse del pin 8 de U195.

Esta placa alberga el 6845 CRTC, multiplexores de direcciones y SRAM de 512 Kb. No hay problemas aquí y no es necesaria ninguna configuración.

Se pueden instalar encabezados para CURSOR y LPEN si es necesario. Probablemente no lo sean.

Esta placa alberga el 8255 PIO y la interfaz de cinta. Se instalan puentes y enlaces de soldadura para que la dirección de E/S sea configurable:

La placa se diseñó de manera que la placa IO pudiera montarse "encima/delante de ella", pero el relé es demasiado alto para permitirlo. Por lo tanto: te recomiendo que montes J902 en la parte trasera de la placa (este es el conector a la placa de sonido).

En la parte posterior de la placa, encuentre los enlaces de soldadura justo encima de los pines de dirección. En cada enlace, debe soldar el panel de direcciones "alto" (etiquetado como A7(sic) a A15) al panel central. Los teclados de direcciones 'bajos' (A0..A7) NO deben conectarse a los teclados centrales.

En el frente del tablero encuentre los enlaces ubicados entre U1 y D302. Debe conectar el enlace 'bajo' (al pin central) para el enlace etiquetado como A3 y el enlace alto (al pin central) para los demás (A2, A4, A5, A6, A7).

Encuentre los enlaces ubicados entre C315 y J901. Esto configura qué señales se dirigen a los conectores jack y cuáles al backplane. La configuración recomendada es:

Instale enlaces entre los pines INT (ernal) y medio para TO, TI y /MO (Salida de cinta, Entrada de cinta y Motor).

Deje abierto el enlace /EXP.

J901 permite el acceso a varias señales de entrada del 8255. Por defecto, todas estas líneas tienen pull-ups y se pueden ignorar.

RG0, RG1, RG2 son la configuración de región.

VHz es la configuración de 50 Hz/60 Hz para la salida de vídeo.

/EXP es la señal /EXP.

PBSY es una señal de impresora ocupada. El CPC Modular no incluye puerto paralelo. Esta señal se puede utilizar para expansión si se desea.

J1, J2 y J3 son los conectores de E/S de cinta. J3 (Motor) debe ser un conector jack de 2,5 mm, pero el tamaño es para un conector jack de 3,5 mm.

Esta placa alberga el generador de sonido AY-3-8910 y las salidas asociadas, además de los conectores de teclado y joystick.

Como se indicó para la placa IO: debe montar el conector entre placas (J902) en la parte superior de esta placa, no en la parte trasera como se muestra en la serigrafía.

La placa tiene la capacidad de utilizar un oscilador integrado para la entrada de reloj del AY. En CPC Modular: omita X1 e instale un puente en el extremo CLK2 de JP3 (que configura la placa para usar la señal de reloj del conjunto de puertas enviada a través del backplane).

Los puentes sobre J103 (conector de salida de audio) permiten enviar varias señales de audio a una variedad de pines del backplane. En la mayoría de los casos, estos se pueden dejar abiertos. Tenga en cuenta que algunas de las configuraciones pueden entrar en conflicto con las señales de cinta enrutadas a través del backplane de la placa IO.

Si se instala un conector de audio, las señales IZQUIERDA y DERECHA NO se enviarán al backplane (si está configurado para hacerlo; consulte el elemento anterior). Sin embargo, la MEZCLA de audio se seguirá enviando (si está configurada así).

CP2 es el conector del teclado. Utiliza el mismo pinout que el Amstrad CPC464 original (teclado PCB).

J102 es el conector del joystick. El conector aquí está montado demasiado "hacia adentro" y podría provocar un cortocircuito en una PCB en el siguiente zócalo.

HAL/PAL:

Código original: https://www.cpcwiki.eu/index.php/PAL16L8

Reemplazo de WiP: https://github.com/Bread80/GreenHAL

Reemplazo de WiP: https://www.cpcwiki.eu/forum/index.php?msg=231084

Matriz de puertas:

Reemplazo basado en WiP FPGA: https://github.com/codedchip/AMSGateArray

Imágenes ROM: https://www.cpcwiki.eu/index.php/ROM_List

Licencia: CERN-OHL-P

Copyright © Mike Sutton, 2023

Sitio web: https://bread80.com

Redes sociales (Mastodon): https://mstdn.social/@bread80

No hay nada útil más allá de aquí. Pero si has llegado hasta aquí, probablemente seguirás adelante de todos modos.

TX/RX=Sonido (Izquierda, Derecha) **Puenteado (opcional) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC (Video a IO) USR4=

/WAIT=READY (¡ya lo está!) CLOCK2=/CPU_ADDR (placa RAM; reloj de 1MHz para sonido) RX2=Entrada de cinta **Con puente (opcional) TX2=Salida de cinta **Con puente (opcional) USR5=RAMDIS MOVED USR6=/ RAMRD MOVED USR7=Motor **Puertado (opcional)

D8-D15=Bus de vídeo

D8-D15=bus IO??? ¿Señales de control???

Posición = Fila superior de orificios a 45,72 mm por encima del centro de los pines del cabezal RC2014 básico, pines más a la izquierda = punto medio entre A9 y A8 Pin 1 a la derecha 1 GND 2 HSYNC (pulg.) 3 DISPEN (pulg.) 4 GND 5 /RAS ( salida) 6 /CAS (salida) 7 /MWE (salida) 8 /CCLK (salida) 9 /244EN (salida) 10 GND

Posición = Fila superior de orificios a 43,18 mm por encima del centro de los pasadores del cabezal extendido, Pasadores más a la izquierda = punto medio entre los pasadores D2 y D3. Pasador 1 a la izquierda, todas las conexiones a tierra en la fila superior. 1=GND 2=HSYNC (entrada) 3=DISPEN (entrada) 4=/CCLK (salida) 5=/XCPU_ADDR (salida) 6=/RAMCS (salida) 7=GND 8=/RAMOE (salida) 9=GND 10 =/RAMWE (fuera) 11=RAMA14 (fuera) 12=RAMA15 (fuera) 13=RAMA16 (fuera) 14=RAMA17 (fuera) 15=GND 16=RAMA18 (fuera)

1=TIERRA 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=TIERRA

Configuración de pines de Amstrad/MX4

GND SONIDO Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK LISTO Y Y BRST RSET Y? ¿Y? ¿Y? ¿Y? ¿Y? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS CURSOR Y LPEN Y EXP Y Y GND CLK4 Y Y

Extra (Video-RAM): RD7..RD0 Y Y Y RAS Y Y CAS Y Y MWE Y Y 244EN Y Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y (24 líneas)

Extra (Video-RAM e IO-Sound): CPU_ADDR(1MHz) Y Y Y VSYNC Y Y Y (2 líneas)

Extra (IO-Sound): PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y LEFT Y RIGHT Y (20 líneas)

Disco: Se requieren aproximadamente 14 líneas internamente

Vídeo/RAM: 50 + 24 + 2 = 76 líneas. total. Menos innecesario: 69 en total (¡70 más uno de repuesto!) IO/Sonido: 50 + 20 + 2 = 72 líneas en total. Menos innecesario: 50 en total (incluye un par de repuestos) Disco: 50 + 14 = 64 líneas en total

Notas: Conector de borde de 76 pines: ancho de la placa = 99,06 mm

Placas: Sección MX4: CPU ROM Repuesto(s) Conector RC2014 Edge

Sección de vídeo (matriz de puertas): Control de RAM de vídeo

Sección de vídeo (RP2040): Transceptor RAM de señales de vídeo

Sección de disco: conectores/búferes del controlador

Sección de sonido IO: amplificador/mezclador de audio en cinta PPI AY