***Ce projet est un travail inachevé en cours. Il contient actuellement des bugs et toutes les fonctionnalités n'ont pas été testées !

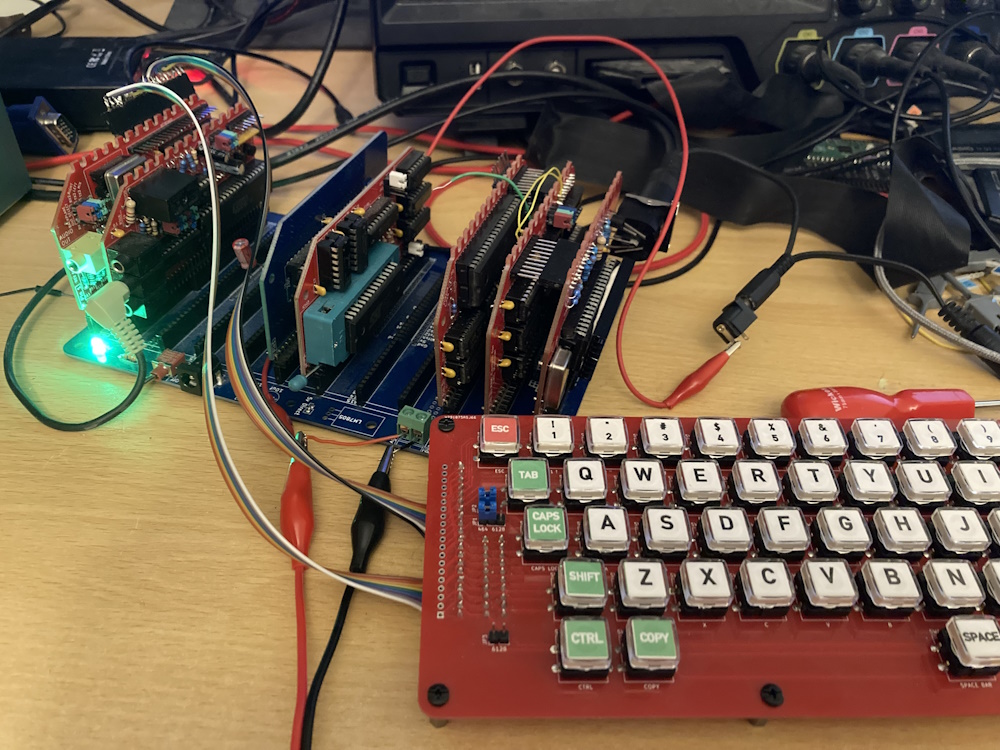

Les modules actuels sont conçus pour s'adapter à un fond de panier RC2014 Pro légèrement modifié. Dans le texte ci-dessous, j'expliquerai l'état actuel du projet, les solutions de contournement nécessaires pour le faire fonctionner et les détails de base de la construction. En raison de l'état d'avancement du projet, ce document sera intentionnellement concis.

Le projet utilise un en-tête/prise à broches pour connecter des modules au sein de sous-systèmes (le sous-système vidéo-RAM et le sous-système IO-son). Cela nécessite un en-tête de broche plus long que d'habitude.

Il s'agit d'un fond de panier RC2014 Pro légèrement modifié. Le CPC Modular utilise les lignes D8 à D15 à la fois dans le sous-système vidéo-RAM et dans le sous-système IO-Sound pour les bus de données locaux. Donc:

Vous devrez couper les lignes D8 à D15 entre ces sections.

Il s'agit d'un "Module CPU Z80" RC2014 légèrement modifié. Modification:

Les résistances de la carte devront être remplacées par une valeur différente. 2,2k ohms devraient bien fonctionner.

Cette carte contient 512 Ko de NORFLASH. Il comprend des circuits permettant de graver le flash in situ (non testé). Configuration :

Un cavalier doit être installé pour relier la broche 2 de LK4 et la broche 2 de LK5.

Pour activer la gravure flash, installez les liens LK1, LK2 et LK3. Sinon laissez ouvert.

Mes notes pour écrire dans Flash (extraites du fichier schématique) sont :

!!! Il n'existe aucun moyen de désactiver les écritures en mémoire sur le système CPC standard. Par conséquent, TOUTE mémoire écrite que nous effectuons dans la ROM pendant que WRITE_EN est actif écrira également dans la RAM.

Cependant, étant donné que la ROM correspond à toutes les banques de mémoire, cela ajoute une certaine flexibilité. Notez également que la lecture depuis la ROM est désactivée tandis que l'écriture est activée. Cela signifie que nous pouvons lire dans la RAM « sous » la ROM pendant que la ROM est active.

Ma procédure de programmation recommandée consiste à écrire dans la ROM en utilisant les adresses RAM vidéo, mais la ROM peut écrire en utilisant les adresses de la banque 1 (&4000-&7fff) si cette plage de mémoire ne contient pas de données significatives. (Si les données à écrire se trouvent déjà dans cette plage d'adresses, le programmeur peut simplement lire les données (RAM) puis écrire (ROM) à la même adresse. Il faut cependant être prudent avec les commandes envoyées à la ROM, car celles-ci supprimera toujours les données en dessous).

Lire l'octet RAM à l'adresse à programmer.

Activez l'activation de l'écriture pour la ROM

Écrivez les données nécessaires dans la ROM.

Désactivez l'activation de l'écriture pour la ROM

Écrivez les données originales dans la ROM.

La ROM (NORFLASH) peut contenir jusqu'à 31 ROM plus la ROM du firmware. Lors de la programmation de la puce, le micrologiciel doit être inséré dans l'emplacement 31 (en commençant à l'adresse &7c000). BASIC (s'il est installé) doit être placé dans l'emplacement 0 (adresse &00000). Les emplacements ROM sont situés tous les &4000 octets, c'est-à-dire &00000, &04000, &08000, &0C000, &10000 etc.

Si vous gravez des ROM avec le logiciel XGPro :

Utilisez Select IC pour sélectionner le IC utilisé (SST39FS040).

Cliquez sur le bouton CHARGER de la barre d'outils.

Sélectionnez le fichier à charger.

Format de fichier : binaire (pour les fichiers .ROM)

Vers la région : par défaut

Mode de chargement : Normal

À partir de l'adresse de début du fichier : 0000

To Buffer Start Addr : l'adresse de début de l'emplacement ROM (&7C000 pour le micrologiciel, &00000 pour BASIC)

Effacer le tampon lors du chargement du fichier : L'option "Effacer le tampon par défaut" écrasera toutes les données précédemment chargées ! Utilisez-le pour la première ROM chargée dans XGPro (qui initialisera la ROM entière). Pour toutes les autres ROM, sélectionnez « Désactiver » (ce qui chargera les données uniquement dans l'emplacement sélectionné).

Cliquez sur OK et vérifiez que vos fichiers ont été chargés à la ou aux bonnes adresses et n'ont pas été écrasés.

Cliquez sur PROG (barre d'outils)

Cliquez sur Programme.

Cette carte abrite le gate array et la sortie vidéo.

Sur le JP901, les signaux DISPEN et HSYNC sont inversés par rapport à ceux de l'en-tête équivalent sur la carte RAM-Control. Il est préférable de résoudre ce problème sur la carte RAM-Control (voir ci-dessous).

Le circuit de sortie vidéo est celui du CPC464 mais, d'une manière ou d'une autre, j'ai utilisé les valeurs des composants du CPC6128 mais sans les condensateurs du '6128. Cela ne fait probablement pas une différence significative.

Lors de mes tests, j'utilise le même adaptateur SCART vers HDMI que j'utilise normalement pour Amstrads, mais ici, il affiche une image en noir et blanc, ou aucune image du tout. Cela semble être un problème entre le bloc d'alimentation utilisé par le câble et l'adaptateur. Il peut être réparé en alimentant le câble en 5 V à partir de la carte modulaire CPC.

La carte comprend des empreintes pour les réseaux de portes 40007 et 40010 (et un 40008 devrait également fonctionner). Les empreintes se chevauchent pour économiser de l'espace. Vous devriez pouvoir inclure des prises pour les deux en séparant les deux rangées de broches et en retirant la sangle entre elles. Cependant, les empreintes sont un peu trop rapprochées pour le faire facilement.

Les trous dans l'empreinte pour la prise DIN sont un peu trop petits.

Cette carte héberge le lien entre le bus de données vidéo et le bus de données du CPU, masse les signaux pour les rendre adaptés à la mémoire SRAM et héberge les composants optionnels requis pour les mémoires supérieures à 64 Ko (non testées).

Le circuit de pilotage /RAMOE est incorrect. Pour le réparer :

Couper la trace entre les broches U192 1 et 13

Couper la trace entre la broche 11 de l'U192 et la broche 1 de l'U193

Installez un fil entre la broche 1 de l'U192 et la broche 9 de l'U195.

Installez un fil entre la broche 8 de l'U195 et la broche 1 de l'U193.

Comme indiqué pour la carte vidéo, les broches DISPEN et HSYNC sont inversées sur les connecteurs entre les cartes. Pour résoudre ce problème :

Coupez la trace entre la broche 2 de J1 et la broche 2 de J2

Coupez la trace entre la broche 3 de J1 et la broche 3 de J2

Installez un fil entre la broche 2 de J1 et la broche 3 de J2

Installer un fil entre la broche 3 de J1 et la broche 2 de J2

Pour utiliser <= 64 Ko de RAM, installez les liens LK5, LK6 et LK7. Si c'est le cas, NE PAS insérer IC118 et U194

Pour utiliser > 64 Ko de RAM, laissez LK5, LK6, LK7 ouverts et installez IC118 et U194. IC118 est un Amstrad HAL/PAL standard.

Le circuit correct pour piloter /RAMOE est :

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

Sous forme de texte : /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD peut provenir de la broche 8 de l'U195.

Cette carte abrite le 6845 CRTC, des multiplexeurs d'adresses et une SRAM de 512 Ko. Il n'y a aucun problème ici et aucune configuration n'est nécessaire.

Des en-têtes peuvent être installés pour CURSOR et LPEN si nécessaire. Ce n’est probablement pas le cas.

Cette carte abrite le 8255 PIO et l'interface bande. Des liens de soudure et des cavaliers sont installés pour rendre l'adresse d'E/S configurable :

La carte a été conçue de telle sorte que la carte IO puisse être montée « au-dessus/devant » d'elle, mais le relais est trop haut pour permettre cela. Ainsi : je vous recommande de monter le J902 à l'arrière de la carte (c'est le connecteur de la carte son).

À l'arrière de la carte, trouvez les liens de soudure juste au-dessus des broches d'adresse. Sur chaque maillon, vous devez souder le plot d'adresse « haut » (étiqueté A7(sic) à A15) au plot central. Les plages d'adresses « basses » (A0..A7) ne doivent PAS être connectées aux plages centrales.

Sur le recto du plateau retrouvez les liens situés entre U1 et D302. Vous devez relier le lien « bas » (à la broche centrale) pour le lien étiqueté A3 et le lien haut (à la broche centrale) pour les autres (A2, A4, A5, A6, A7).

Retrouvez les liens situés entre C315 et J901. Configurez les signaux dirigés vers les prises jack et ceux dirigés vers le fond de panier. La configuration recommandée est la suivante :

Installez des liens entre les broches INT (ernales) et centrales pour TO, TI et /MO (Tape Out, Tape In et Motor).

Laissez le lien /EXP ouvert.

J901 permet d'accéder à divers signaux d'entrée 8255. Par défaut, toutes ces lignes ont des pull-ups et peuvent être ignorées.

RG0, RG1, RG2 sont les paramètres de région.

VHz est le paramètre 50 Hz/60 Hz pour la sortie vidéo.

/EXP est le signal /EXP.

PBSY est un signal d'imprimante occupée. Le CPC Modular n'inclut pas de port parallèle. Ce signal peut être utilisé pour l'expansion si vous le souhaitez.

J1, J2 et J3 sont les prises E/S de la bande. J3 (moteur) doit être une prise jack 2,5 mm mais l'empreinte est pour une prise 3,5 mm.

Cette carte abrite le générateur de son AY-3-8910 et les sorties associées, ainsi que les connecteurs du clavier et du joystick.

Comme indiqué pour la carte IO : vous devez monter le connecteur inter-carte (J902) sur le dessus de cette carte, et non à l'arrière comme indiqué sur la sérigraphie.

La carte a la capacité d'utiliser un oscillateur intégré pour l'entrée d'horloge de l'AY. Dans le CPC Modular : omettez X1 et installez un cavalier à l'extrémité CLK2 de JP3 (qui configure la carte pour utiliser le signal d'horloge du réseau de portes envoyé via le fond de panier).

Les cavaliers au-dessus de J103 (prise de sortie audio) permettent d'envoyer divers signaux audio à diverses broches du fond de panier. Dans la plupart des cas, ceux-ci peuvent rester ouverts. Notez que certains paramètres peuvent entrer en conflit avec les signaux de bande acheminés via le fond de panier de la carte IO.

Si une prise audio est installée, les signaux GAUCHE et DROITE ne seront PAS envoyés au fond de panier (si configuré pour le faire - voir l'élément précédent). Cependant, le MIX audio sera toujours envoyé (si configuré ainsi).

CP2 est le connecteur du clavier. Celui-ci utilise le même brochage que l'Amstrad CPC464 d'origine (clavier PCB).

J102 est le connecteur du joystick. Le connecteur ici est monté un peu trop « à l'intérieur » et pourrait court-circuiter un PCB dans la prise suivante.

HAL/PAL :

Code pour l'original : https://www.cpcwiki.eu/index.php/PAL16L8

Remplacement WiP : https://github.com/Bread80/GreenHAL

Remplacement WiP : https://www.cpcwiki.eu/forum/index.php?msg=231084

Réseau de portes :

Remplacement basé sur WiP FPGA : https://github.com/codedchip/AMSGateArray

Images ROM : https://www.cpcwiki.eu/index.php/ROM_List

Licence : CERN-OHL-P

Droits d'auteur © Mike Sutton, 2023

Site Web : https://bread80.com

Réseaux sociaux (Mastodon) : https://mstdn.social/@bread80

Il n'y a rien d'utile au-delà d'ici. Mais si vous êtes arrivé jusqu’ici, vous continuerez probablement quand même.

TX/RX=Son (Gauche, droite) **Cavalier (facultatif) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC (Vidéo vers IO) USR4=

/WAIT=READY (c'est déjà le cas !) CLOCK2=/CPU_ADDR (carte RAM ; horloge 1 MHz pour le son) RX2=Tape in **Jumped (facultatif) TX2=Tape out **Jumped (facultatif) USR5=RAMDIS MOVED USR6=/ RAMRD MOVED USR7=Moteur **Cavalé (facultatif)

D8-D15=Bus vidéo

D8-D15=Bus IO ???Signaux de commande???

Position = rangée supérieure de trous à 45,72 mm au-dessus du centre des broches d'embase RC2014 de base, broches les plus à gauche = point médian entre A9 et A8 Broche 1 à droite 1 GND 2 HSYNC (po) 3 DISPEN (po) 4 GND 5 /RAS ( sortie) 6 /CAS (sortie) 7 /MWE (sortie) 8 /CCLK (sortie) 9 /244EN (sortie) 10 GND

Position = rangée supérieure de trous à 43,18 mm au-dessus du centre des broches d'embase étendues, broches les plus à gauche = point médian entre les broches D2 et D3, broche 1 vers la gauche, toutes les masses sur la rangée la plus haute. 1=GND 2=HSYNC (entrée) 3=DISPEN (entrée) 4=/CCLK (sortie) 5=/XCPU_ADDR (sortie) 6=/RAMCS (sortie) 7=GND 8=/RAMOE (sortie) 9=GND 10 =/RAMWE (sortie) 11=RAMA14 (sortie) 12=RAMA15 (sortie) 13=RAMA16 (sortie) 14=RAMA17 (sortie) 15=GND 16=RAMA18 (sortie)

1=GND 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=GND

Brochage Amstrad/MX4

GND SOUND Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y O Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK READY Y Y BRST RSET Y? Oui ? Oui ? Oui ? Oui ? ROMEN Y ROMDIS O RAMRD O O RAMDIS CURSOR O LPEN O EXP O O GND CLK4 O O

Extra (Vidéo-RAM) : RD7..RD0 Y Y Y RAS Y Y CAS Y Y MWE Y Y 244EN O Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y (24 lignes)

Extra (Vidéo-RAM et IO-Sound) : CPU_ADDR (1 MHz) Y Y Y VSYNC O Y Y (2 lignes)

Extra (IO-Sound) : PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y LEFT Y RIGHT Y (20 lignes)

Disque : environ 14 lignes requises en interne

Vidéo/RAM : 50 + 24 + 2 = 76 lignes ! total. Moins inutile : 69 au total (70 plus une de rechange !) IO/Sound : 50 + 20 + 2 = 72 lignes au total. Moins inutile : 50 au total (y compris quelques pièces de rechange) Disque : 50 + 14 = 64 lignes au total

Remarques : connecteur de bord à 76 broches : largeur de la carte = 99,06 mm

Cartes : Section MX4 : CPU ROM de rechange(s) Connecteur RC2014 Edge

Section vidéo (gate array) : Vidéo RAM RAM Control

Section vidéo (RP2040) : émetteur-récepteur RAM de signaux vidéo

Section disque : connecteurs/tampons du contrôleur

Section sonore IO : ampli/mixeur audio à bande PPI AY