Repo ini mengimplementasikan kumpulan komponen terkait Ethernet di Bluespec SystemVerilog(BSV) untuk pemrosesan paket berkinerja tinggi pada FPGA. Secara khusus, repo ini menyediakan modul untuk menghasilkan dan mengurai paket UDP/IP/Ethernet. Unit pemrosesan ARP dengan cache non-pemblokiran yang menyimpan informasi alamat juga disediakan untuk menangani resolusi alamat MAC secara otomatis. Selain membangun tumpukan UDP/IP/Ethernet standar, blue-ethernet menambahkan dukungan untuk RoCE(RDMA over Converged Ethernet): 1) mengintegrasikan pembuatan dan verifikasi ICRC(Invariant Cyclic Redundancy) dalam pemrosesan paket UDP/IP; 2) menyediakan modul untuk menangani PFC (Priority Flow Control) untuk mewujudkan transmisi jaringan lossless. Dan terakhir modul konversi antarmuka juga disediakan untuk generator paket dan parser untuk berinteraksi dengan Xilinx 100G Ethernet Subsystem (CMAC).

Beberapa direktori utama repo ini ditunjukkan di bawah ini:

├── lib # external libraries/repos

│ ├── blue-crc # high-performance CRC hardware implementation

│ └── blue-wrapper # BSV wrappers for generating ready-to-use Verilog interface

├── scripts # scripts used to build project

├── src # design source files

│ └── includes # files containing some commonly-used BSV types and modules

├── syn # scripts for vivado synthesis and implementation

└── test # source files for verification

├── bluesim # testbenches based on bluesim

├── cocotb # python testbenches based on cocotb

└── vivado # co-simulation with cmac using vivadoBerikut adalah daftar beberapa file sumber penting:

./src

├── ArpCache.bsv # Cache implementation storing MAC addresses got from ARP

├── ArpProcessor.bsv # processing unit handling ARP requests and responses

├── includes

│ ├── CompletionBuf.bsv

│ ├── ContentAddressMem.bsv

│ ├── EthernetTypes.bsv # numeric and struct types about protocol definition

│ ├── PortConversion.bsv # interface conversion modules used to generate ready-to-use Verilog

│ ├── Ports.bsv # numeric and struct types about in/output ports of modules

│ ├── RFile.bsv

│ ├── StreamHandler.bsv # modules implemented for manipulating data stream

│ └── EthUtils.bsv # utility functions and modules

├── MacLayer.bsv # generator and parser for Ethernet packet

├── PfcUdpIpArpEthRxTx.bsv # generator and parser for UDP/IP/Ethernet packet with PFC

├── PriorityFlowControl.bsv # modules handling PFC

├── UdpIpArpEthRxTx.bsv # generator and parser for UDP/IP/Ethernet packet

├── UdpIpEthRx.bsv # parser for UDP/IP/Ethernet packet

├── UdpIpEthTx.bsv # generator for UDP/IP/Ethernet packet

├── UdpIpLayer.bsv # parser and generator for UDP/IP packet

├── UdpIpLayerForRdma.bsv # parser and generator for UDP/IP packet with support for RoCE

└── XilinxCmacRxTxWrapper.bsv # bridge modules between parser/generator and Xilinx CMACBagian ini memberikan penjelasan rinci tentang beberapa komponen penting yang diterapkan di blue-ethernet, termasuk fungsionalitas, antarmuka, dan arsitektur perangkat kerasnya.

Apa yang dilakukan komponen perangkat keras terkait Ethernet pada dasarnya adalah serangkaian manipulasi aliran. Generator paket bertanggung jawab untuk memasukkan aliran header ke aliran muatan utama untuk menghasilkan aliran paket lengkap. Sebaliknya, yang dilakukan parser adalah mengekstrak aliran header dan aliran payload dari aliran paket. Sedangkan untuk menambahkan checksum untuk sebuah paket, aliran paket diteruskan ke kalkulator CRC dan kemudian nilai output CRC ditambahkan ke bagian ekor aliran paket.

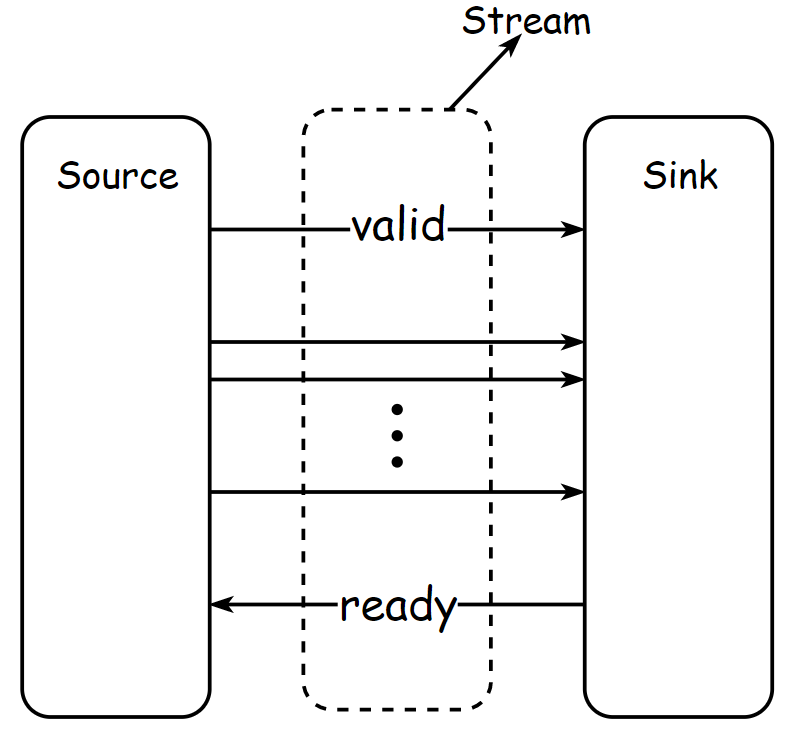

Entitas perangkat keras yang terkait dengan aliran yang kami sebutkan di sini sebenarnya adalah sekelompok sinyal data yang dilindungi oleh pasangan sinyal kontrol yang valid dan siap pakai. Sinyal yang valid menunjukkan bahwa komponen sumber ingin mentransfer data. Dan ready menandakan bahwa sink sudah siap menerima data dari sumber. Transfer antara sumber dan sink hanya berhasil jika valid dan ready bernilai tinggi. Jika ukuran data yang akan dikirim lebih besar dari ukuran satu transfer, maka data perlu dipecah-pecah dan dikirim dalam serangkaian transfer.

Bagian pemrosesan aliran yang paling rumit dan rawan kesalahan adalah tentang cara menangani sinyal kontrol siap-valid dari berbagai aliran. Di BSV, manipulasi sinyal kontrol diimplementasikan oleh kompiler dan tidak terlihat di tingkat tata bahasa, yang membantu desainer fokus pada logika pemrosesan aliran.

Sinyal data yang digunakan untuk mentransfer aliran paket antar komponen yang berbeda dienkapsulasi dalam struktur DataStream , yang mencakup sinyal data 256-bit, sinyal pengaktifan byte 32-bit, dua sinyal Boolean menunjukkan apakah transfer ini adalah yang terakhir atau pertama dari aliran paket.

typedef 256 DATA_BUS_WIDTH ;

typedef TDiv # ( DATA_BUS_WIDTH , 8 ) DATA_BUS_BYTE_WIDTH ;

typedef Bit # ( DATA_BUS_WIDTH ) Data ;

typedef Bit # ( DATA_BUS_BYTE_WIDTH ) ByteEn ;

typedef struct {

Data data ;

ByteEn byteEn ;

Bool isFirst ;

Bool isLast ;

} DataStream deriving ( Bits , Bounded , Eq , FShow ) ; module mkAppendDataStreamHead # (

IsSwapEndian swapDataStream ,

IsSwapEndian swapAppendData ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( dType ) appendDataIn

)( FifoOut # ( DataStream )) ; module mkAppendDataStreamTail # (

IsSwapEndian swapDataStream ,

IsSwapEndian swapAppendData ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( dType ) appendDataIn ,

FifoOut # ( Bit # ( streamLenWidth )) streamLengthIn

)( FifoOut # ( DataStream )) ; interface ExtractDataStream # ( type dType ) ;

interface FifoOut # ( dType ) extractDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkExtractDataStreamHead # (

FifoOut # ( DataStream ) dataStreamIn

)( ExtractDataStream # ( dType )) ;Modul dalam paket UdpIpLayer diimplementasikan untuk menghasilkan dan mengurai paket UDP/IP.

Generator paket mengambil UdpIpMetaData yang berisi informasi header UDP/IP dan aliran muatan serta keluaran aliran paket UDP/IP lengkap. Pengurai paket bekerja dengan cara sebaliknya dengan mengekstraksi UdpIpMetaData dan aliran muatan dari aliran paket UDP/IP.

typedef struct {

UdpLength dataLen ; # The Length of payload data

IpAddr ipAddr ; # Desitnation IP address

IpDscp ipDscp ; # DSCP field used for PFC

IpEcn ipEcn ; # ECN field

UdpPort dstPort ; # Destination port number

UdpPort srcPort ; # Source port number

} UdpIpMetaData ;Sinyal yang dienkapsulasi dalam struct UdpIpMetaData tidak mencakup semua bidang yang ditentukan dalam header UDP/IP. Beberapa bidang header ditetapkan untuk perangkat jaringan tertentu, yang dienkapsulasi dalam struct UdpConfig dan perlu dikonfigurasi sebelum mengirim atau menerima paket apa pun. Dan beberapa bidang lainnya bersifat konstan dan terkodekan dalam komponen perangkat keras.

typedef struct {

EthMacAddr macAddr ; # Source MAC address

IpAddr ipAddr ; # Source IP address

IpNetMask netMask ; # IP netmask

IpGateWay gateWay ; # IP gateway

} UdpConfig ; module mkUdpIpStream # (

UdpConfig udpConfig ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( UdpIpMetaData ) udpIpMetaDataIn ,

function UdpIpHeader genHeader ( UdpIpMetaData meta , UdpConfig udpConfig , IpID ipId )

)( FifoOut # ( DataStream )) ; interface UdpIpMetaDataAndDataStream ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkUdpIpMetaDataAndDataStream # (

UdpConfig udpConfig ,

FifoOut # ( DataStream ) udpIpStreamIn ,

function UdpIpMetaData extractMetaData ( UdpIpHeader hdr )

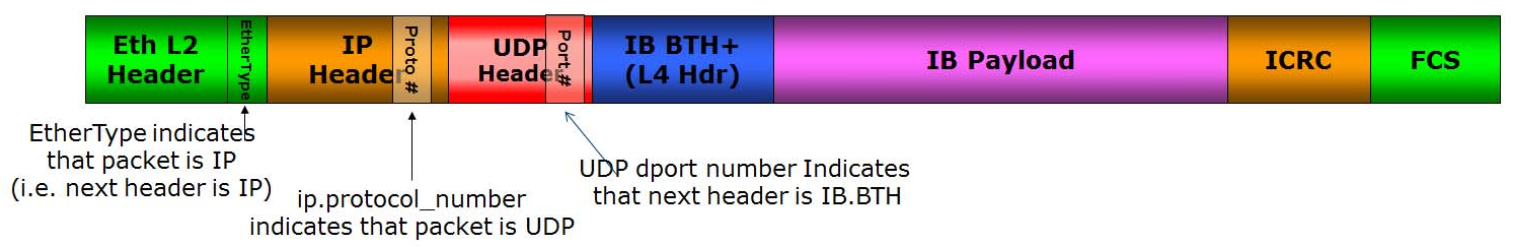

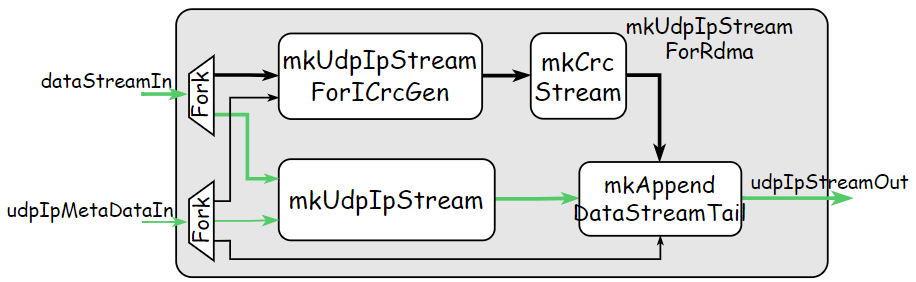

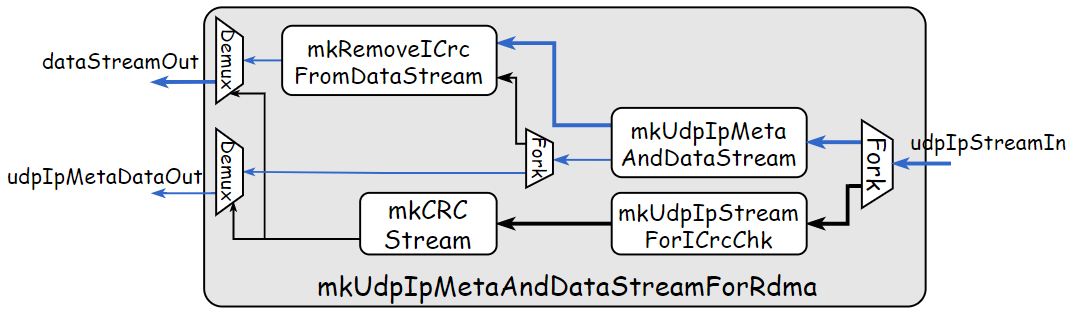

)( UdpIpMetaDataAndDataStream ) ; Modul dalam paket UdpIpLayerForRdma diimplementasikan berdasarkan UdpIpLayer dengan dukungan untuk RoCE(RDMA over Converged Ethernet). Fungsionalitas tambahan yang ditambahkan untuk mendukung RoCE adalah pembuatan dan verifikasi ICRC (Invariant CRC) yang diperlukan untuk paket RoCE. Format paket RoCE didefinisikan sebagai berikut:

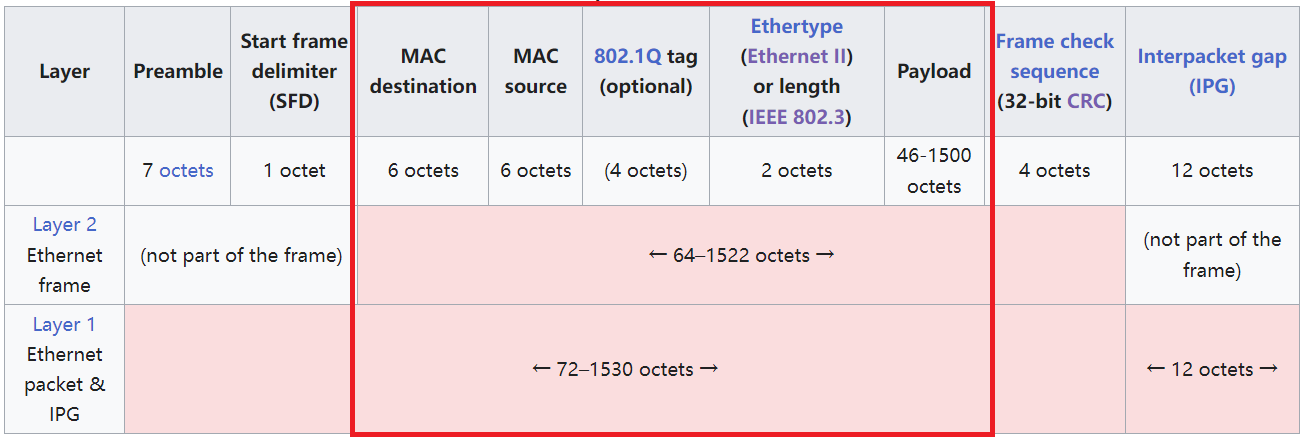

Modul dalam paket MacLayer diimplementasikan untuk menghasilkan dan menguraikan paket Ethernet. Generator memasukkan header Ethernet ke kepala aliran paket UDP/IP untuk menghasilkan aliran paket Ethernet. Parser mengekstrak header Ethernet dan aliran paket UDP/IP dari aliran paket Ethernet.

Informasi header yang digunakan untuk menghasilkan paket Ethernet ditentukan dalam struktur MacMetaData .

typedef struct {

EthMacAddr macAddr ; # Destination MAC address

EthType ethType ; # Type of Ethernet frame

} MacMetaData deriving ( Bits , Eq , FShow ) ;Perlu diperhatikan, paket Ethernet yang ditangani di MacLayer hanya mencakup bidang yang diuraikan dalam kotak merah pada gambar di bawah. Bidang lain dibiarkan diproses oleh Xilinx CMAC IP.

module mkMacStream # (

FifoOut # ( DataStream ) udpIpStreamIn ,

FifoOut # ( MacMetaData ) macMetaDataIn ,

UdpConfig udpConfig

)( FifoOut # ( DataStream )) ; interface MacMetaDataAndUdpIpStream ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface FifoOut # ( DataStream ) udpIpStreamOut ;

endinterface

module mkMacMetaDataAndUdpIpStream # (

FifoOut # ( DataStream ) macStreamIn ,

UdpConfig udpConfig

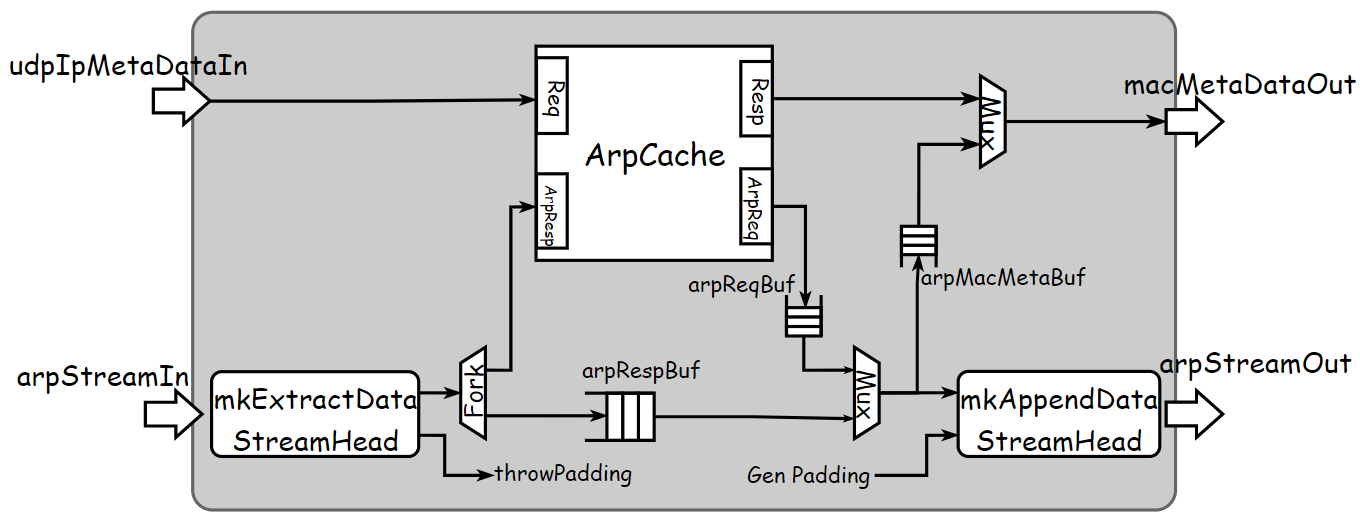

)( MacMetaDataAndUdpIpStream ) ; Protokol Resolusi Alamat (ARP) digunakan untuk menemukan alamat MAC yang terkait dengan alamat IP tertentu. Di blue-ethernet, modul mkArpProcessor diimplementasikan untuk pemrosesan ARP, yang mengintegrasikan generator paket ARP, parser, dan modul mkArpCache yang menyimpan alamat MAC.

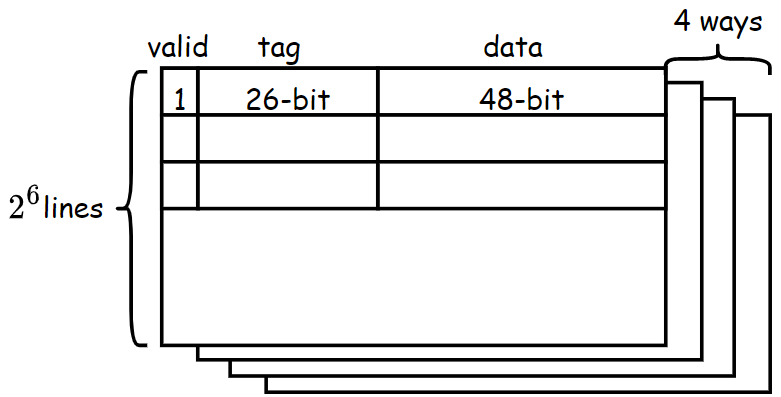

Untuk cache yang digunakan dalam pemrosesan ARP, alamat IP 32-bit sesuai dengan alamat cache dan alamat MAC 48-bit sesuai dengan data cache. Susunan default array memori untuk cache ARP ditunjukkan di bawah ini, yaitu struktur asosiatif set 4 arah, setiap jalur berisi 64 baris dan setiap baris menyertakan valid 1-bit, tag 26-bit, dan data 48-bit. Ukuran total konfigurasi array default ini adalah sekitar 1,2 KB. Didukung untuk mengubah ukuran array memori dengan mengatur jumlah baris dan cara. Berdasarkan susunan memori ini, cache dirancang agar tidak memblokir, mendukung permintaan luar biasa (beberapa permintaan dalam penerbangan) dan menggunakan algoritma pseudo-LRU untuk penggantian baris cache.

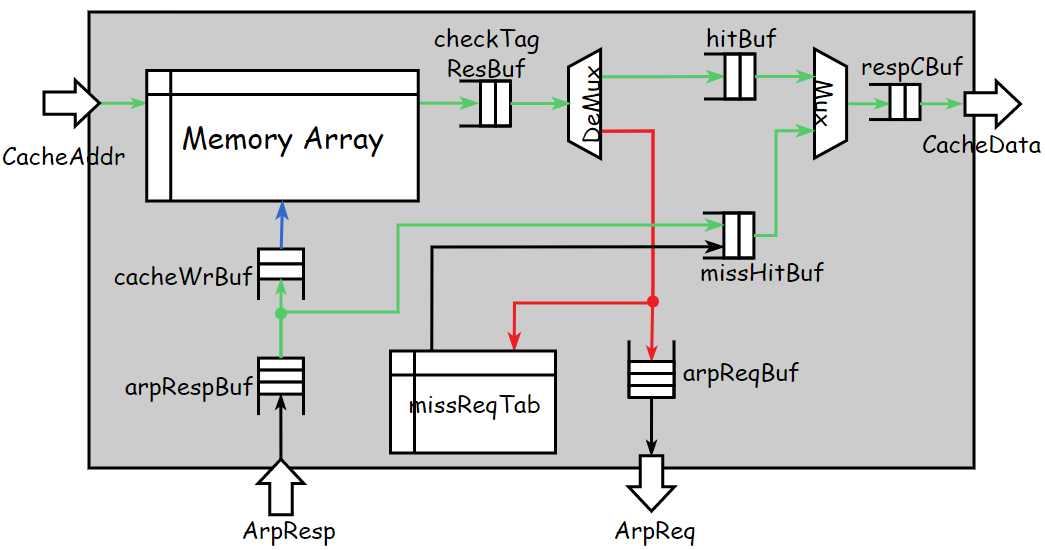

Definisi antarmuka dan diagram struktur modul mkArpCache yang disederhanakan ditunjukkan di bawah ini. ArpCache memiliki dua subinterface: cacheServer menangani interaksi dengan komponen layanan resolusi alamat MAC; dan arpClient menangani interaksi dengan mkArpProcessor untuk memulai permintaan ARP dan mendapatkan alamat MAC dari respons ARP. Alur kerja dasar modul mkArpCache adalah sebagai berikut:

Ketika cache menerima permintaan baca, cache pertama-tama mencari array memori untuk mendapatkan semua tag dan data yang sesuai dengan alamat IP yang diberikan. Kemudian ia memeriksa tag untuk melihat apakah data yang kita perlukan disimpan di cache. Jika cache ditemukan, data yang diambil dikirim ke hitBuf . Atau alamat IP dikirim ke arpReqBuf untuk memulai permintaan ARP. Dan ketika respons ARP kembali, data dan informasi alamat yang dibawanya ditulis ke cacheWrBuf dan missHitBuf untuk memperbarui susunan memori dan mengembalikan respons baca cache.

interface ArpCache ;

interface Server # ( CacheAddr , CacheData ) cacheServer ;

interface Client # ( CacheAddr , ArpResp ) arpClient ;

endinterface

Bagian tersulit dari implementasi cache adalah mendukung fitur luar biasa, yaitu mendukung beberapa permintaan baca dalam penerbangan. Masalah yang disebabkan oleh luar biasa adalah bahwa waktu respons berbeda untuk setiap permintaan ARP dalam penerbangan, yang berarti bahwa permintaan yang terlambat mungkin menerima responsnya terlebih dahulu. Oleh karena itu diperlukan mekanisme penyusunan ulang untuk menjamin korespondensi antara alamat permintaan dan data respons ketika terjadi kehilangan cache. Untuk mewujudkan respons berurutan, buffer penyelesaian respCBuf dan memori beralamat konten missReqTab diintegrasikan dalam aliran data. Buffer penyelesaian berfungsi seperti FIFO dengan dukungan tambahan untuk fungsi reservasi. Sebelum operasi enqueue sebenarnya, pertama-tama kita dapat memesan pesanan di buffer penyelesaian. Dan operasi dequeue mengikuti urutan yang dicadangkan, tidak peduli urutan operasi enqueue yang sebenarnya. Untuk setiap permintaan baca, perintah dequeue dibalik di respCBuf setelah diterima. Dan karena permintaan ARP tidak dapat membawa informasi pesanan, missReqTab diimplementasikan untuk menyimpannya.

Modul ini dapat berperilaku sebagai klien dan server ARP. Sebagai server, prosesor perlu menghasilkan permintaan ARP jika alamat MAC IP target tidak diketahui dan kemudian menunggu respons ARP dari perangkat target. Sebagai klien, prosesor ARP menerima permintaan ARP dari perangkat lain dan mengirimkan kembali respons ARP dengan membawa alamat MAC-nya sendiri.

interface ArpProcessor ;

interface FifoOut # ( DataStream ) arpStreamOut ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface Put # ( UdpConfig ) udpConfig ;

endinterface

module mkArpProcessor # (

FifoOut # ( DataStream ) arpStreamIn ,

FifoOut # ( UdpIpMetaData ) udpIpMetaDataIn

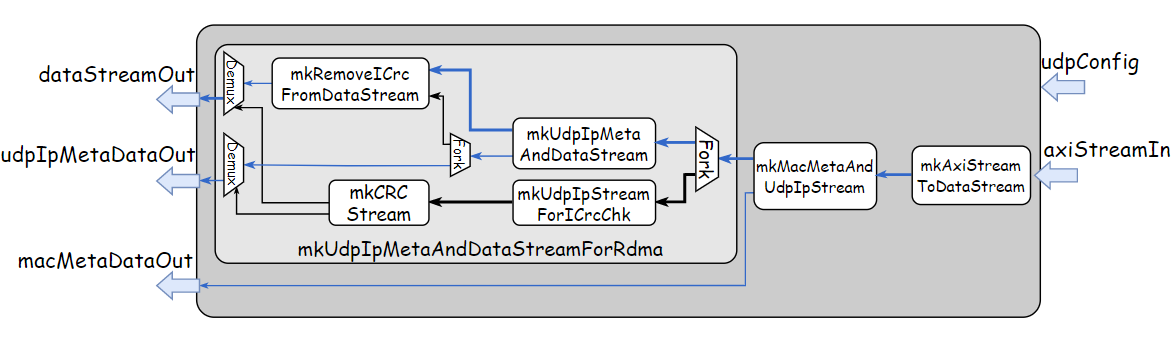

)( ArpProcessor ) ; Modul dalam paket UdpIpEthRx diimplementasikan untuk menerima dan mengurai paket UDP/IP/Ethernet.

interface UdpIpEthRx ;

interface Put # ( UdpConfig ) udpConfig ;

interface Put # ( AxiStream512 ) axiStreamIn ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkGenericUdpIpEthRx # ( Bool isSupportRdma )( UdpIpEthRx )

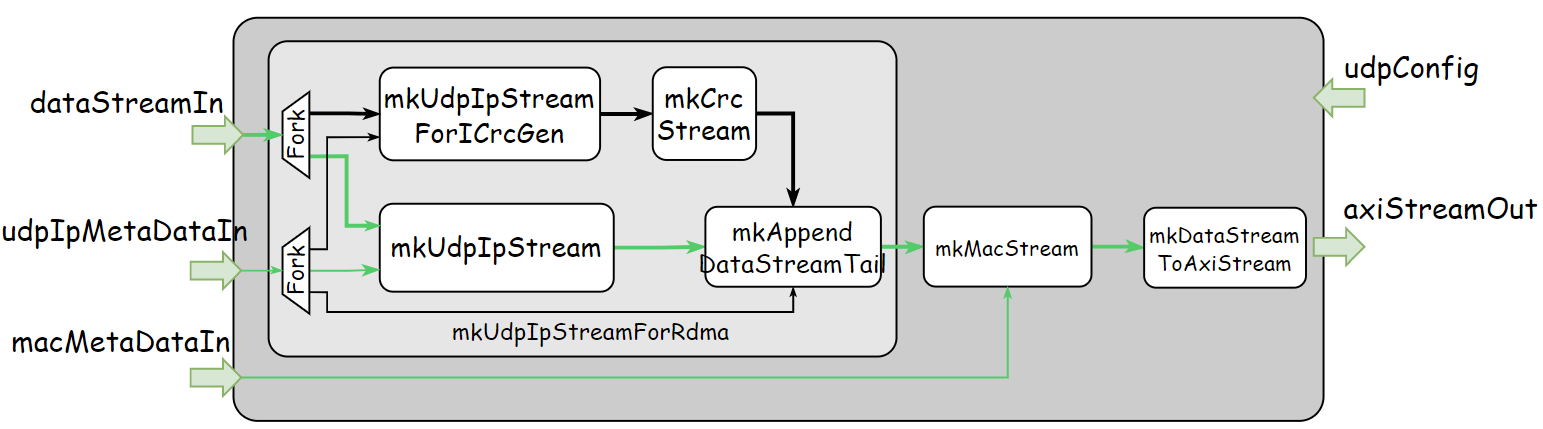

Modul dalam paket UdpIpEthTx diimplementasikan untuk menghasilkan dan mengirimkan paket UDP/IP/Ethernet.

interface UdpIpEthTx ;

interface Put # ( UdpConfig ) udpConfig ;

interface Put # ( UdpIpMetaData ) udpIpMetaDataIn ;

interface Put # ( MacMetaData ) macMetaDataIn ;

interface Put # ( DataStream ) dataStreamIn ;

interface AxiStream512FifoOut axiStreamOut ;

endinterface

module mkGenericUdpIpEthTx # ( Bool isSupportRdma )( UdpIpEthTx ) ;

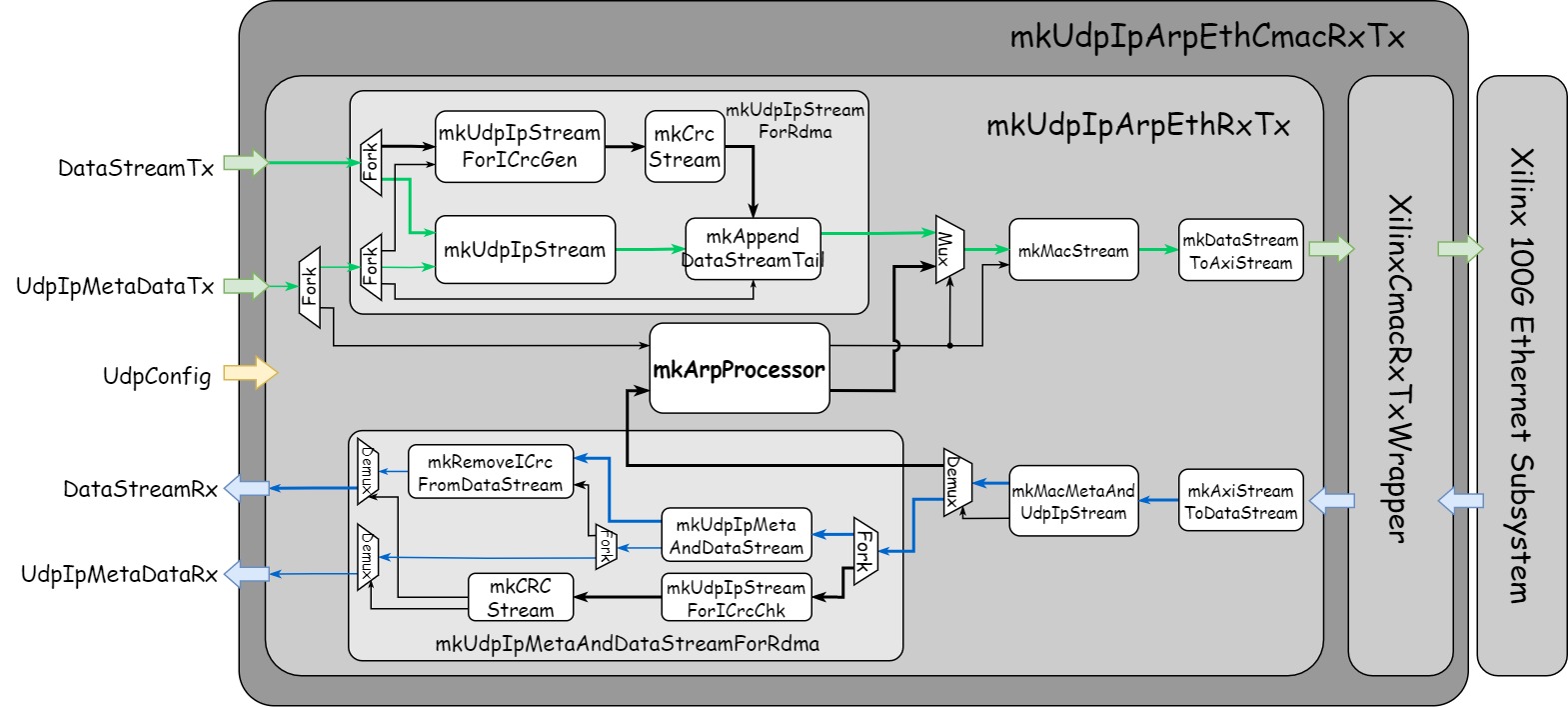

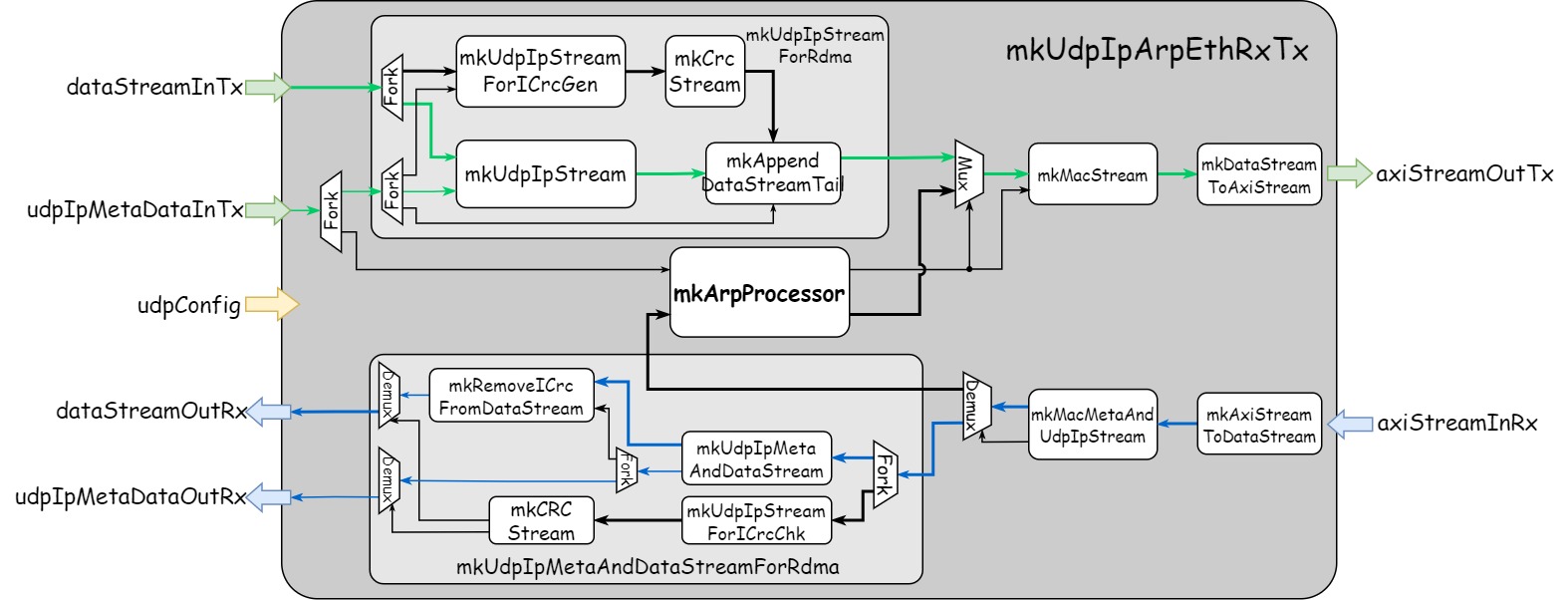

Modul yang disediakan dalam paket UdpIpArpEthRxTx dirancang untuk menerima dan mengirimkan paket UDP/IP/Ethernet serta menangani permintaan dan respons ARP pada saat yang bersamaan.

Modul ini dapat dibagi menjadi dua jalur aliran yang berlawanan, termasuk jalur transmisi dan jalur penerimaan:

Untuk jalur transmisi, dibutuhkan dataStreamInTx yang membawa aliran muatan dan udpIpMetaDataIn yang membawa aliran informasi header dan menghasilkan axiStreamOutTx yang membawa aliran paket UDP/IP/Ethernet. Tidak perlu menyediakan MacMetaData yang berisi informasi header Ethernet sebagai modul mkUdpIpEthTx , karena mkArpProcessor bertanggung jawab menangani resolusi alamat MAC dan menghasilkan informasi header Ethernet.

Untuk jalur penerimaan, cara kerjanya sebaliknya dengan mengekstraksi dataStreamOutRx yang membawa aliran payload dan udpIpMetaDataOutRx membawa aliran informasi header dari axiStreamInRx yang membawa aliran paket UDP/IP/Ethernet.

Generator dan parser paket Ethernet digunakan bersama oleh paket UDP/IP dan paket ARP, sehingga diperlukan Mux dan Demux tambahan di jalur transmisi dan penerimaan untuk arbitrase dan distribusi aliran. Parameter modul isSupportRdma menentukan apakah modul tersebut mendukung pemrosesan paket RoCE atau tidak. Jika dukungan untuk RDMA dinonaktifkan, kita hanya memerlukan mkUdpIpStream dan mkUdpIpMetaAndDataStream masing-masing di jalur transmisi dan penerimaan.

interface UdpIpArpEthRxTx ;

interface Put # ( UdpConfig ) udpConfig ;

// Tx

interface Put # ( UdpIpMetaData ) udpIpMetaDataInTx ;

interface Put # ( DataStream ) dataStreamInTx ;

interface AxiStream512FifoOut axiStreamOutTx ;

// Rx

interface Put # ( AxiStream512 ) axiStreamInRx ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOutRx ;

interface FifoOut # ( DataStream ) dataStreamOutRx ;

endinterface

module mkGenericUdpIpArpEthRxTx # ( Bool isSupportRdma )( UdpIpArpEthRxTx ) ;

Modul membungkus mkGenericUdpIpArpEthRxTx menggunakan modul yang disediakan dalam blue-wrapper sehingga menghasilkan antarmuka Verilog yang siap digunakan.

Modul ini mengintegrasikan modul mkGenericUdpIpArpEthRxTx dan modul mkXilinxCmacTxWrapper . Ini dirancang untuk berinteraksi dengan Xilinx CMAC IP untuk mengirim dan menerima paket UDP/IP/Ethernet ke dan dari media fisik.

Modul dalam paket PriorityFlowControl diimplementasikan untuk mewujudkan mekanisme kontrol aliran prioritas untuk memastikan transmisi jaringan tanpa kehilangan.

interface PriorityFlowControlTx ;

interface Get # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface Get # ( DataStream ) dataStreamOut ;

endinterface

module mkPriorityFlowControlTx # (

FifoOut # ( FlowControlReqVec ) flowControlReqVecIn ,

Vector # ( VIRTUAL_CHANNEL_NUM , DataStreamFifoOut ) dataStreamInVec ,

Vector # ( VIRTUAL_CHANNEL_NUM , UdpIpMetaDataFifoOut ) udpIpMetaDataInVec

)( PriorityFlowControlTx ) ;

interface PriorityFlowControlRx # (

numeric type bufPacketNum ,

numeric type maxPacketFrameNum ,

numeric type pfcThreshold

) ;

interface FifoOut # ( FlowControlReqVec ) flowControlReqVecOut ;

interface Vector # ( VIRTUAL_CHANNEL_NUM , Get # ( DataStream )) dataStreamOutVec ;

interface Vector # ( VIRTUAL_CHANNEL_NUM , Get # ( UdpIpMetaData )) udpIpMetaDataOutVec ;

endinterface

module mkPriorityFlowControlRx # (

DataStreamFifoOut dataStreamIn ,

UdpIpMetaDataFifoOut udpIpMetaDataIn

)( PriorityFlowControlRx # ( bufPacketNum , maxPacketFrameNum , pfcThreshold )) ;

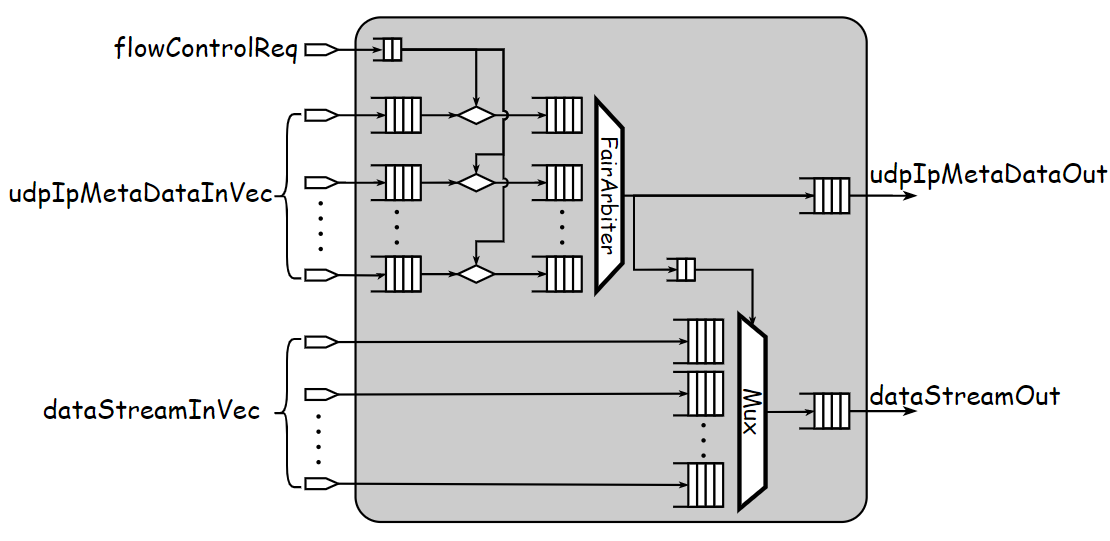

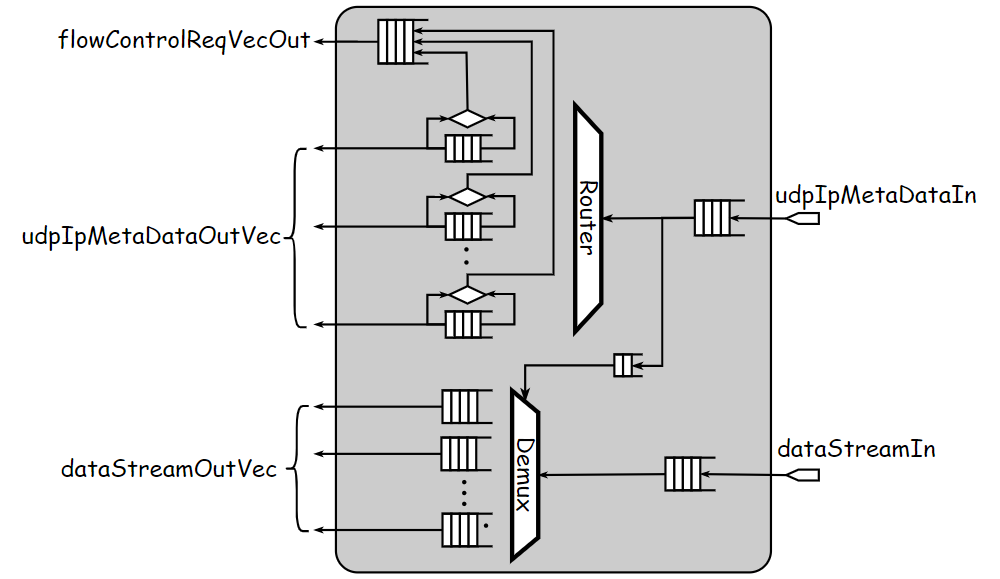

mkGenericPfcUdpIpArpEthRxTx mengintegrasikan mkPriorityFlowControlRx/Tx dan mkGenericUdpIpArpEthRxTx untuk menyediakan fungsionalitas pembuatan dan penguraian paket UDP/IP/Ethernet sekaligus mendukung kontrol aliran prioritas. Untuk transmisi paket, dibutuhkan delapan saluran aliran muatan dan informasi header UDP/IP, dan mengeluarkan satu aliran paket UDP/IP/Ethernet. Untuk penerimaan paket, dibutuhkan satu aliran paket UDP/IP/Ethernet dan merutekan header UDP/IP yang diekstraksi dan aliran muatan ke salah satu dari delapan saluran keluaran.

mkPfcUdpIpArpEthCmacRxTx mengintegrasikan modul mkGenericPfcUdpIpArpEthRxTx dan modul mkXilinxCmacTxWrapper . Ini dirancang untuk berinteraksi dengan Xilinx CMAC IP untuk mengirim dan menerima paket UDP/IP/Ethernet ke dan dari media fisik.

Sintesis dan implementasi modul utama mkGenericUdpIpArpEthRxTx dilakukan berdasarkan perangkat Xilinx xcvu9p menggunakan Vivado. Dan hasilnya menunjukkan bahwa rangkaian tersebut dapat mencapai frekuensi kerja 500MHz dan memberikan throughput puncak 128Gbps. Penggunaan sumber daya perangkat keras tercantum sebagai berikut:

CLB Logic

+----------------------------+-------+-------+------------+-----------+-------+

| Site Type | Used | Fixed | Prohibited | Available | Util % |

+----------------------------+-------+-------+------------+-----------+-------+

| CLB LUTs | 63886 | 0 | 0 | 1182240 | 5.40 |

| LUT as Logic | 41242 | 0 | 0 | 1182240 | 3.49 |

| LUT as Memory | 22644 | 0 | 0 | 591840 | 3.83 |

| LUT as Distributed RAM | 22644 | 0 | | | |

| LUT as Shift Register | 0 | 0 | | | |

| CLB Registers | 44099 | 0 | 0 | 2364480 | 1.87 |

| Register as Flip Flop | 44099 | 0 | 0 | 2364480 | 1.87 |

| Register as Latch | 0 | 0 | 0 | 2364480 | 0.00 |

| CARRY8 | 73 | 0 | 0 | 147780 | 0.05 |

| F7 Muxes | 194 | 0 | 0 | 591120 | 0.03 |

| F8 Muxes | 28 | 0 | 0 | 295560 | < 0.01 |

| F9 Muxes | 0 | 0 | 0 | 147780 | 0.00 |

+----------------------------+-------+-------+------------+-----------+-------+

BLOCKRAM

+-------------------+------+-------+------------+-----------+-------+

| Site Type | Used | Fixed | Prohibited | Available | Util % |

+-------------------+------+-------+------------+-----------+-------+

| Block RAM Tile | 4.5 | 0 | 0 | 2160 | 0.21 |

| RAMB36 / FIFO * | 4 | 0 | 0 | 2160 | 0.19 |

| RAMB36E2 only | 4 | | | | |

| RAMB18 | 1 | 0 | 0 | 4320 | 0.02 |

| RAMB18E2 only | 1 | | | | |

| URAM | 0 | 0 | 0 | 960 | 0.00 |

+-------------------+------+-------+------------+-----------+-------+Bagian ini memperkenalkan cara memulai proyek ini. Sebelum langkah lainnya, Anda harus terlebih dahulu menyiapkan lingkungan pengembangan dengan mengacu pada skrip setup.sh. Berikut adalah daftar dependensi:

Setelah menyiapkan lingkungan, kloning repo ini ke direktori tertentu. Di sini kami menyebut direktori ini sebagai BLUE_ETH:

git clone --recursive https://github.com/wengwz/blue-ethernet.git $( BLUE_ETH ) Ada tiga tingkat testbench berbeda yang disediakan di blue-ethernet:

# Specify TARGET to the name of target component

cd $( BLUE_ETH ) /test/bluesim

make TARGET=ArpCache # Run tests of UdpIpEthRx/Tx

# Enable/Disable support for RDMA by setting SUPPORT_RDAM to True/False

cd $( BLUE_ETH ) /test/cocotb

make cocotb TARGET=UdpIpEthTx SUPPORT_RDMA=TRUE

# Run simulation on virtual network

# Change NET_IFC in run_docker_net_test.sh to the name of your network card

cd $( BLUE_ETH ) /test/cocotb

docker build -f ./build_docker/Dockerfile -t ethernet-test ./build_docker

./run_docker_net_test.sh # Available TARGET includes UdpIpArpEthCmacRxTx/PfcUdpIpArpEthCmacRxTx

# Enable/Disable support for RDMA by setting SUPPORT_RDAM to True/False

cd $( BLUE_ETH ) /test/vivado

make sim TARGET=UdpIpArpEthCmacRxTx SUPPORT_RDMA=FalseSkrip yang digunakan untuk menjalankan sintesis dan implementasi desain disediakan di direktori $(BLUE_ETH)/syn.

# TARGET specifies the top module to be synthsized or implemented

# SUPPORT_RDMA specifies whether modules supports RoCE packet processing

# ONLYSYNTH decides whether or not run implemetation after synthesis

cd $( BLUE_ETH ) /syn

make vivado TARGET=UdpIpArpEthRxTx SUPPORT_RDMA=False ONLYSYNTH=0 # TARGET specifies the name of top module to be generated

# Specify SUPPORT_RDMA if needed

cd $( BLUE_ETH ) /test/cocotb

make verilog TARGET=UdpIpEthTx SUPPORT_RDMA=TRUEbsc -p +: $( BLUE_ETH ) /src: $( BLUE_ETH ) /src/includes ...Implementasi blue-ethernet melibatkan penggunaan perpustakaan eksternal berikut: