CATATAN:

Dokumentasi untuk proyek ini sedang diperbarui untuk mencerminkan perubahan pada Caravel versi baru yang didesain ulang.

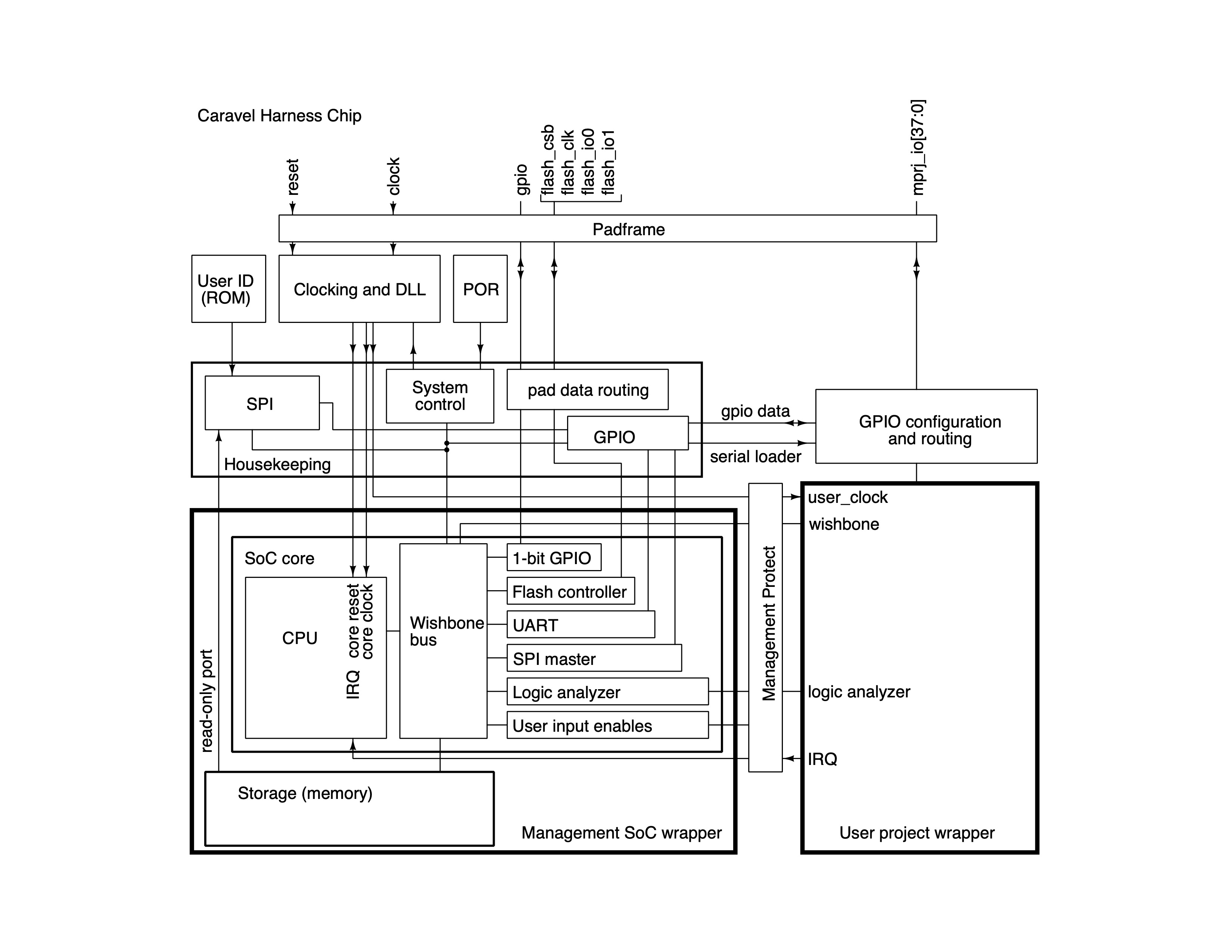

Caravel adalah SoC templat untuk Efabless Open MPW dan angkutan chipIgnite berdasarkan node Sky130 dari SkyWater Technologies. Arsitektur SoC saat ini diberikan di bawah ini.

Lembar data dan dokumentasi terperinci ada di sini

Caravel terdiri dari bingkai harness ditambah dua pembungkus untuk modul drop-in untuk area manajemen dan area proyek pengguna .

Harness itu sendiri berisi modul pencatatan jam kerja, DLL, ID pengguna, SPI housekeeping, POR, dan kontrol GPIO.

Penanganan GPIO dipindahkan dari SoC manajemen dan ke SPI. SPI mendapat antarmuka wishbone; SoC manajemen berkomunikasi dengan SPI melalui wishbone, bukan dengan mengambil alih antarmuka SPI 4-pin.

Blok baru seperti ID memiliki mode penyalaan untuk setiap GPIO. Dapat dikonfigurasi dengan file teks. Pin SPI ditetapkan untuk pengoperasian saat startup.

Saat dinyalakan, SPI secara otomatis mengkonfigurasi GPIO. Pemuatan manual dimungkinkan dari SPI dan dari bus wishbone.

Semua fungsi di dalam harness tetapi di luar SoC manajemen digabungkan ke dalam satu modul besar yang disebut "housekeeping". Ini mencakup sejumlah register untuk semua fungsi yang disertakan, dengan antarmuka SPI "pintu depan" yang terhubung ke padframe melalui pin GPIO 1 hingga 4, dan antarmuka wishbone "pintu belakang" yang terhubung ke SoC manajemen. Soc manajemen mencadangkan blok memori pada 0x26000000 untuk modul housekeeping. Modul housekeeping bertukar data dengan SoC manajemen melalui antarmuka yang menggunakan data register SPI selebar byte. Mesin negara kecil membaca empat alamat wishbone yang berdekatan dan dekoder alamat menentukan register SPI yang sesuai. Mesin negara menghentikan SoC sampai keempat byte telah ditangani sebelum mengembalikan sinyal pengakuan.

Area manajemen adalah modul drop-in yang diimplementasikan sebagai repo terpisah. Biasanya mencakup SoC berbasis RISC-V yang mencakup sejumlah periferal seperti pengatur waktu, uart, dan gpio. Area manajemen menjalankan firmware yang dapat digunakan untuk:

Area manajemen menerapkan SRAM untuk SoC manajemen.

Instansiasi default untuk inti manajemen dapat ditemukan di sini. Lihat dokumentasi inti manajemen untuk rincian lebih lanjut.

Ini adalah ruang pengguna. Ia memiliki area silikon terbatas 2.92mm x 3.52mm serta jumlah bantalan I/O yang tetap 38 dan bantalan daya 4 .

Ruang pengguna memiliki akses ke utilitas berikut yang disediakan oleh SoC manajemen:

38 Pelabuhan IO128 Probe penganalisis logika Area Anda adalah ruang pengguna penuh, jadi silakan tambahkan proyek Anda di sana atau buat makro berbeda dan perkuat secara terpisah lalu masukkan ke dalam user_project_wrapper untuk proyek digital atau masukkan ke dalam user_project_analog_wrapper untuk proyek analog.

Jika Anda sedang membangun proyek digital untuk ruang pengguna, periksa contoh proyek di caravel_user_project.

Jika Anda akan menggunakan OpenLANE untuk memperkuat desain Anda, ikuti instruksi dalam README ini.

Proyek pengguna digital harus mematuhi persyaratan berikut:

user_project_wrapperuser_project_wrapper mematuhi urutan pin yang ditentukan pada Urutan Pin Pembungkus Digital.user_project_wrapper mematuhi konfigurasi desain tetap di Konfigurasi Tetap Digital Wrapper.Jika Anda membuat proyek analog untuk ruang pengguna, periksa contoh proyek di caravel_user_project_analog.

Proyek pengguna analog harus mematuhi persyaratan berikut:

user_analog_project_wrapperuser_analog_project_wrapper menggunakan pembungkus analog yang kosong.user_analog_project_wrapper mengikuti urutan pin dan penempatan pembungkus analog kosong yang sama. Harap pastikan untuk menjalankan make compress sebelum melakukan apa pun ke repositori Anda. Hindari 2 versi gds/user_project_wrapper.gds yang satu dikompresi dan yang lainnya tidak dikompresi.

Untuk informasi tentang perkakas dan pembuatan versi, silakan merujuk ke tool-versioning.rst.

gds/ : mencakup semua file gds yang digunakan atau dihasilkan dari proyek.def : mencakup semua file def yang digunakan atau dihasilkan dari proyek.lef/ : mencakup semua file kiri yang digunakan atau dihasilkan dari proyek.mag/ : mencakup semua file mag yang digunakan atau dihasilkan dari proyek.maglef : mencakup semua file maglef yang digunakan atau dihasilkan dari proyek.spi/lvs/ : mencakup semua file bumbu yang digunakan atau dihasilkan dari proyek.verilog/dv : mencakup semua bangku tes simulasi dan cara menjalankannya.verilog/gl/ : mencakup semua netlist yang disintesis/diuraikan.verilog/rtl : mencakup semua RTL Verilog dan file sumber.openlane/<macro>/ : mencakup semua file konfigurasi yang digunakan untuk menjalankan openlane di proyek Anda.info.yaml : mencakup semua info yang diperlukan dalam contoh ini. Harap pastikan bahwa Anda menunjuk ke netlist caravel yang diuraikan serta netlist tingkat gerbang yang disintesis untuk user_project_wrapperCATATAN:

Jika Anda menggunakan openlane untuk memperkeras desain Anda, direktoriverilog/gldef/lef/gds/magmaglefharus secara otomatis diisi oleh openlane.

Periksa mpw-one-final untuk caravel yang digunakan untuk tapeout mpw-one.

>make ship tidak lagi diperlukan.