UDP オフロード エンジンは、FPGA ハードウェア プログラミングに使用される IP VHDL です。

この IP は UDP-IP スタック アクセラレータであり、イーサネット リンクを通じてデータを送受信できます。このスタックは、構成可能なバス サイズにより、最大 40 Gb/s のイーサネット レートで使用できるように高度に構成可能です。しかもモジュール式です。リソースを節約するために無効化できるさまざまなプロトコルと統合テスト ツールが実装されています。

この IP は、エンジニアリングにおけるタレス戦略に従ったビルディング ブロックに基づいています。これらは基本的な機能を実行し、プラットフォーム/ターゲットから独立できるようにします。このデザインではメーカーのプリミティブは使用されておらず、すべて推測されます。

目次

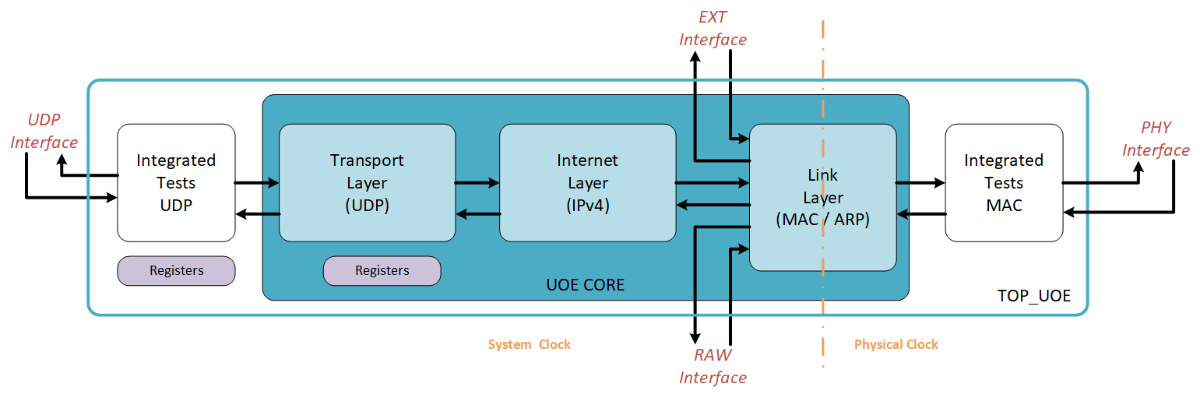

この図は、IP の内部アーキテクチャを示しています。主要なエンティティはモジュールuoe_coreです。これは、いくつかの統合テスト関数をさらにインスタンス化するトップ ラッパーtop_uoeにカプセル化されています。

機能部

内蔵テスト部品(オプション)

スタックの完全なドキュメントは、アーキテクチャ ガイドで入手できます。

設定可能なバスサイズ

以下のプロトコルを処理します

アドレス解決プロトコル (ARP)

インターネット制御メッセージ プロトコル (ICMP)

MAC インターフェイス上のバッファとクロック ドメインの交差を考慮する

受信トラフィックのフィルタリング オプション

一般バスの利用

デザインは、さまざまなジェネリックス パラメーターを使用して、コンテキスト外の複数のターゲットに対して合成および実装されています。結果は「パフォーマンス」ページで確認できます。

このリポジトリには、次の設計例が統合されています。

近日公開 ...

このプロジェクトに貢献することに興味がある場合は、まず貢献ガイドラインを読んでください。