UDP 오프로드 엔진은 FPGA 하드웨어 프로그래밍에 사용되는 IP VHDL입니다.

이 IP는 UDP-IP 스택 가속기로서 이더넷 링크를 통해 데이터를 주고받을 수 있습니다. 이 스택은 구성 가능한 버스 크기 덕분에 최대 40Gb/s의 이더넷 속도와 함께 사용할 수 있도록 고도로 구성 가능합니다. 게다가 모듈식입니다. 리소스를 절약하기 위해 비활성화할 수 있는 다양한 프로토콜과 통합 테스트 도구를 구현합니다.

이 IP는 엔지니어링 분야의 Thales 전략을 따르는 빌딩 블록을 기반으로 합니다. 기본 기능을 수행하고 플랫폼/타겟으로부터 독립될 수 있습니다. 이 설계에는 제조업체 기본 요소가 사용되지 않으며 모두 추론됩니다.

목차

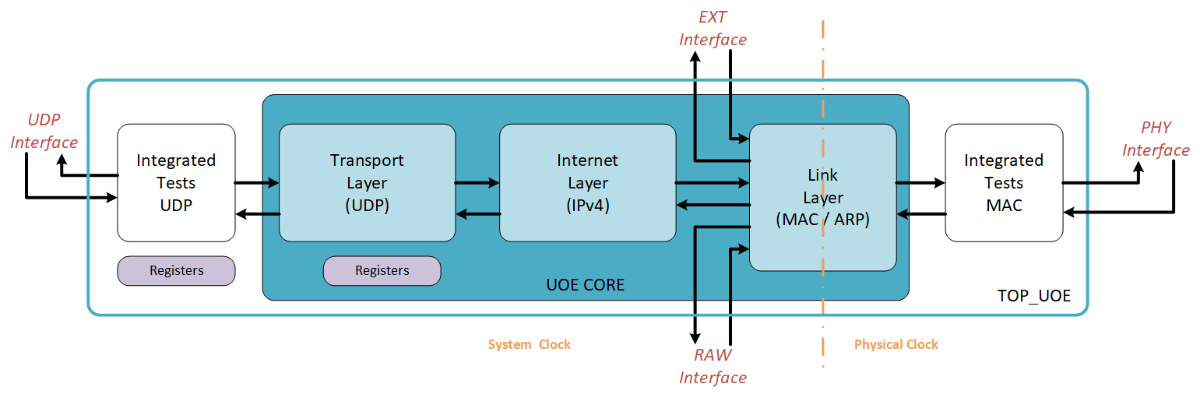

이 그림은 IP의 내부 아키텍처를 설명합니다. 주요 엔터티는 uoe_core 모듈입니다. 일부 통합 테스트 기능을 추가로 인스턴스화하는 상위 래퍼 top_uoe 에 캡슐화되었습니다.

기능적인 부분

내장 테스트 부품(옵션)

스택의 전체 문서는 아키텍처 가이드에서 확인할 수 있습니다.

구성 가능한 버스 크기

다음 프로토콜을 처리합니다.

ARP(주소 확인 프로토콜)

ICMP(인터넷 제어 메시지 프로토콜)

MAC 인터페이스 및 클록 도메인 교차의 버퍼를 고려합니다.

들어오는 트래픽에 대한 필터링 옵션

일반버스 이용

디자인은 다양한 일반 매개변수를 사용하여 상황에 맞지 않는 여러 대상에 대해 합성 및 구현되었습니다. 결과는 성능 페이지에서 확인할 수 있습니다.

이 저장소는 다음 디자인 예제를 통합합니다.

곧 출시됩니다 ...

이 프로젝트에 기여하고 싶다면 기여 가이드라인을 읽어보세요.