이 저장소는 FPGA의 고성능 패킷 처리를 위해 Bluespec SystemVerilog(BSV)에서 이더넷 관련 구성 요소 모음을 구현합니다. 특히 이 저장소는 UDP/IP/이더넷 패킷을 생성하고 구문 분석하기 위한 모듈을 제공합니다. 주소 정보를 저장하는 비차단 캐시를 갖춘 ARP 처리 장치도 제공되어 MAC 주소 확인을 자동으로 처리합니다. 표준 UDP/IP/이더넷 스택을 구축하는 것 외에도 블루 이더넷은 RoCE(RDMA over Converged Ethernet)에 대한 지원을 추가합니다. 1) UDP/IP 패킷 처리에 ICRC(Invariant Cyclic Redundancy) 생성 및 검증을 통합합니다. 2) 무손실 네트워크 전송을 실현하기 위해 PFC(Priority Flow Control)를 처리하는 모듈을 제공합니다. 마지막으로 패킷 생성기 및 파서가 Xilinx 100G 이더넷 하위 시스템(CMAC)과 상호 작용할 수 있도록 인터페이스 변환 모듈도 제공됩니다.

이 저장소의 일부 주요 디렉터리는 다음과 같습니다.

├── lib # external libraries/repos

│ ├── blue-crc # high-performance CRC hardware implementation

│ └── blue-wrapper # BSV wrappers for generating ready-to-use Verilog interface

├── scripts # scripts used to build project

├── src # design source files

│ └── includes # files containing some commonly-used BSV types and modules

├── syn # scripts for vivado synthesis and implementation

└── test # source files for verification

├── bluesim # testbenches based on bluesim

├── cocotb # python testbenches based on cocotb

└── vivado # co-simulation with cmac using vivado다음은 몇 가지 중요한 소스 파일 목록입니다.

./src

├── ArpCache.bsv # Cache implementation storing MAC addresses got from ARP

├── ArpProcessor.bsv # processing unit handling ARP requests and responses

├── includes

│ ├── CompletionBuf.bsv

│ ├── ContentAddressMem.bsv

│ ├── EthernetTypes.bsv # numeric and struct types about protocol definition

│ ├── PortConversion.bsv # interface conversion modules used to generate ready-to-use Verilog

│ ├── Ports.bsv # numeric and struct types about in/output ports of modules

│ ├── RFile.bsv

│ ├── StreamHandler.bsv # modules implemented for manipulating data stream

│ └── EthUtils.bsv # utility functions and modules

├── MacLayer.bsv # generator and parser for Ethernet packet

├── PfcUdpIpArpEthRxTx.bsv # generator and parser for UDP/IP/Ethernet packet with PFC

├── PriorityFlowControl.bsv # modules handling PFC

├── UdpIpArpEthRxTx.bsv # generator and parser for UDP/IP/Ethernet packet

├── UdpIpEthRx.bsv # parser for UDP/IP/Ethernet packet

├── UdpIpEthTx.bsv # generator for UDP/IP/Ethernet packet

├── UdpIpLayer.bsv # parser and generator for UDP/IP packet

├── UdpIpLayerForRdma.bsv # parser and generator for UDP/IP packet with support for RoCE

└── XilinxCmacRxTxWrapper.bsv # bridge modules between parser/generator and Xilinx CMAC이 섹션에서는 기능, 인터페이스 및 하드웨어 아키텍처를 포함하여 블루 이더넷으로 구현된 일부 중요한 구성 요소에 대한 자세한 설명을 제공합니다.

이더넷 관련 하드웨어 구성 요소가 수행하는 작업은 기본적으로 일련의 스트림 조작입니다. 패킷 생성기는 완전한 패킷 스트림을 생성하기 위해 헤더 스트림을 페이로드 스트림의 헤드에 삽입하는 역할을 담당합니다. 반대로 파서가 하는 일은 패킷 스트림에서 헤더 스트림과 페이로드 스트림을 추출하는 것입니다. 패킷에 대한 체크섬을 추가하는 경우 패킷 스트림이 CRC 계산기로 전달된 다음 출력 CRC 값이 패킷 스트림의 꼬리에 추가됩니다.

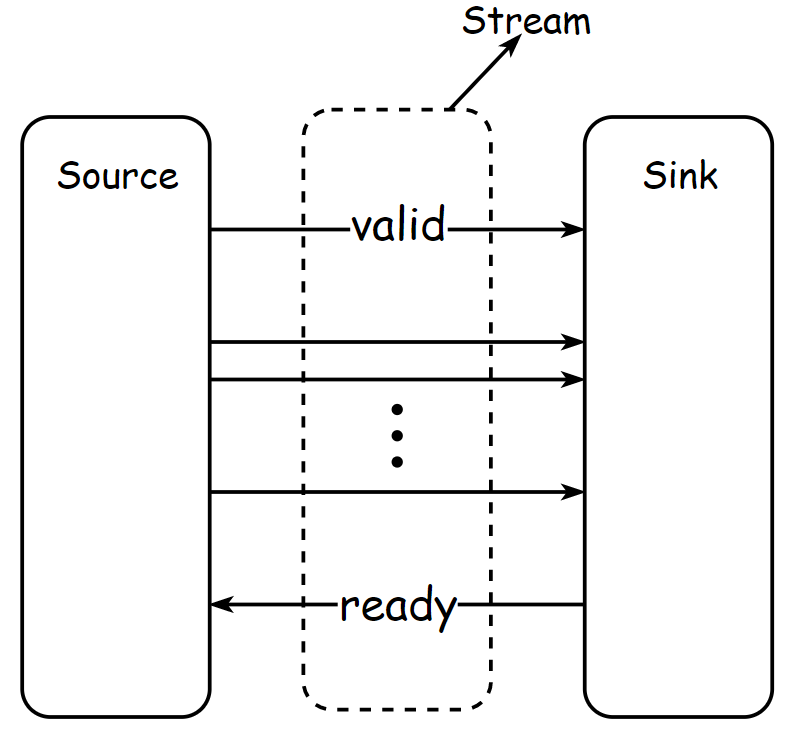

여기서 언급한 스트림에 해당하는 하드웨어 엔터티는 실제로 유효한 준비 제어 신호 쌍에 의해 보호되는 데이터 신호 그룹입니다. 유효한 신호는 소스 구성 요소가 데이터를 전송하려고 함을 나타냅니다. 그리고 준비는 싱크가 소스로부터 데이터를 수신할 준비가 되었음을 나타냅니다. 소스와 싱크 간의 전송은 유효 및 준비가 모두 높은 경우에만 성공적으로 발생합니다. 전송하려는 데이터의 크기가 한 번의 전송 크기보다 큰 경우 데이터를 조각화하여 일련의 전송으로 전송해야 합니다.

스트림 처리에서 가장 까다롭고 오류가 발생하기 쉬운 부분은 다양한 스트림의 유효한 준비 제어 신호를 처리하는 방법에 관한 것입니다. BSV에서 제어 신호의 조작은 컴파일러에 의해 구현되며 문법 수준에서는 보이지 않으므로 설계자가 스트림 처리 논리에 집중할 수 있습니다.

서로 다른 구성 요소 간에 패킷 스트림을 전송하는 데 사용되는 데이터 신호는 256비트 데이터 신호, 32비트 바이트 활성화 신호를 포함하는 DataStream 구조에 캡슐화됩니다. 두 개의 부울 신호는 이 전송이 패킷 스트림의 마지막인지 첫 번째인지를 나타냅니다.

typedef 256 DATA_BUS_WIDTH ;

typedef TDiv # ( DATA_BUS_WIDTH , 8 ) DATA_BUS_BYTE_WIDTH ;

typedef Bit # ( DATA_BUS_WIDTH ) Data ;

typedef Bit # ( DATA_BUS_BYTE_WIDTH ) ByteEn ;

typedef struct {

Data data ;

ByteEn byteEn ;

Bool isFirst ;

Bool isLast ;

} DataStream deriving ( Bits , Bounded , Eq , FShow ) ; module mkAppendDataStreamHead # (

IsSwapEndian swapDataStream ,

IsSwapEndian swapAppendData ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( dType ) appendDataIn

)( FifoOut # ( DataStream )) ; module mkAppendDataStreamTail # (

IsSwapEndian swapDataStream ,

IsSwapEndian swapAppendData ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( dType ) appendDataIn ,

FifoOut # ( Bit # ( streamLenWidth )) streamLengthIn

)( FifoOut # ( DataStream )) ; interface ExtractDataStream # ( type dType ) ;

interface FifoOut # ( dType ) extractDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkExtractDataStreamHead # (

FifoOut # ( DataStream ) dataStreamIn

)( ExtractDataStream # ( dType )) ;UdpIpLayer 패키지의 모듈은 UDP/IP 패킷을 생성하고 구문 분석하기 위해 구현됩니다.

패킷 생성기는 UDP/IP 헤더 정보와 페이로드 스트림을 포함하는 UdpIpMetaData를 가져와서 완전한 UDP/IP 패킷 스트림을 출력합니다. 패킷 파서는 UDP/IP 패킷 스트림에서 UdpIpMetaData 및 페이로드 스트림을 추출하여 반대 방식으로 작동합니다.

typedef struct {

UdpLength dataLen ; # The Length of payload data

IpAddr ipAddr ; # Desitnation IP address

IpDscp ipDscp ; # DSCP field used for PFC

IpEcn ipEcn ; # ECN field

UdpPort dstPort ; # Destination port number

UdpPort srcPort ; # Source port number

} UdpIpMetaData ;UdpIpMetaData 구조체에 캡슐화된 신호는 UDP/IP 헤더에 정의된 모든 필드를 포함하지 않습니다. 헤더의 일부 필드는 특정 네트워크 장치에 대해 고정되어 있으며 UdpConfig 구조에 캡슐화되어 있으며 패킷을 전송하거나 수신하기 전에 구성해야 합니다. 그리고 일부 다른 필드는 하드웨어 구성 요소에 일정하고 하드 코딩되어 있습니다.

typedef struct {

EthMacAddr macAddr ; # Source MAC address

IpAddr ipAddr ; # Source IP address

IpNetMask netMask ; # IP netmask

IpGateWay gateWay ; # IP gateway

} UdpConfig ; module mkUdpIpStream # (

UdpConfig udpConfig ,

FifoOut # ( DataStream ) dataStreamIn ,

FifoOut # ( UdpIpMetaData ) udpIpMetaDataIn ,

function UdpIpHeader genHeader ( UdpIpMetaData meta , UdpConfig udpConfig , IpID ipId )

)( FifoOut # ( DataStream )) ; interface UdpIpMetaDataAndDataStream ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkUdpIpMetaDataAndDataStream # (

UdpConfig udpConfig ,

FifoOut # ( DataStream ) udpIpStreamIn ,

function UdpIpMetaData extractMetaData ( UdpIpHeader hdr )

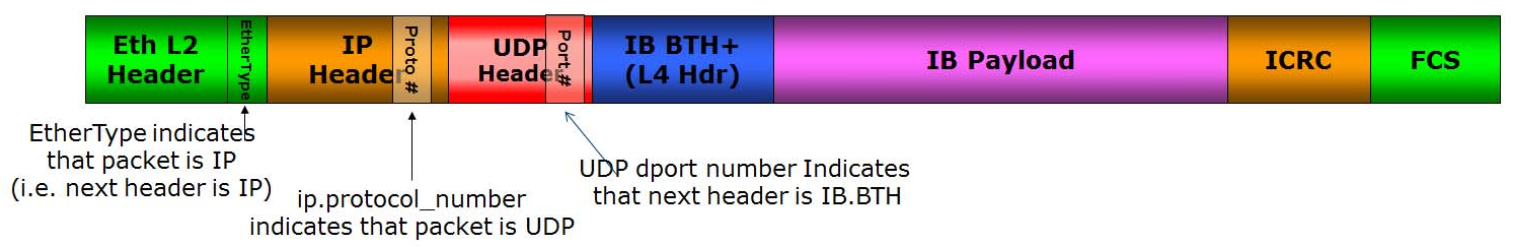

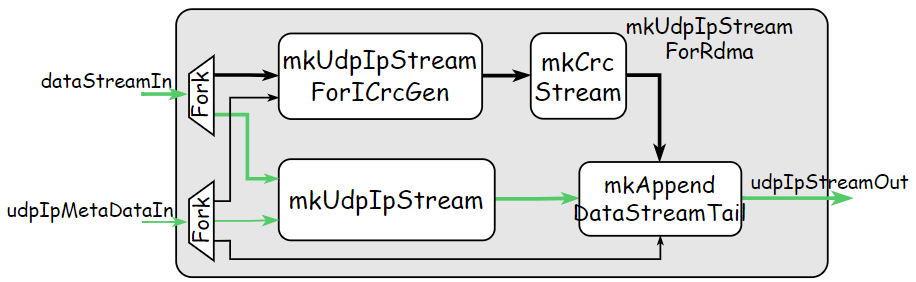

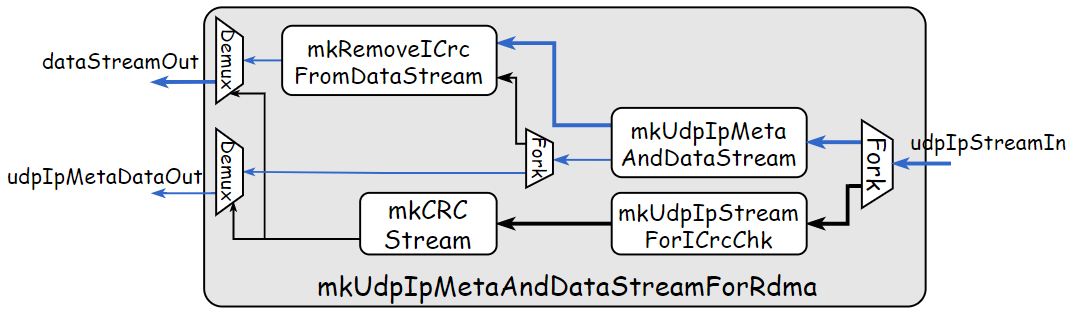

)( UdpIpMetaDataAndDataStream ) ; UdpIpLayerForRdma 패키지의 모듈은 RoCE(RDMA over Converged Ethernet)를 지원하는 UdpIpLayer를 기반으로 구현됩니다. RoCE를 지원하기 위해 추가된 추가 기능은 RoCE 패킷에 필요한 ICRC(Invariant CRC) 생성 및 검증입니다. RoCE 패킷의 형식은 다음과 같이 정의됩니다.

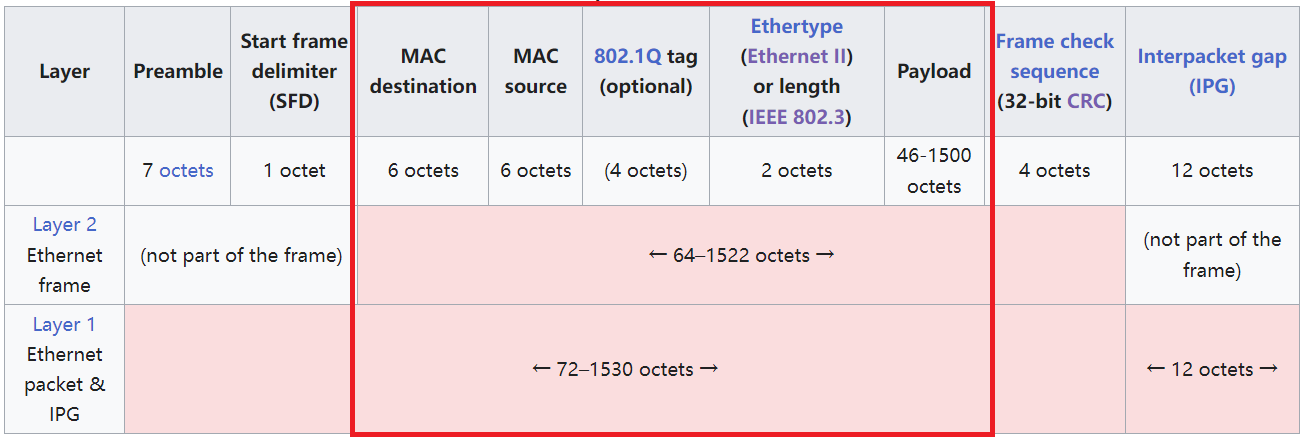

MacLayer 패키지의 모듈은 이더넷 패킷을 생성하고 구문 분석하기 위해 구현됩니다. 생성기는 UDP/IP 패킷 스트림의 선두에 이더넷 헤더를 삽입하여 이더넷 패킷 스트림을 생성합니다. 파서는 이더넷 패킷 스트림에서 이더넷 헤더와 UDP/IP 패킷 스트림을 추출합니다.

이더넷 패킷을 생성하는데 사용되는 헤더 정보는 MacMetaData 구조체에 정의되어 있습니다.

typedef struct {

EthMacAddr macAddr ; # Destination MAC address

EthType ethType ; # Type of Ethernet frame

} MacMetaData deriving ( Bits , Eq , FShow ) ;참고로 MacLayer 에서 처리되는 이더넷 패킷은 아래 그림에서 빨간색 직사각형으로 표시된 필드만 포함합니다. 다른 필드는 Xilinx CMAC IP에서 처리되도록 남겨져 있습니다.

module mkMacStream # (

FifoOut # ( DataStream ) udpIpStreamIn ,

FifoOut # ( MacMetaData ) macMetaDataIn ,

UdpConfig udpConfig

)( FifoOut # ( DataStream )) ; interface MacMetaDataAndUdpIpStream ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface FifoOut # ( DataStream ) udpIpStreamOut ;

endinterface

module mkMacMetaDataAndUdpIpStream # (

FifoOut # ( DataStream ) macStreamIn ,

UdpConfig udpConfig

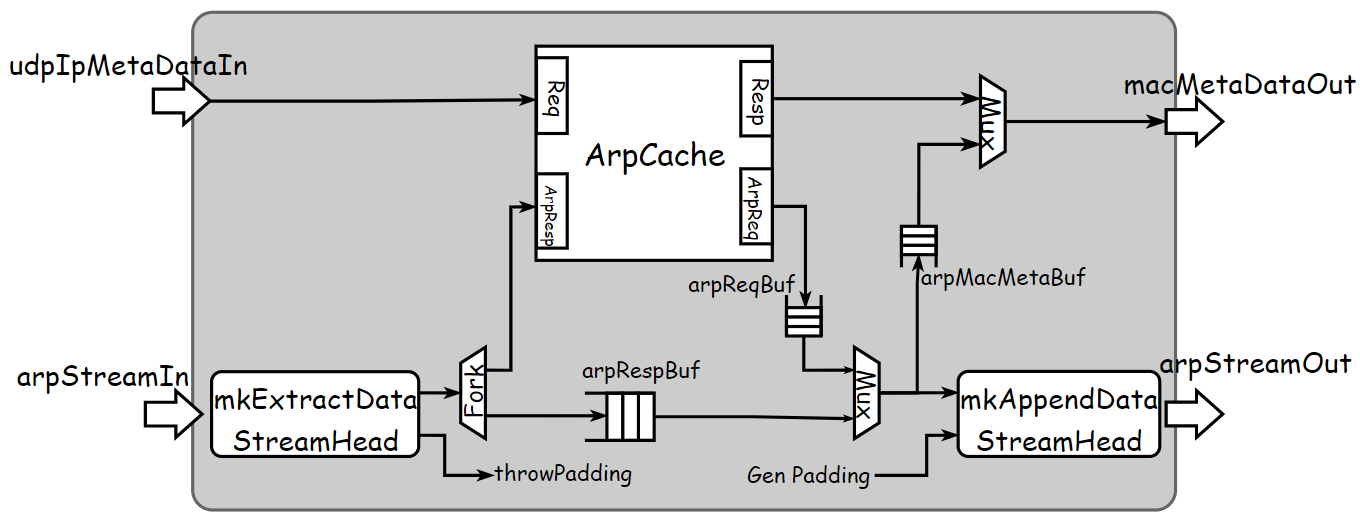

)( MacMetaDataAndUdpIpStream ) ; ARP(주소 확인 프로토콜)는 특정 IP 주소와 연관된 MAC 주소를 검색하는 데 사용됩니다. 블루 이더넷에서는 ARP 패킷 생성기, 파서 및 MAC 주소를 저장하는 mkArpCache 모듈을 통합하는 ARP 처리를 위해 mkArpProcessor 모듈이 구현됩니다.

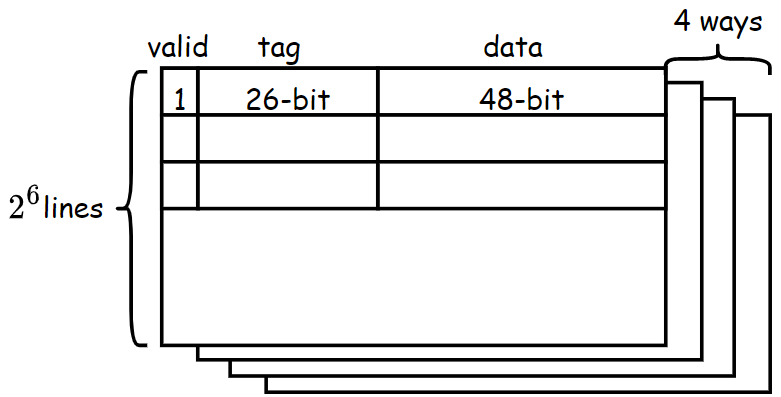

ARP 처리에 사용되는 캐시의 경우 32비트 IP 주소는 캐시 주소에 해당하고 48비트 MAC 주소는 캐시 데이터에 해당합니다. ARP 캐시를 위한 메모리 배열의 기본 배열은 아래와 같습니다. 이는 4방향 집합 연관 구조로, 각 방향에는 64개의 라인이 포함되고 각 라인에는 1비트 유효, 26비트 태그 및 48비트 데이터가 포함됩니다. 이 기본 어레이 구성의 전체 크기는 약 1.2KB입니다. 라인 수와 웨이 수를 설정하여 메모리 배열의 크기를 변경하는 것이 지원됩니다. 이 메모리 배열을 기반으로 캐시는 비차단 기능을 갖고 미해결 요청(비행 중 다중 요청)을 지원하며 캐시 라인 교체를 위해 의사 LRU 알고리즘을 사용하도록 설계되었습니다.

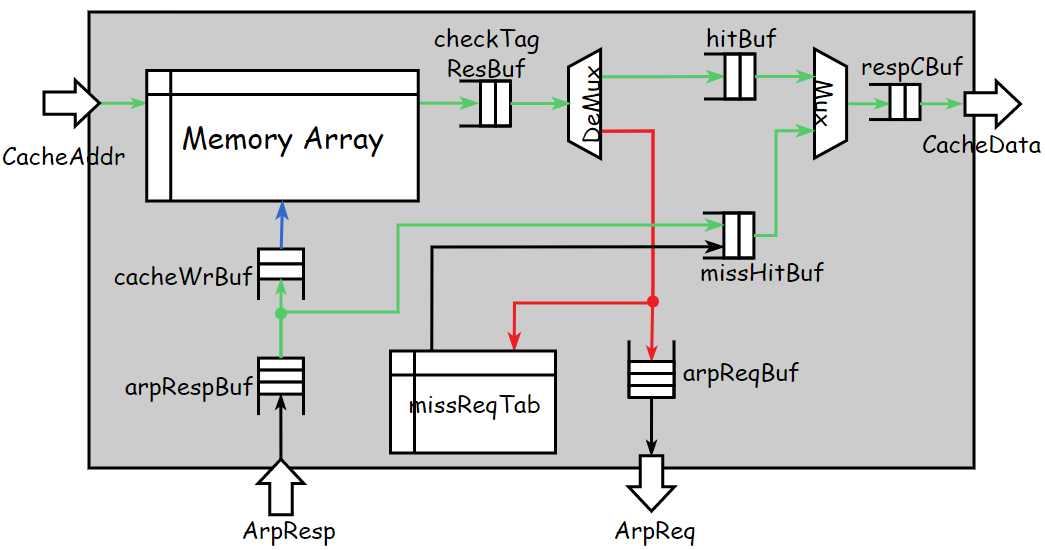

mkArpCache 모듈의 인터페이스 정의와 단순화된 구조 다이어그램은 다음과 같습니다. ArpCache 에는 두 가지 하위 인터페이스가 있습니다. 캐시 서버는 MAC 주소 확인 서비스를 제공하는 구성 요소와의 상호 작용을 처리합니다. arpClient 는 mkArpProcessor 와의 상호 작용을 처리하여 ARP 요청을 시작하고 ARP 응답에서 MAC 주소를 얻습니다. mkArpCache 모듈의 기본 작업 흐름은 다음과 같습니다.

캐시가 읽기 요청을 받으면 먼저 메모리 배열을 검색하여 지정된 IP 주소에 해당하는 모든 태그와 데이터를 가져옵니다. 그런 다음 태그를 확인하여 필요한 데이터가 캐시에 저장되어 있는지 확인합니다. 캐시 적중이 발생하면 가져온 데이터가 hitBuf 로 전송됩니다. 또는 IP 주소가 arpReqBuf 로 전송되어 ARP 요청을 시작합니다. 그리고 ARP 응답이 돌아오면 전달되는 데이터와 주소 정보가 모두 캐시WrBuf 및 missHitBuf 에 기록되어 메모리 배열을 업데이트하고 캐시 읽기 응답을 반환합니다.

interface ArpCache ;

interface Server # ( CacheAddr , CacheData ) cacheServer ;

interface Client # ( CacheAddr , ArpResp ) arpClient ;

endinterface

캐시 구현에서 가장 어려운 부분은 뛰어난 기능, 즉 비행 중 다중 읽기 요청을 지원하는 것입니다. 미해결로 인한 문제는 각 on-flight ARP 요청마다 응답 시간이 다르기 때문에 늦은 요청이 먼저 응답을 받을 수 있다는 것입니다. 따라서 캐시 누락이 발생할 때 요청 주소와 응답 데이터 간의 일치를 보장하려면 재정렬 메커니즘이 필요합니다. 순차 응답을 실현하기 위해 완료 버퍼 respCBuf 및 콘텐츠 주소 지정 가능 메모리 missReqTab 이 데이터 흐름에 통합됩니다. 완료 버퍼는 예약 기능을 추가로 지원하는 FIFO처럼 작동합니다. 실제 대기열에 넣기 작업 전에 먼저 완료 버퍼에 주문을 예약할 수 있습니다. 그리고 큐에서 빼기 작업은 큐에 넣기 작업의 실제 순차적 순서에 관계없이 예약된 순서를 따릅니다. 각 읽기 요청에 대해 대기열 제거 순서는 일단 수신되면 respCBuf 에서 반전됩니다. 그리고 ARP 요청은 주문 정보를 전달할 수 없기 때문에 missReqTab을 구현하여 이를 저장합니다.

모듈은 ARP 클라이언트와 서버 모두로 작동할 수 있습니다. 서버로서 프로세서는 대상 IP의 MAC 주소를 알 수 없는 경우 ARP 요청을 생성한 다음 대상 장치의 ARP 응답을 기다려야 합니다. 클라이언트로서 ARP 프로세서는 다른 장치로부터 ARP 요청을 수신하고 자신의 MAC 주소를 포함하는 ARP 응답을 다시 보냅니다.

interface ArpProcessor ;

interface FifoOut # ( DataStream ) arpStreamOut ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface Put # ( UdpConfig ) udpConfig ;

endinterface

module mkArpProcessor # (

FifoOut # ( DataStream ) arpStreamIn ,

FifoOut # ( UdpIpMetaData ) udpIpMetaDataIn

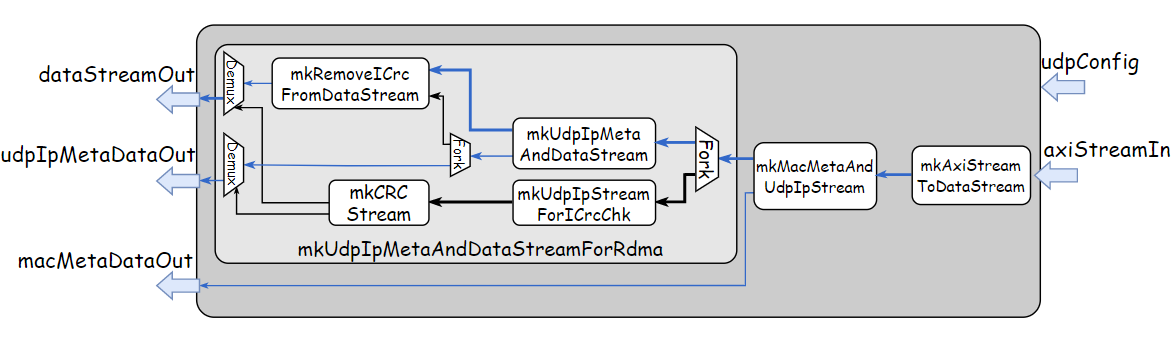

)( ArpProcessor ) ; UdpIpEthRx 패키지의 모듈은 UDP/IP/이더넷 패킷을 수신하고 구문 분석하기 위해 구현됩니다.

interface UdpIpEthRx ;

interface Put # ( UdpConfig ) udpConfig ;

interface Put # ( AxiStream512 ) axiStreamIn ;

interface FifoOut # ( MacMetaData ) macMetaDataOut ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface FifoOut # ( DataStream ) dataStreamOut ;

endinterface

module mkGenericUdpIpEthRx # ( Bool isSupportRdma )( UdpIpEthRx )

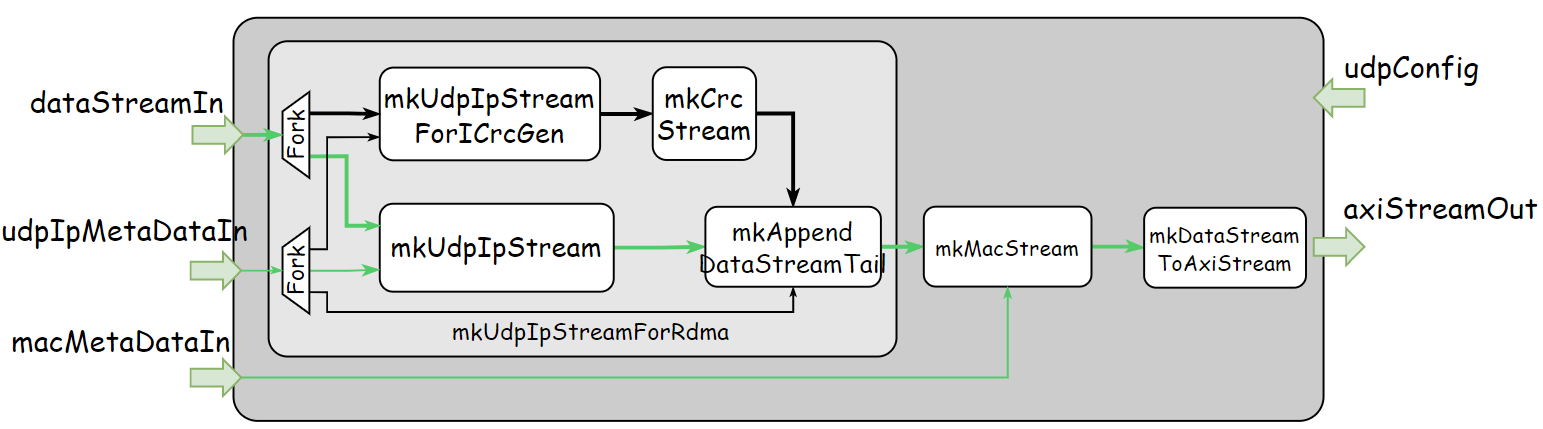

UdpIpEthTx 패키지의 모듈은 UDP/IP/이더넷 패킷을 생성하고 전송하기 위해 구현됩니다.

interface UdpIpEthTx ;

interface Put # ( UdpConfig ) udpConfig ;

interface Put # ( UdpIpMetaData ) udpIpMetaDataIn ;

interface Put # ( MacMetaData ) macMetaDataIn ;

interface Put # ( DataStream ) dataStreamIn ;

interface AxiStream512FifoOut axiStreamOut ;

endinterface

module mkGenericUdpIpEthTx # ( Bool isSupportRdma )( UdpIpEthTx ) ;

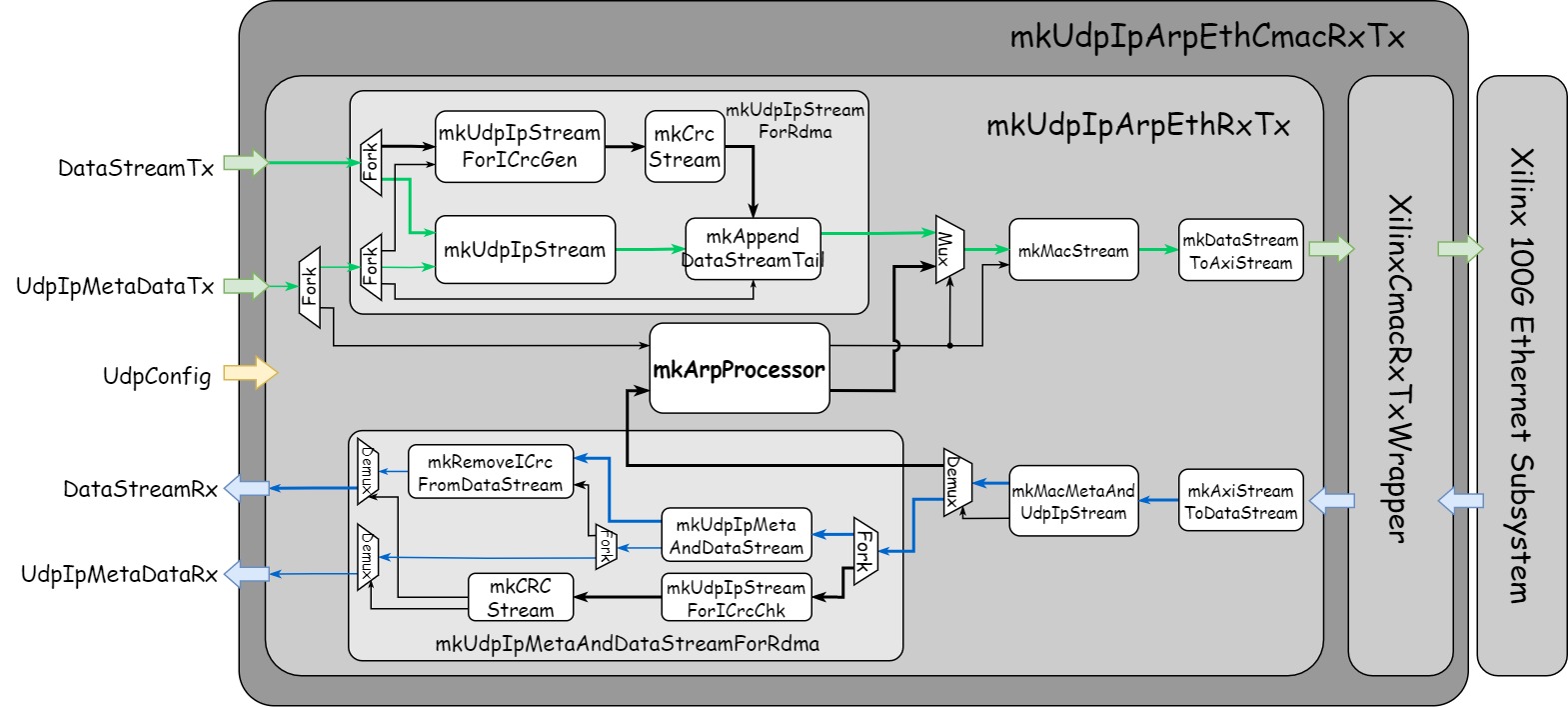

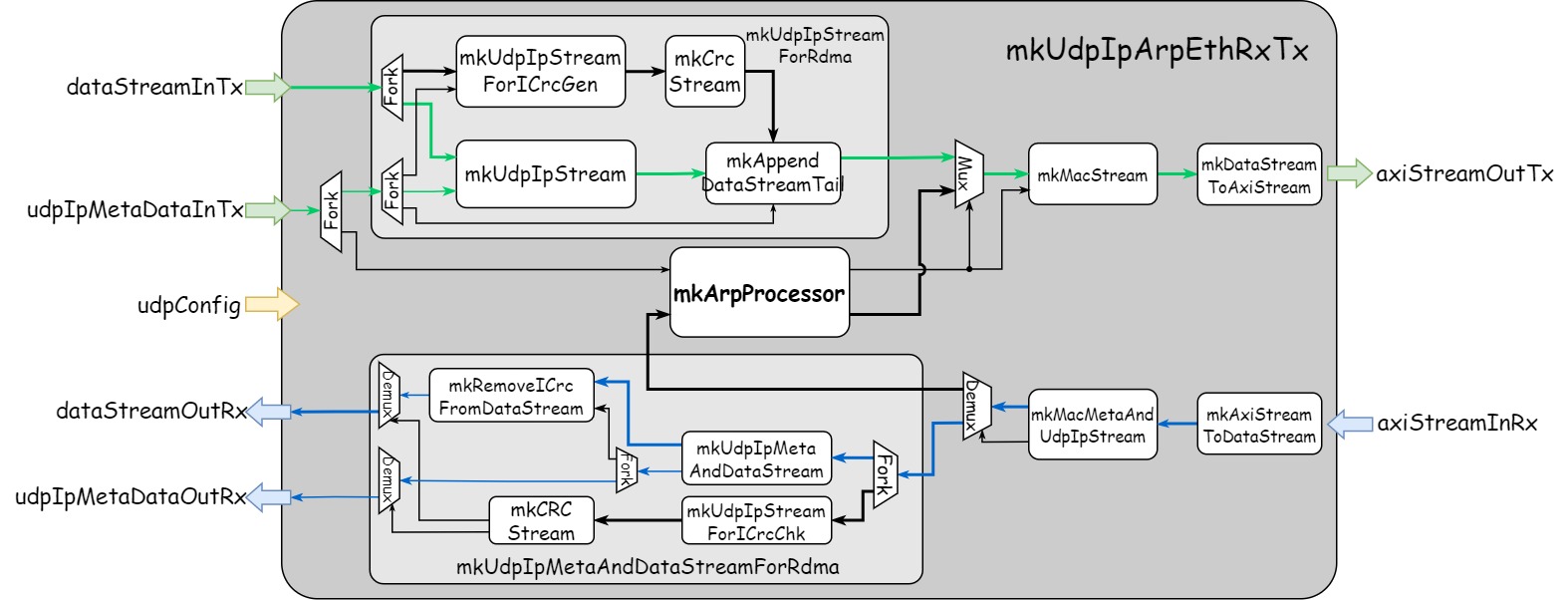

UdpIpArpEthRxTx 패키지에 제공되는 모듈은 UDP/IP/Ethernet 패킷을 송수신하고 ARP 요청과 응답을 동시에 처리하도록 설계되었습니다.

모듈은 전송 경로와 수신 경로를 포함하여 두 개의 반대 스트림 경로로 나눌 수 있습니다.

전송 경로로는 페이로드 스트림을 전달하는 dataStreamInTx 와 헤더 정보 스트림을 전달하는 udpIpMetaDataIn을 가져와 UDP/IP/Ethernet 패킷 스트림을 전달하는 axiStreamOutTx를 생성합니다. mkArpProcessor는 MAC 주소 해석 처리 및 이더넷 헤더 정보 생성을 담당하므로 이더넷 헤더 정보가 포함된 MacMetaData를 mkUdpIpEthTx 모듈로 제공할 필요가 없습니다.

수신 경로의 경우 UDP/IP/Ethernet 패킷 스트림을 전달하는 axiStreamInRx 에서 페이로드 스트림을 전달하는 dataStreamOutRx 와 헤더 정보 스트림을 전달하는 udpIpMetaDataOutRx를 추출하여 반대 방식으로 작동합니다.

이더넷 패킷 생성기와 파서는 UDP/IP 패킷과 ARP 패킷에 의해 공유되므로 스트림 중재 및 배포를 위한 송수신 경로에 추가 Mux 및 Demux가 필요합니다. 모듈 매개변수 isSupportRdma는 RoCE 패킷 처리를 지원하는지 여부를 지정합니다. RDMA 지원이 비활성화된 경우 전송 및 수신 경로에 각각 mkUdpIpStream 및 mkUdpIpMetaAndDataStream 만 필요합니다.

interface UdpIpArpEthRxTx ;

interface Put # ( UdpConfig ) udpConfig ;

// Tx

interface Put # ( UdpIpMetaData ) udpIpMetaDataInTx ;

interface Put # ( DataStream ) dataStreamInTx ;

interface AxiStream512FifoOut axiStreamOutTx ;

// Rx

interface Put # ( AxiStream512 ) axiStreamInRx ;

interface FifoOut # ( UdpIpMetaData ) udpIpMetaDataOutRx ;

interface FifoOut # ( DataStream ) dataStreamOutRx ;

endinterface

module mkGenericUdpIpArpEthRxTx # ( Bool isSupportRdma )( UdpIpArpEthRxTx ) ;

모듈은 블루 래퍼에 제공된 모듈을 사용하여 mkGenericUdpIpArpEthRxTx를 래핑하여 바로 사용할 수 있는 Verilog 인터페이스를 생성합니다.

이 모듈은 mkGenericUdpIpArpEthRxTx 모듈과 mkXilinxCmacTxWrapper 모듈을 모두 통합합니다. 이는 Xilinx CMAC IP와 상호 작용하여 물리적 매체와 UDP/IP/이더넷 패킷을 송수신하도록 설계되었습니다.

PriorityFlowControl 패키지의 모듈은 무손실 네트워크 전송을 보장하기 위해 우선순위 흐름 제어 메커니즘을 구현하도록 구현됩니다.

interface PriorityFlowControlTx ;

interface Get # ( UdpIpMetaData ) udpIpMetaDataOut ;

interface Get # ( DataStream ) dataStreamOut ;

endinterface

module mkPriorityFlowControlTx # (

FifoOut # ( FlowControlReqVec ) flowControlReqVecIn ,

Vector # ( VIRTUAL_CHANNEL_NUM , DataStreamFifoOut ) dataStreamInVec ,

Vector # ( VIRTUAL_CHANNEL_NUM , UdpIpMetaDataFifoOut ) udpIpMetaDataInVec

)( PriorityFlowControlTx ) ;

interface PriorityFlowControlRx # (

numeric type bufPacketNum ,

numeric type maxPacketFrameNum ,

numeric type pfcThreshold

) ;

interface FifoOut # ( FlowControlReqVec ) flowControlReqVecOut ;

interface Vector # ( VIRTUAL_CHANNEL_NUM , Get # ( DataStream )) dataStreamOutVec ;

interface Vector # ( VIRTUAL_CHANNEL_NUM , Get # ( UdpIpMetaData )) udpIpMetaDataOutVec ;

endinterface

module mkPriorityFlowControlRx # (

DataStreamFifoOut dataStreamIn ,

UdpIpMetaDataFifoOut udpIpMetaDataIn

)( PriorityFlowControlRx # ( bufPacketNum , maxPacketFrameNum , pfcThreshold )) ;

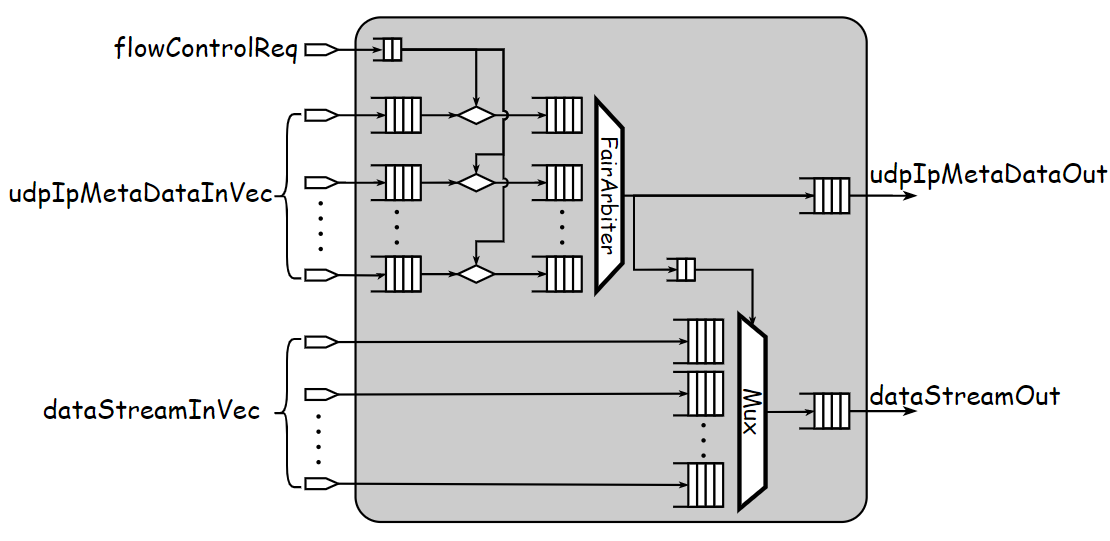

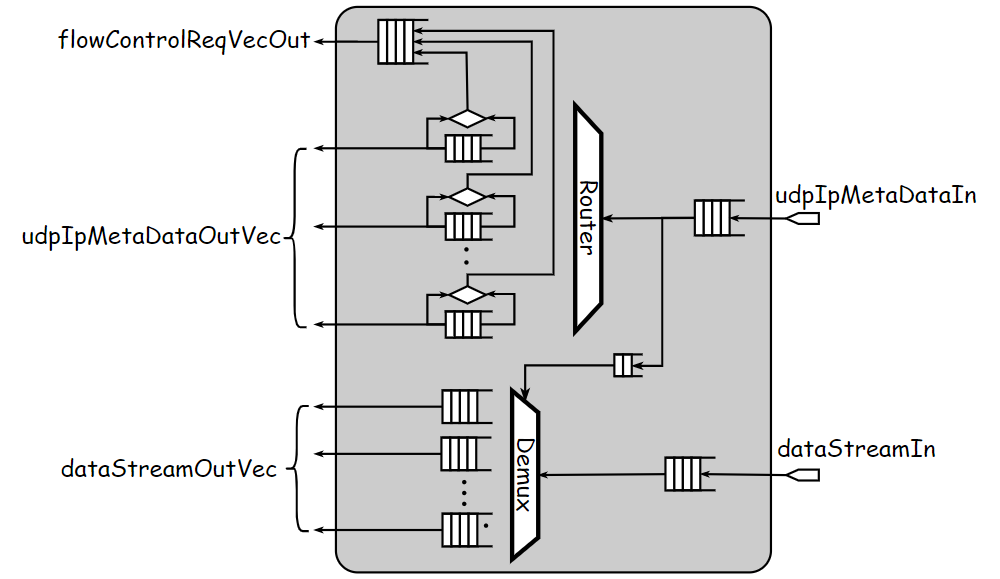

mkGenericPfcUdpIpArpEthRxTx는 mkPriorityFlowControlRx/Tx 및 mkGenericUdpIpArpEthRxTx를 통합하여 우선순위 흐름 제어를 지원하는 동시에 UDP/IP/이더넷 패킷을 생성하고 구문 분석하는 기능을 제공합니다. 패킷 전송의 경우 8개 채널의 페이로드 스트림과 UDP/IP 헤더 정보를 가져와 하나의 UDP/IP/이더넷 패킷 스트림을 출력합니다. 패킷 수신을 위해 하나의 UDP/IP/이더넷 패킷 스트림을 가져와서 추출된 UDP/IP 헤더와 페이로드 스트림을 8개의 출력 채널 중 하나로 라우팅합니다.

mkPfcUdpIpArpEthCmacRxTx는 mkGenericPfcUdpIpArpEthRxTx 모듈과 mkXilinxCmacTxWrapper 모듈을 모두 통합합니다. 이는 Xilinx CMAC IP와 상호 작용하여 물리적 매체와 UDP/IP/이더넷 패킷을 송수신하도록 설계되었습니다.

메인 모듈 mkGenericUdpIpArpEthRxTx 의 합성 및 구현은 Vivado를 사용하는 Xilinx xcvu9p 장치를 기반으로 수행됩니다. 결과에 따르면 회로는 500MHz의 작동 주파수에 도달하고 128Gbps의 최대 처리량을 제공할 수 있습니다. 하드웨어 리소스의 사용량은 다음과 같습니다.

CLB Logic

+----------------------------+-------+-------+------------+-----------+-------+

| Site Type | Used | Fixed | Prohibited | Available | Util % |

+----------------------------+-------+-------+------------+-----------+-------+

| CLB LUTs | 63886 | 0 | 0 | 1182240 | 5.40 |

| LUT as Logic | 41242 | 0 | 0 | 1182240 | 3.49 |

| LUT as Memory | 22644 | 0 | 0 | 591840 | 3.83 |

| LUT as Distributed RAM | 22644 | 0 | | | |

| LUT as Shift Register | 0 | 0 | | | |

| CLB Registers | 44099 | 0 | 0 | 2364480 | 1.87 |

| Register as Flip Flop | 44099 | 0 | 0 | 2364480 | 1.87 |

| Register as Latch | 0 | 0 | 0 | 2364480 | 0.00 |

| CARRY8 | 73 | 0 | 0 | 147780 | 0.05 |

| F7 Muxes | 194 | 0 | 0 | 591120 | 0.03 |

| F8 Muxes | 28 | 0 | 0 | 295560 | < 0.01 |

| F9 Muxes | 0 | 0 | 0 | 147780 | 0.00 |

+----------------------------+-------+-------+------------+-----------+-------+

BLOCKRAM

+-------------------+------+-------+------------+-----------+-------+

| Site Type | Used | Fixed | Prohibited | Available | Util % |

+-------------------+------+-------+------------+-----------+-------+

| Block RAM Tile | 4.5 | 0 | 0 | 2160 | 0.21 |

| RAMB36 / FIFO * | 4 | 0 | 0 | 2160 | 0.19 |

| RAMB36E2 only | 4 | | | | |

| RAMB18 | 1 | 0 | 0 | 4320 | 0.02 |

| RAMB18E2 only | 1 | | | | |

| URAM | 0 | 0 | 0 | 960 | 0.00 |

+-------------------+------+-------+------------+-----------+-------+이 섹션에서는 이 프로젝트를 시작하는 방법을 소개합니다. 다른 단계에 앞서 먼저 setup.sh 스크립트를 참조하여 개발 환경을 설정해야 합니다. 종속성 목록은 다음과 같습니다.

환경을 설정한 후 이 저장소를 특정 디렉터리에 복제합니다. 여기서는 이 디렉터리를 BLUE_ETH라고 합니다.

git clone --recursive https://github.com/wengwz/blue-ethernet.git $( BLUE_ETH ) 블루 이더넷에는 세 가지 수준의 테스트벤치가 제공됩니다.

# Specify TARGET to the name of target component

cd $( BLUE_ETH ) /test/bluesim

make TARGET=ArpCache # Run tests of UdpIpEthRx/Tx

# Enable/Disable support for RDMA by setting SUPPORT_RDAM to True/False

cd $( BLUE_ETH ) /test/cocotb

make cocotb TARGET=UdpIpEthTx SUPPORT_RDMA=TRUE

# Run simulation on virtual network

# Change NET_IFC in run_docker_net_test.sh to the name of your network card

cd $( BLUE_ETH ) /test/cocotb

docker build -f ./build_docker/Dockerfile -t ethernet-test ./build_docker

./run_docker_net_test.sh # Available TARGET includes UdpIpArpEthCmacRxTx/PfcUdpIpArpEthCmacRxTx

# Enable/Disable support for RDMA by setting SUPPORT_RDAM to True/False

cd $( BLUE_ETH ) /test/vivado

make sim TARGET=UdpIpArpEthCmacRxTx SUPPORT_RDMA=False설계 합성 및 구현을 실행하는 데 사용되는 스크립트는 $(BLUE_ETH)/syn 디렉터리에 제공됩니다.

# TARGET specifies the top module to be synthsized or implemented

# SUPPORT_RDMA specifies whether modules supports RoCE packet processing

# ONLYSYNTH decides whether or not run implemetation after synthesis

cd $( BLUE_ETH ) /syn

make vivado TARGET=UdpIpArpEthRxTx SUPPORT_RDMA=False ONLYSYNTH=0 # TARGET specifies the name of top module to be generated

# Specify SUPPORT_RDMA if needed

cd $( BLUE_ETH ) /test/cocotb

make verilog TARGET=UdpIpEthTx SUPPORT_RDMA=TRUEbsc -p +: $( BLUE_ETH ) /src: $( BLUE_ETH ) /src/includes ...블루 이더넷 구현에는 다음 외부 라이브러리의 사용이 포함됩니다.