***이 프로젝트는 진행 중인 미완성 작업입니다. 현재 버그가 있으며 모든 기능이 테스트되지는 않았습니다!

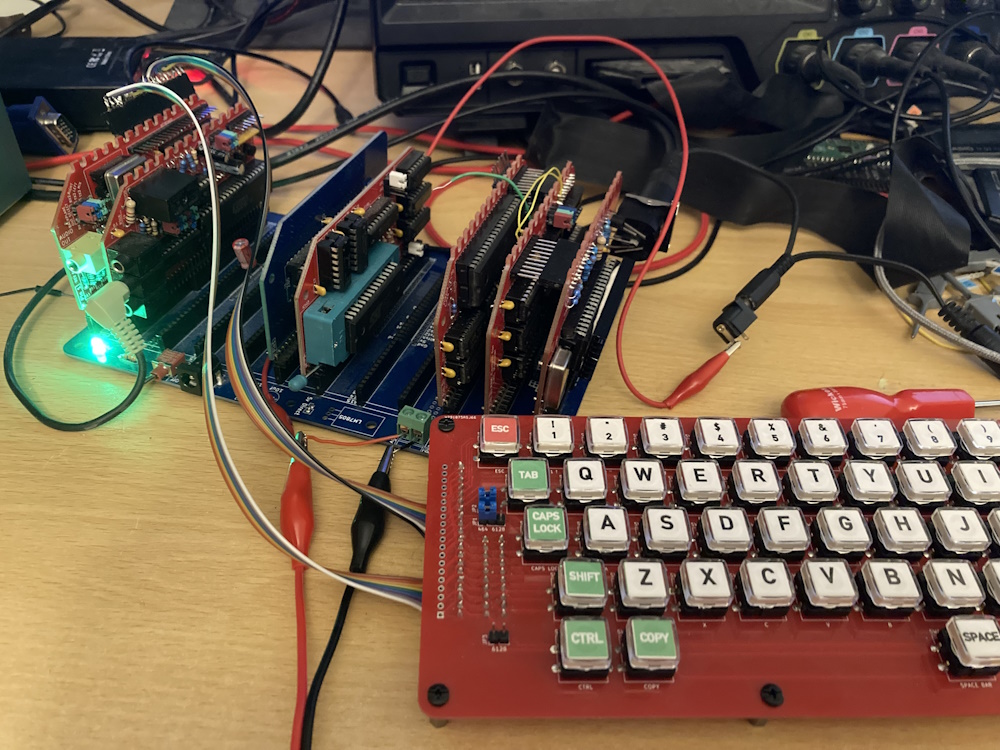

현재 모듈은 약간 수정된 RC2014 Pro 백플레인에 맞도록 설계되었습니다. 아래 텍스트에서는 프로젝트의 현재 상태, 이를 실행하는 데 필요한 해결 방법 및 기본 빌드 세부 정보를 설명합니다. 프로젝트의 작업 진행 상태로 인해 이 문서는 의도적으로 간결하게 작성되었습니다.

이 프로젝트는 핀 헤더/소켓을 사용하여 하위 시스템(비디오 RAM 하위 시스템 및 IO 사운드 하위 시스템) 내의 모듈을 연결합니다. 이를 위해서는 평소보다 긴 핀 헤더가 필요합니다.

이것은 약간 수정된 RC2014 Pro 백플레인입니다. CPC 모듈러는 비디오 RAM 하위 시스템과 로컬 데이터 버스용 IO-Sound 하위 시스템 내에서 D8~D15 라인을 사용합니다. 그러므로:

이 섹션 사이의 D8~D15 라인을 분리해야 합니다.

이것은 약간 수정된 RC2014 "Z80 CPU 모듈"입니다. 가감:

보드의 저항을 다른 값으로 교체해야 합니다. 2.2k 옴이 잘 작동합니다.

이 보드에는 512Kb NORFLASH가 포함되어 있습니다. 여기에는 플래시를 현장에서 구울 수 있는(테스트되지 않음) 회로가 포함되어 있습니다. 구성:

LK4의 핀 2와 LK5의 핀 2를 연결하는 점퍼를 설치해야 합니다.

플래시 굽기를 활성화하려면 링크 LK1, LK2 및 LK3을 설치하십시오. 그렇지 않으면 열어 두십시오.

플래시에 쓰기 위한 메모(회로도 파일에서 가져옴)는 다음과 같습니다.

!!! 표준 CPC 시스템에서는 메모리 쓰기를 비활성화할 수 있는 방법이 없습니다. 따라서 WRITE_EN이 활성화된 동안 ROM에 수행하는 모든 메모리 쓰기는 RAM에도 기록됩니다.

그러나 ROM은 모든 메모리 뱅크에 매핑되므로 어느 정도 유연성이 추가됩니다. 또한 쓰기가 활성화되어 있는 동안에는 ROM에서 읽기가 비활성화된다는 점에 유의하십시오. 이는 ROM이 활성화된 동안 ROM '아래' RAM에서 읽을 수 있음을 의미합니다.

내가 권장하는 프로그래밍 절차는 비디오 RAM 주소를 사용하여 ROM에 쓰는 것이지만 해당 메모리 범위에 의미 있는 데이터가 포함되어 있지 않으면 ROM은 뱅크 1(&4000-&7fff)의 주소를 사용하여 쓸 수 있습니다. (기록할 데이터가 이미 이 주소 범위에 있는 경우 프로그래머는 간단히 데이터(RAM)를 읽은 다음 동일한 주소에서 쓰기(ROM)를 할 수 있습니다. 하지만 ROM에 전송되는 명령에는 주의가 필요합니다. 여전히 아래의 데이터는 삭제됩니다).

프로그래밍할 주소에서 RAM 바이트를 읽습니다.

ROM에 대한 쓰기 활성화를 켜십시오.

필요한 데이터를 ROM에 씁니다.

ROM에 대한 쓰기 활성화를 끄십시오.

원본 데이터를 다시 ROM에 씁니다.

ROM(NORFLASH)은 최대 31개의 ROMS와 펌웨어 ROM을 수용할 수 있습니다. 칩을 프로그래밍할 때 펌웨어는 슬롯 31(주소 &7c000에서 시작)에 들어가야 합니다. BASIC(설치된 경우)은 슬롯 0(주소 &00000)에 들어가야 합니다. ROM 슬롯은 &4000바이트마다 위치합니다(예: &00000, &04000, &08000, &0C000, &10000 등).

XGPro 소프트웨어로 ROM을 굽는 경우:

Select IC를 사용하여 사용 중인 IC(SST39FS040)를 선택합니다.

LOAD 도구 모음 버튼을 클릭합니다.

로드할 파일을 선택합니다.

파일 형식: 바이너리(.ROM 파일용)

지역으로: 기본값

로드 모드: 일반

파일 시작 주소에서: 0000

To Buffer Start Addr: ROM 슬롯 시작 주소(펌웨어의 경우 &7C000, BASIC의 경우 &00000)

파일 로드 시 버퍼 지우기: '기본값으로 버퍼 지우기' 옵션은 이전에 로드된 데이터를 덮어씁니다 ! XGPro에 로드된 첫 번째 ROM에 사용합니다(전체 ROM을 초기화합니다). 다른 모든 ROM의 경우 '비활성화'를 선택합니다(선택한 슬롯에만 데이터를 로드함).

확인을 클릭하고 파일이 올바른 주소에 로드되었으며 덮어쓰여지지 않았는지 확인하세요.

PROG(도구 모음)를 클릭합니다.

프로그램을 클릭합니다.

이 보드에는 게이트 어레이와 비디오 출력이 포함되어 있습니다.

JP901에서는 DISPEN 및 HSYNC 신호가 RAM 제어 보드의 해당 헤더에 있는 신호와 비교하여 교체됩니다. 이는 RAM 제어 보드에서 수정하는 것이 가장 좋습니다(아래 참조).

비디오 출력 회로는 CPC464의 회로이지만 어떻게 든 CPC6128의 구성 요소 값을 사용했지만 '6128의 커패시터는 뺍니다. 이는 아마도 큰 차이를 가져오지 않을 것입니다.

테스트에서는 Amstrads에 일반적으로 사용하는 것과 동일한 SCART-HDMI 어댑터를 사용하고 있지만 여기서는 흑백 이미지가 표시되거나 이미지가 전혀 표시되지 않습니다. 이는 케이블에 사용되는 PSU와 어댑터 사이의 문제인 것으로 보입니다. CPC 모듈러 보드에서 케이블로 5V 전원을 공급하면 문제를 해결할 수 있습니다.

보드에는 40007 및 40010 게이트 어레이 모두에 대한 설치 공간이 포함되어 있습니다(40008도 작동해야 함). 공간을 절약하기 위해 발자국이 겹쳐집니다. 두 행의 핀을 분리하고 그 사이의 웨빙을 제거하여 두 행의 소켓을 모두 포함할 수 있어야 하지만 발자국이 너무 가까워서 쉽게 할 수 없습니다.

DIN 소켓의 설치 공간에 있는 구멍이 너무 작습니다.

이 보드는 비디오 데이터 버스와 CPU 데이터 버스 사이의 링크를 수용하고 신호를 마사지하여 SRAM 메모리에 적합하게 만들고 64k(테스트되지 않음)보다 큰 메모리에 필요한 옵션 구성 요소를 수용합니다.

/RAMOE 구동 회로가 올바르지 않습니다. 문제를 해결하려면:

U192 핀 1과 13 사이의 트레이스를 잘라냅니다.

U192 핀 11과 U193 핀 1 사이의 트레이스를 잘라냅니다.

U192 핀 1과 U195 핀 9 사이에 와이어를 설치합니다.

U195 핀 8과 U193 핀 1 사이에 와이어를 설치합니다.

비디오 보드에 대해 언급한 것처럼 DISPEN 및 HSYNC 핀은 보드 사이의 커넥터에서 교체됩니다. 이 문제를 해결하려면:

J1 핀 2와 J2 핀 2 사이의 트레이스를 잘라냅니다.

J1 핀 3과 J2 핀 3 사이의 트레이스를 잘라냅니다.

J1 핀 2와 J2 핀 3 사이에 와이어를 설치합니다.

J1 핀 3과 J2 핀 2 사이에 와이어를 설치합니다.

<= 64k RAM을 사용하려면 링크 LK5, LK6 및 LK7을 설치하세요. 그렇다면 IC118 및 U194를 삽입하지 마십시오.

64k 이상의 RAM을 사용하려면 LK5, LK6, LK7을 열어두고 IC118 및 U194를 설치하십시오. IC118은 표준 Amstrad HAL/PAL입니다.

/RAMOE를 구동하는 올바른 회로는 다음과 같습니다.

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

텍스트 형식: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD는 U195 핀 8에서 공급될 수 있습니다.

이 보드에는 6845 CRTC, 주소 멀티플렉서 및 512Kb SRAM이 포함되어 있습니다. 여기에는 문제가 없으며 구성이 필요하지 않습니다.

필요한 경우 CURSOR 및 LPEN에 헤더를 설치할 수 있습니다. 아마도 그렇지 않을 것입니다.

이 보드에는 8255 PIO 및 테이프 인터페이스가 포함되어 있습니다. I/O 주소를 구성할 수 있도록 납땜 링크와 점퍼가 설치됩니다.

보드는 IO 보드가 '위/앞'에 장착될 수 있도록 설계되었지만 릴레이가 너무 커서 이를 허용하지 않습니다. 따라서 J902를 보드 후면에 장착하는 것이 좋습니다(이것은 사운드 보드에 대한 커넥터입니다).

보드 뒷면에서 주소 핀 바로 위에 있는 납땜 링크를 찾으세요. 각 링크에서 '상위' 주소 패드(A7(sic) ~ A15로 표시됨)를 중앙 패드에 납땜해야 합니다. '낮은' 주소 패드(A0..A7)는 중앙 패드에 연결되어서는 안 됩니다.

보드 전면에서 U1과 D302 사이에 있는 링크를 찾으세요. A3이라고 표시된 링크의 경우 '낮은' 링크(중앙 핀으로)를 점퍼해야 하고 다른 링크(A2, A4, A5, A6, A7)의 경우 높은 링크(중앙 핀으로)를 점퍼해야 합니다.

C315와 J901 사이에 있는 링크를 찾으세요. 잭 소켓으로 전달되는 신호와 백플레인으로 전달되는 신호를 구성합니다. 권장되는 설정은 다음과 같습니다.

INT(ernal)와 TO, TI 및 /MO(Tape Out, Tape In 및 Motor)용 중간 핀 사이에 링크를 설치합니다.

/EXP 링크를 열어두세요.

J901을 사용하면 다양한 8255 입력 신호에 액세스할 수 있습니다. 기본적으로 이러한 모든 줄에는 풀업이 있으므로 무시할 수 있습니다.

RG0, RG1, RG2는 지역 설정입니다.

VHz는 비디오 출력을 위한 50Hz/60Hz 설정입니다.

/EXP는 /EXP 신호입니다.

PBSY는 프린터 사용 중 신호입니다. CPC 모듈러에는 병렬 포트가 포함되어 있지 않습니다. 원하는 경우 이 신호를 확장에 사용할 수 있습니다.

J1, J2 및 J3은 테이프 I/O 잭입니다. J3(모터)는 2.5mm 잭 소켓이어야 하지만 설치 공간은 3.5mm 소켓용입니다.

이 보드에는 AY-3-8910 사운드 생성기 및 관련 출력과 키보드 및 조이스틱 커넥터가 포함되어 있습니다.

IO 보드에 대해 언급한 바와 같이, 실크스크린에 표시된 것처럼 보드 간 커넥터(J902)를 후면이 아닌 이 보드의 상단에 장착해야 합니다.

이 보드에는 AY의 클록 입력을 위해 온보드 발진기를 사용할 수 있는 기능이 있습니다. CPC 모듈러: X1을 생략하고 JP3의 CLK2 끝에 점퍼를 설치합니다(백플레인을 통해 전송되는 게이트 어레이의 클록 신호를 사용하도록 보드를 구성함).

J103(오디오 출력 잭) 위의 점퍼를 사용하면 다양한 오디오 신호를 다양한 백플레인 핀으로 보낼 수 있습니다. 대부분의 경우 이는 열어 둘 수 있습니다. 일부 설정은 IO 보드의 백플레인을 통해 라우팅되는 테이프 신호와 충돌할 수 있습니다.

오디오 잭이 설치된 경우 LEFT 및 RIGHT 신호는 백플레인으로 전송되지 않습니다(그렇게 구성한 경우 - 이전 항목 참조). 그러나 오디오 MIX는 계속 전송됩니다(그렇게 구성된 경우).

CP2는 키보드 커넥터입니다. 이는 원래 Amstrad CPC464(PCB 키보드)와 동일한 핀아웃을 사용합니다.

J102는 조이스틱 커넥터입니다. 여기의 커넥터는 약간 '내부'에 장착되어 다음 소켓의 PCB를 단락시킬 수 있습니다.

할/팔:

원본 코드: https://www.cpcwiki.eu/index.php/PAL16L8

WiP 교체: https://github.com/Bread80/GreenHAL

WiP 교체: https://www.cpcwiki.eu/forum/index.php?msg=231084

게이트 어레이:

WiP FPGA 기반 대체: https://github.com/codedchip/AMSGateArray

ROM 이미지: https://www.cpcwiki.eu/index.php/ROM_List

라이센스: CERN-OHL-P

저작권 © 마이크 서튼, 2023

홈페이지: https://bread80.com

소셜미디어(마스토돈): https://mstdn.social/@bread80

여기 외에는 유용한 것이 없습니다. 하지만 지금까지 해냈다면 아마도 계속해서 나아갈 것입니다.

TX/RX=사운드(왼쪽, 오른쪽) **점퍼됨(옵션) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC(IO로 비디오) USR4=

/WAIT=READY(이미 완료되었습니다!) CLOCK2=/CPU_ADDR(RAM 보드, 사운드용 1MHz 클럭) RX2=테이프 인 **점퍼됨(옵션) TX2=테이프 아웃 **점퍼됨(옵션) USR5=RAMDIS MOVED USR6=/ RAMRD 이동됨 USR7=모터 **점퍼됨(옵션)

D8-D15=비디오 버스

D8-D15=IO 버스???제어 신호???

위치=기본 RC2014 헤더 핀 중앙 위 45.72mm의 맨 위 구멍 행, 가장 왼쪽 핀 = A9와 A8 사이의 중간 지점 오른쪽의 핀 1 1 GND 2 HSYNC(in) 3 DISPEN(in) 4 GND 5 /RAS( 출력) 6 /CAS(출력) 7 /MWE(출력) 8 /CCLK(출력) 9 /244EN(출력) 10 GND

위치=구멍의 맨 위 줄 @ 확장된 헤더 핀 중앙 위 43.18mm, 가장 왼쪽 핀 = 왼쪽 핀 1의 D2와 D3 핀 사이의 중간 지점, 모든 접지는 맨 위 행에 있습니다. 1=GND 2=HSYNC(입력) 3=DISPEN(입력) 4=/CCLK(출력) 5=/XCPU_ADDR(출력) 6=/RAMCS(출력) 7=GND 8=/RAMOE(출력) 9=GND 10 =/RAMWE(출력) 11=RAMA14(출력) 12=RAMA15(출력) 13=RAMA16(출력) 14=RAMA17(출력) 15=GND 16=RAMA18(출력)

1=GND 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=GND

Amstrad/MX4 핀아웃

접지음 Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK 준비 Y Y BRST RSET Y? 와이? 와이? 와이? 와이? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS 커서 Y LPEN Y EXP Y Y GND CLK4 Y Y

추가(비디오-RAM): RD7..RD0 Y Y Y RAS Y Y CAS Y Y MWE Y Y 244EN Y Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y (24줄)

추가(비디오-RAM 및 IO-사운드): CPU_ADDR(1MHz) Y Y Y VSYNC Y Y Y (2줄)

추가(IO-사운드): PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y LEFT Y RIGHT Y (20줄)

디스크: 내부적으로 약 14라인 필요

비디오/RAM: 50 + 24 + 2 = 76줄! 총. 덜 필요함: 총 69개(70개 + 예비 1개!) IO/사운드: 50 + 20 + 2 = 총 72개 라인. 덜 필요함: 총 50개(예비 부품 포함) 디스크: 50 + 14 = 총 64개 라인

참고: 76핀 에지 커넥터: 보드 폭 = 99.06mm

보드: MX4 섹션: CPU ROM 예비 RC2014 에지 커넥터

비디오 섹션(게이트 어레이): 비디오 RAM RAM 제어

비디오 섹션(RP2040): 비디오 신호 RAM 트랜시버

디스크 섹션: 컨트롤러 커넥터/버퍼

IO 사운드 섹션: PPI AY 테이프 오디오 앰프/믹서