메모:

이 프로젝트에 대한 문서는 새로 디자인된 Caravel 버전의 변경 사항을 반영하기 위해 업데이트되고 있습니다.

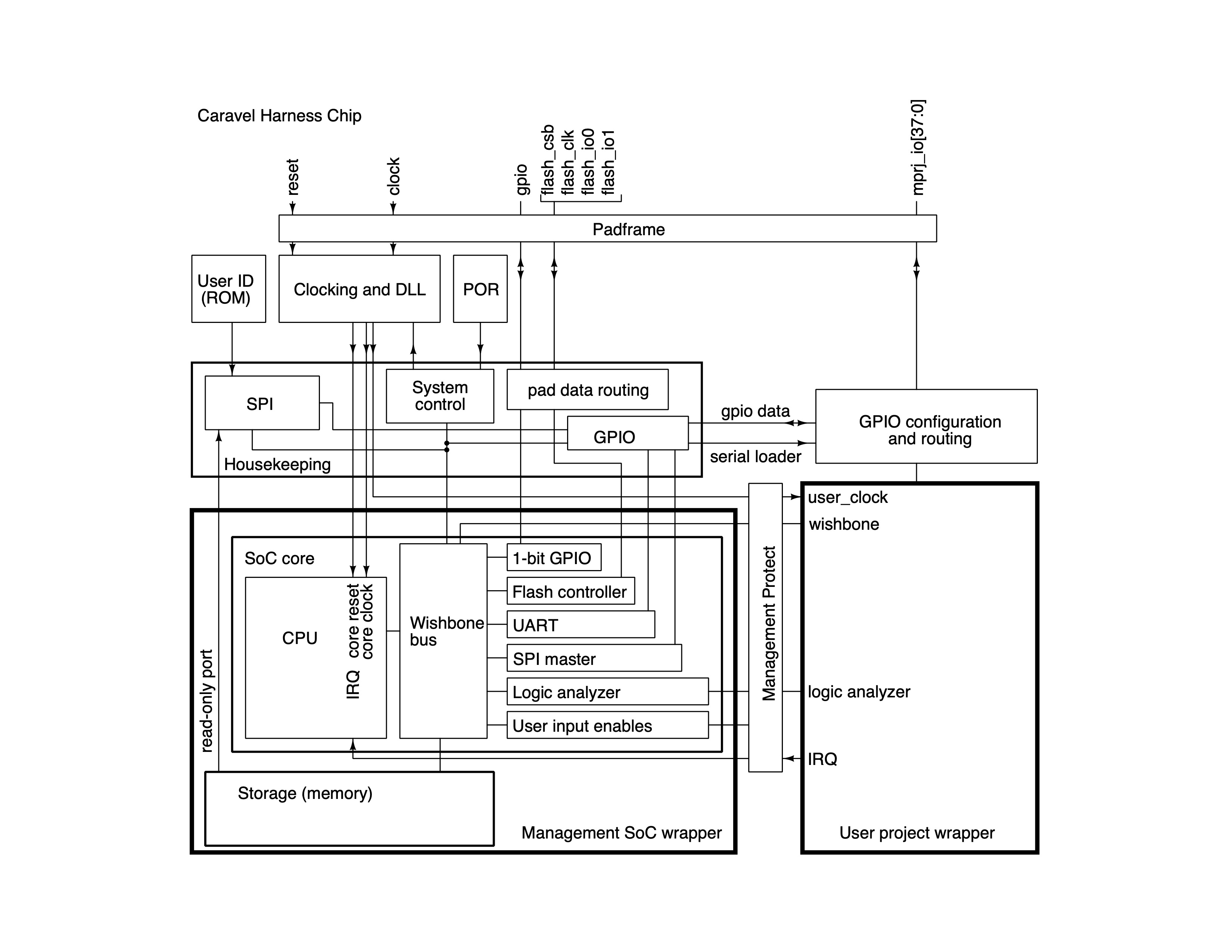

Caravel은 SkyWater Technologies의 Sky130 노드를 기반으로 하는 Efabless Open MPW 및 ChipIgnite 셔틀을 위한 템플릿 SoC입니다. 현재 SoC 아키텍처는 다음과 같습니다.

데이터시트와 자세한 문서는 여기에 있습니다.

Caravel은 하네스 프레임과 관리 영역 및 사용자 프로젝트 영역을 위한 드롭인 모듈용 래퍼 2개로 구성됩니다.

하네스 자체에는 클로킹 모듈, DLL, 사용자 ID, 하우스키핑 SPI, POR 및 GPIO 제어가 포함되어 있습니다.

GPIO 처리가 관리 SoC에서 SPI로 이동되었습니다. SPI는 위시본 인터페이스를 얻습니다. 관리 SoC는 4핀 SPI 인터페이스를 인계받는 것이 아니라 위시본을 통해 SPI와 통신합니다.

ID와 같은 새 블록에는 각 GPIO에 대한 전원 공급 모드가 있습니다. 텍스트 파일로 구성할 수 있습니다. SPI 핀은 시작 시 작동하도록 고정되어 있습니다.

전원을 켜면 SPI가 자동으로 GPIO를 구성합니다. SPI와 위시본 버스 모두에서 수동 로드가 가능합니다.

하네스 내부를 제외한 관리 SoC 외부의 모든 기능은 "하우스키핑"이라는 하나의 대형 모듈에 통합됩니다. 여기에는 GPIO 핀 1~4를 통해 패드프레임에 연결된 "전면 도어" SPI 인터페이스와 관리 SoC에 연결된 "후면 도어" 위시본 인터페이스와 함께 포함된 모든 기능에 대한 여러 레지스터가 포함됩니다. 관리 Soc는 하우스키핑 모듈을 위해 0x26000000에 메모리 블록을 예약합니다. 하우스키핑 모듈은 바이트 전체 SPI 레지스터 데이터를 사용하는 인터페이스를 통해 관리 SoC와 데이터를 교환합니다. 소형 상태 머신은 4개의 연속된 위시본 주소를 읽고 주소 디코더는 해당 SPI 레지스터를 결정합니다. 상태 머신은 확인 신호를 반환하기 전에 4바이트가 모두 처리될 때까지 SoC를 정지합니다.

관리 영역은 별도의 저장소로 구현된 드롭인 모듈입니다. 일반적으로 타이머, uart 및 gpio와 같은 여러 주변 장치를 포함하는 RISC-V 기반 SoC가 포함됩니다. 관리 영역에서는 다음 작업에 사용할 수 있는 펌웨어를 실행합니다.

관리 영역에서는 관리 SoC용 SRAM을 구현합니다.

관리 코어의 기본 인스턴스화는 여기에서 찾을 수 있습니다. 자세한 내용은 관리 코어 설명서를 참조하세요.

사용자 공간입니다. 2.92mm x 3.52mm 제한된 실리콘 면적과 고정된 수의 I/O 패드 38 및 전원 패드 4 를 갖습니다.

사용자 공간은 관리 SoC에서 제공하는 다음 유틸리티에 액세스할 수 있습니다.

38128 로직 분석기 프로브 귀하의 영역은 전체 사용자 공간이므로 자유롭게 프로젝트를 추가하거나 다른 매크로를 생성하여 별도로 강화한 다음 디지털 프로젝트의 경우 user_project_wrapper 에 삽입하거나 아날로그 프로젝트의 경우 user_project_analog_wrapper 에 삽입하세요.

사용자 공간을 위한 디지털 프로젝트를 구축하는 경우 caravel_user_project에서 샘플 프로젝트를 확인하세요.

OpenLANE을 사용하여 설계를 강화하려면 이 README의 지침을 따르세요.

디지털 사용자 프로젝트는 다음 요구 사항을 준수해야 합니다.

user_project_wrapper 입니다.user_project_wrapper Digital Wrapper Pin Order에 정의된 핀 순서를 따릅니다.user_project_wrapper Digital Wrapper 고정 구성의 고정 디자인 구성을 준수합니다.사용자 공간을 위한 아날로그 프로젝트를 구축하는 경우 caravel_user_project_analog에서 샘플 프로젝트를 확인하세요.

아날로그 사용자 프로젝트는 다음 요구 사항을 준수해야 합니다.

user_analog_project_wrapper 입니다.user_analog_project_wrapper 는 빈 아날로그 래퍼를 사용합니다.user_analog_project_wrapper 빈 아날로그 래퍼의 동일한 핀 순서와 배치를 준수합니다. 저장소에 무엇인가를 커밋하기 전에 make compress 실행했는지 확인하십시오. gds/user_project_wrapper.gds 의 두 버전 중 하나는 압축되고 다른 하나는 압축되지 않은 버전을 사용하지 마세요.

도구 및 버전 관리에 대한 자세한 내용은 tool-versioning.rst를 참조하세요.

gds/ : 프로젝트에서 사용되거나 생성된 모든 gds 파일을 포함합니다.def : 프로젝트에서 사용되거나 생성된 모든 def 파일을 포함합니다.lef/ : 프로젝트에서 사용되거나 생성된 모든 lef 파일을 포함합니다.mag/ : 프로젝트에서 사용되거나 생성된 모든 mag 파일을 포함합니다.maglef : 프로젝트에서 사용되거나 생성된 모든 maglef 파일을 포함합니다.spi/lvs/ : 프로젝트에서 사용되거나 생성된 모든 spice 파일을 포함합니다.verilog/dv : 모든 시뮬레이션 테스트 벤치와 실행 방법이 포함되어 있습니다.verilog/gl/ : 합성/정교한 넷리스트를 모두 포함합니다.verilog/rtl : 모든 Verilog RTL과 소스 파일을 포함합니다.openlane/<macro>/ : 프로젝트에서 openlane을 실행하는 데 사용되는 모든 구성 파일을 포함합니다.info.yaml : 이 예시에 필요한 모든 정보를 포함합니다. user_project_wrapper에 대한 합성된 게이트 레벨 넷리스트뿐만 아니라 정교한 캐러벨 넷리스트를 가리키고 있는지 확인하십시오.메모:

디자인을 강화하기 위해 openlane을 사용한다면,verilog/gldef/lef/gds/magmaglef디렉토리는 openlane에 의해 자동으로 채워져야 합니다.

mpw-one 테이프아웃에 사용된 캐러벨은 mpw-one-final을 확인하세요.

>make ship 실행하는 것이 더 이상 필요하지 않습니다.