***Este projeto é um trabalho inacabado em andamento. Atualmente possui bugs e nem todos os recursos foram testados!

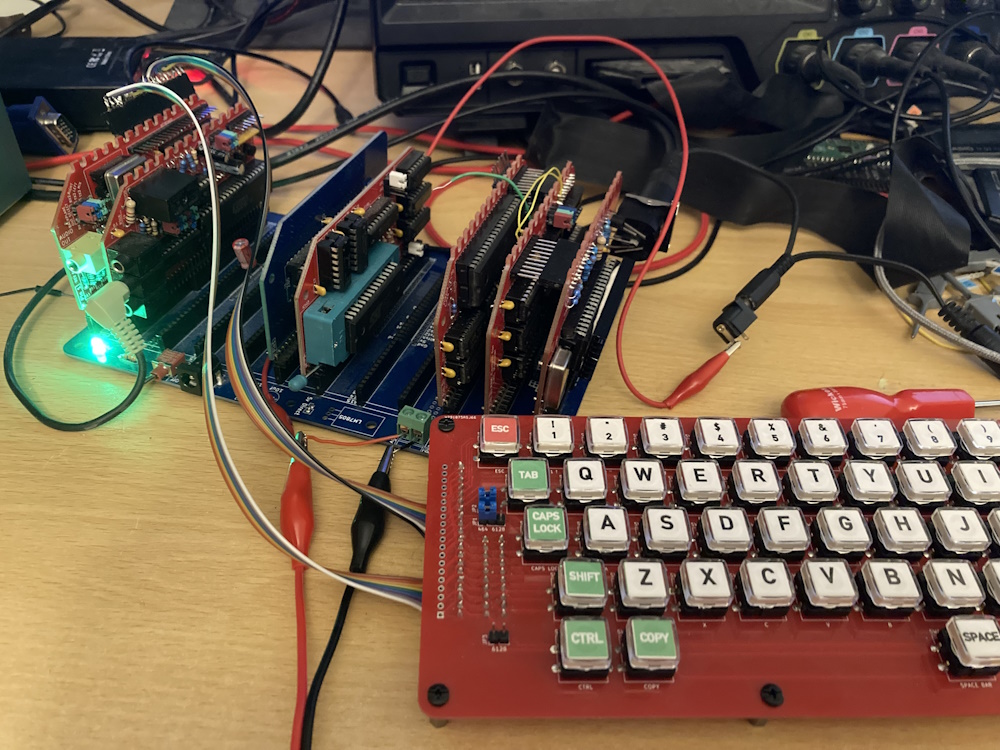

Os módulos atuais são projetados para caber em um backplane RC2014 Pro ligeiramente modificado. No texto abaixo explicarei o status atual do projeto, soluções alternativas necessárias para colocá-lo em execução e detalhes básicos de construção. Devido ao status do trabalho em andamento do projeto, este documento será intencionalmente conciso.

O projeto usa cabeçalho/soquete de pinos para conectar módulos dentro de subsistemas (o subsistema de vídeo-RAM e o subsistema de som IO). Isso requer um cabeçalho de pino mais longo do que o normal.

Este é um backplane RC2014 Pro ligeiramente modificado. O CPC Modular usa as linhas D8 a D15 tanto no subsistema de vídeo-RAM quanto no subsistema IO-Sound para barramentos de dados locais. Portanto:

Você precisará cortar as linhas D8 a D15 entre essas seções.

Este é um RC2014 "Módulo CPU Z80" ligeiramente modificado. Modificação:

Os resistores da placa precisarão ser substituídos por um valor diferente. 2,2k ohm deve funcionar bem.

Esta placa contém NORFLASH de 512Kb. Inclui circuitos para permitir que o flash seja queimado in situ (não testado). Configuração:

Um jumper precisa ser instalado conectando o pino 2 do LK4 e o pino 2 do LK5.

Para habilitar a gravação de flash, instale os links LK1, LK2 e LK3. Caso contrário, deixe aberto.

Minhas notas para escrever no Flash (retiradas do arquivo esquemático) são:

!!! Não há como desabilitar gravações de memória no sistema CPC padrão. Portanto, QUALQUER gravação de memória que fizermos na ROM enquanto WRITE_EN estiver ativo também gravará na RAM.

No entanto, como a ROM mapeia para todo e qualquer banco de memória, isso adiciona uma certa flexibilidade. Observe também que a leitura da ROM está desabilitada enquanto a escrita está habilitada. Isso significa que podemos ler a RAM 'abaixo' da ROM enquanto a ROM está ativa.

Meu procedimento de programação recomendado é gravar na ROM usando endereços de RAM de vídeo; no entanto, a ROM pode gravar usando endereços no banco 1 (& 4000-& 7fff) se esse intervalo de memória não contiver dados significativos. (Se os dados a serem gravados já estiverem neste intervalo de endereços, o programador pode simplesmente ler os dados (RAM) e depois escrever (ROM) no mesmo endereço. É preciso ter cuidado com os comandos enviados para a ROM, pois estes ainda irá descartar os dados abaixo).

Leia o byte de RAM no endereço a ser programado.

Ative a habilitação de gravação para a ROM

Grave os dados necessários na ROM.

Desative a habilitação de gravação para a ROM

Grave os dados originais de volta na ROM.

A ROM (NORFLASH) pode conter até 31 ROMS mais a ROM do firmware. Ao programar o chip, o Firmware precisa entrar no slot 31 (começando no endereço &7c000). BASIC (se instalado) precisa ir para o slot 0 (endereço &00000). Os slots ROM estão localizados a cada &4000 bytes, ou seja, &00000, &04000, &08000, &0C000, &10000 etc.

Se estiver gravando ROMs com o software XGPro:

Use Select IC para selecionar o IC que está sendo usado (SST39FS040).

Clique no botão CARREGAR da barra de ferramentas.

Selecione o arquivo a ser carregado.

Formato de arquivo: Binário (para arquivos .ROM)

Para região: padrão

Modo de carregamento: Normal

Do endereço inicial do arquivo: 0000

To Buffer Start Addr: O endereço inicial do slot ROM (&7C000 para o firmware, &00000 para BASIC)

Limpar buffer ao carregar arquivo: A opção 'Limpar buffer com padrão' irá sobrescrever quaisquer dados carregados anteriormente! Use isto para a primeira ROM carregada no XGPro (que inicializará toda a ROM). Para todas as outras ROMs, selecione 'Desativar' (que carregará os dados apenas no slot selecionado).

Clique em OK e verifique se seus arquivos foram carregados nos endereços corretos e não foram substituídos.

Clique em PROG (barra de ferramentas)

Clique em Programa.

Esta placa abriga o conjunto de portas e a saída de vídeo.

No JP901 os sinais DISPEN e HSYNC são trocados em comparação com aqueles no cabeçalho equivalente na placa RAM-Control. Isso é melhor corrigido na placa RAM-Control (veja abaixo).

O circuito de saída de vídeo é o do CPC464, mas, de alguma forma, usei valores de componentes do CPC6128, mas menos os capacitores do '6128. Isso provavelmente não faz uma diferença significativa.

Nos meus testes estou usando o mesmo adaptador SCART para HDMI que normalmente uso para Amstrads, mas aqui ele mostra uma imagem em preto e branco, ou nenhuma imagem. Este parece ser um problema entre a PSU usada pelo cabo e o adaptador. Ele pode ser consertado alimentando o cabo com alimentação de 5 V da placa modular CPC.

A placa inclui pegadas para matrizes de portas 40007 e 40010 (e uma 40008 também deve funcionar). As pegadas se sobrepõem para economizar espaço. Você deve ser capaz de incluir soquetes para ambos, separando as duas fileiras de pinos e removendo a correia entre eles; no entanto, as pegadas estão um pouco próximas demais para fazer isso facilmente.

Os orifícios na área do soquete DIN são um pouco pequenos.

Esta placa abriga o link entre o barramento de dados de vídeo e o barramento de dados da CPU, massageia os sinais para torná-los adequados para a memória SRAM e abriga os componentes opcionais necessários para memórias maiores que 64k (não testadas).

O circuito de condução /RAMOE está incorreto. Para consertar:

Corte o traço entre os pinos 1 e 13 do U192

Corte o traço entre U192 pino 11 e U193 pino 1

Instale um fio entre o pino 1 de U192 e o pino 9 de U195

Instale um fio entre o pino 8 de U195 e o pino 1 de U193

Conforme observado para a placa de vídeo, os pinos DISPEN e HSYNC são trocados nos conectores entre as placas. Para corrigir isso:

Corte o traço entre J1 pino 2 e J2 pino 2

Corte o traço entre J1 pino 3 e J2 pino 3

Instale um fio entre J1 pino 2 e J2 pino 3

Instale um fio entre J1 pino 3 e J2 pino 2

Para usar <= 64k RAM, instale os links LK5, LK6 e LK7. Nesse caso, NÃO insira IC118 e U194

Para usar > 64k RAM, deixe LK5, LK6, LK7 abertos e instale IC118 e U194. IC118 é um Amstrad HAL/PAL padrão.

O circuito correto para acionar /RAMOE é:

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

Em formato de texto: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD pode ser proveniente do pino 8 do U195.

Esta placa abriga o 6845 CRTC, multiplexadores de endereço e SRAM de 512Kb. Não há problemas aqui e nenhuma configuração é necessária.

Cabeçalhos podem ser instalados para CURSOR e LPEN, se necessário. Provavelmente não são.

Esta placa abriga o 8255 PIO e a interface de fita. Links de solda e jumpers são instalados para tornar o endereço de E/S configurável:

A placa foi projetada de forma que a placa IO pudesse ser montada 'acima/na frente' dela, mas o relé é muito alto para permitir isso. Assim: recomendo que você monte o J902 na parte traseira da placa (este é o conector da placa de som).

Na parte traseira da placa, encontre os links de solda logo acima dos pinos de endereço. Em cada link você precisa soldar o bloco de endereço 'alto' (rotulado A7(sic) a A15) ao bloco central. Os blocos de endereço 'baixos' (A0..A7) NÃO devem ser conectados aos blocos centrais.

Na frente da placa encontre os links localizados entre U1 e D302. Você precisa fazer o jumper do link 'baixo' (para o pino central) para o link rotulado como A3, e o link alto (para o pino central) para os outros (A2, A4, A5, A6, A7).

Encontre os links localizados entre C315 e J901. A configuração de quais sinais são direcionados para os soquetes jack e quais são direcionados para o backplane. A configuração recomendada é:

Instale links entre os pinos INT (internos) e intermediários para TO, TI e /MO (Tape Out, Tape In e Motor).

Deixe o link /EXP aberto.

J901 permite acesso a vários sinais de entrada do 8255. Por padrão, todas essas linhas possuem pull-ups e podem ser ignoradas.

RG0, RG1, RG2 são as configurações da região.

VHz é a configuração de 50 Hz/60 Hz para saída de vídeo.

/EXP é o sinal /EXP.

PBSY é sinal de impressora ocupada. O CPC Modular não inclui porta paralela. Este sinal pode ser usado para expansão, se desejado.

J1, J2 e J3 são os conectores de E/S de fita. J3 (Motor) deve ser um soquete jack de 2,5 mm, mas o tamanho é para um soquete de 3,5 mm.

Esta placa abriga o gerador de som AY-3-8910 e saídas associadas, além dos conectores de teclado e joystick.

Conforme observado para a placa IO: Você deve montar o conector entre placas (J902) na parte superior desta placa, não na parte traseira, como mostrado na serigrafia.

A placa tem a capacidade de usar um oscilador integrado para a entrada do clock do AY. No CPC Modular: Omita X1 e instale um jumper na extremidade CLK2 do JP3 (que configura a placa para usar o sinal de clock do array de portas enviado através do backplane).

Os jumpers acima do J103 (conector de saída de áudio) permitem que vários sinais de áudio sejam enviados para uma variedade de pinos do backplane. Na maioria dos casos, estes podem ser deixados abertos. Observe que algumas configurações podem entrar em conflito com sinais de fita roteados através do backplane na placa IO.

Se um conector de áudio estiver instalado, os sinais ESQUERDO e DIREITO NÃO serão enviados para o backplane (se configurado para isso - veja o item anterior). No entanto, o MIX de áudio ainda será enviado (se assim configurado).

CP2 é o conector do teclado. Ele usa a mesma pinagem do Amstrad CPC464 original (teclado PCB).

J102 é o conector do joystick. O conector aqui é montado um pouco 'interno' e pode causar curto-circuito em uma PCB no próximo soquete.

HAL/PAL:

Código original: https://www.cpcwiki.eu/index.php/PAL16L8

Substituição WiP: https://github.com/Bread80/GreenHAL

Substituição WiP: https://www.cpcwiki.eu/forum/index.php?msg=231084

Matriz de portas:

Substituição baseada em WiP FPGA: https://github.com/codedchip/AMSGateArray

Imagens ROM: https://www.cpcwiki.eu/index.php/ROM_List

Licença: CERN-OHL-P

Direitos autorais © Mike Sutton, 2023

Site: https://bread80.com

Mídia social (Mastodonte): https://mstdn.social/@bread80

Não há nada útil além daqui. Mas se você chegou até aqui, provavelmente continuará de qualquer maneira.

TX/RX=Som (esquerda, direita) **Jumper (opcional) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC (vídeo para IO) USR4=

/WAIT=READY (já está!) CLOCK2=/CPU_ADDR (placa RAM; clock de 1MHz para som) RX2=Entrada de fita **Jumper (opcional) TX2=Saída de fita **Jumper (opcional) USR5=RAMDIS MOVED USR6=/ RAMRD MOVED USR7 = Motor ** Jumper (opcional)

D8-D15=Barramento de vídeo

D8-D15=Barramento IO ???Sinais de controle???

Posição = linha superior de furos @ 45,72 mm acima do centro dos pinos básicos do cabeçote RC2014, pinos mais à esquerda = ponto médio entre A9 e A8 Pino 1 à direita 1 GND 2 HSYNC (in) 3 DISPEN (in) 4 GND 5 /RAS ( saída) 6 /CAS (saída) 7 /MWE (saída) 8 /CCLK (saída) 9 /244EN (saída) 10 GND

Posição=Fila superior de furos @ 43,18 mm acima do centro dos pinos da plataforma estendida, Pinos mais à esquerda = ponto médio entre os pinos D2 e D3 Pino 1 à esquerda, todos posicionados na linha superior. 1=GND 2=HSYNC (entrada) 3=DISPEN (entrada) 4=/CCLK (saída) 5=/XCPU_ADDR (saída) 6=/RAMCS (saída) 7=GND 8=/RAMOE (saída) 9=GND 10 =/RAMWE (saída) 11=RAMA14 (saída) 12=RAMA15 (saída) 13=RAMA16 (saída) 14=RAMA17 (saída) 15=GND 16=RAMA18 (saída)

1=GND 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=GND

Pinagem Amstrad/MX4

GND SOM Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK PRONTO Y Y BRST RSET Y? Sim? Sim? Sim? Sim? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS CURSOR Y LPEN Y EXP Y Y GND CLK4 Y Y

Extra (Vídeo-RAM): RD7..RD0 Y Y Y RAS Y Y CAS Y Y MWE Y Y 244EN Y Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y (24 linhas)

Extra (Vídeo-RAM e IO-Som): CPU_ADDR(1MHz) Y Y Y VSYNC Y Y Y (2 linhas)

Extra (IO-Som): PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y ESQUERDA Y DIREITA Y (20 linhas)

Disco: Aproximadamente 14 linhas necessárias internamente

Vídeo/RAM: 50 + 24 + 2 = 76 linhas! total. Menos desnecessário: 69 no total (70 mais uma sobressalente!) IO/Som: 50 + 20 + 2 = 72 linhas no total. Menos desnecessário: 50 no total (incluindo algumas peças sobressalentes) Disco: 50 + 14 = 64 linhas no total

Notas: conector de borda de 76 pinos: largura da placa = 99,06 mm

Placas: Seção MX4: CPU ROM sobressalente(s) Conector RC2014 Edge

Seção de vídeo (matriz de portas): Controle de RAM de vídeo RAM

Seção de vídeo (RP2040): Transceptor RAM de sinais de vídeo

Seção do disco: conectores/buffers do controlador

Seção de som IO: Amplificador/mixer de áudio de fita PPI AY