UDP Offload Engine คือ IP VHDL ที่ใช้สำหรับการเขียนโปรแกรมฮาร์ดแวร์ FPGA

IP นี้เป็นตัวเร่งสแต็ก UDP-IP และสามารถส่งและรับข้อมูลผ่านลิงก์อีเธอร์เน็ต สแตกนี้สามารถกำหนดค่าได้สูงเพื่อใช้กับอัตราอีเธอร์เน็ตสูงถึง 40Gb/s ด้วยขนาดบัสที่กำหนดค่าได้ นอกจากนี้ยังเป็นแบบโมดูลาร์ ใช้โปรโตคอลต่างๆ และเครื่องมือทดสอบแบบรวมที่สามารถปิดใช้งานได้เพื่อประหยัดทรัพยากร

IP นี้อิงตาม Building Blocks ตามกลยุทธ์ของ Thales ในด้านวิศวกรรม พวกเขาทำหน้าที่พื้นฐานและปล่อยให้เป็นอิสระจากแพลตฟอร์ม/เป้าหมาย ไม่มีการใช้ผู้ผลิตดั้งเดิมในการออกแบบนี้ ทั้งหมดอนุมานได้

สารบัญ

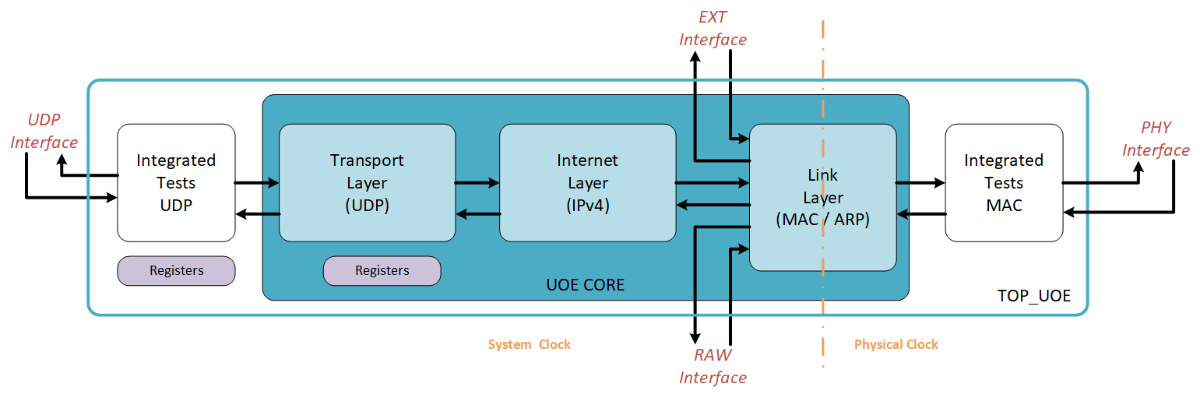

รูปนี้อธิบายสถาปัตยกรรมภายในของ IP เอนทิตีหลักคือโมดูล uoe_core มันถูกห่อหุ้มไว้ใน wrapper ด้านบน top_uoe ซึ่งสร้างอินสแตนซ์ของฟังก์ชันการทดสอบแบบรวมบางส่วนเพิ่มเติม

ส่วนการทำงาน

ส่วนทดสอบในตัว (อุปกรณ์เสริม)

เอกสารฉบับสมบูรณ์ของสแต็กมีอยู่ในคู่มือสถาปัตยกรรม

ขนาดบัสที่กำหนดค่าได้

จัดการโปรโตคอลต่อไปนี้

โปรโตคอลการแก้ไขที่อยู่ (ARP)

ข้อความควบคุมอินเทอร์เน็ต Procotol (ICMP)

คำนึงถึงบัฟเฟอร์บนอินเทอร์เฟซ MAC และการข้ามโดเมนนาฬิกา

ตัวเลือกการกรองสำหรับการรับส่งข้อมูลที่เข้ามา

การใช้รถโดยสารมาตรฐาน

การออกแบบได้รับการสังเคราะห์และนำไปใช้ด้วยพารามิเตอร์ทั่วไปที่แตกต่างกันและสำหรับเป้าหมายหลายรายการโดยไม่อยู่ในบริบท ผลลัพธ์มีอยู่ในหน้าประสิทธิภาพ

repo นี้รวมตัวอย่างการออกแบบต่อไปนี้:

เร็วๆ นี้ ...

หากคุณสนใจที่จะมีส่วนร่วมในโครงการนี้ ให้เริ่มต้นด้วยการอ่านหลักเกณฑ์การบริจาค