***โครงการนี้เป็นงานที่ยังดำเนินการไม่เสร็จ ขณะนี้มีข้อบกพร่องและคุณสมบัติบางอย่างยังไม่ได้รับการทดสอบ!

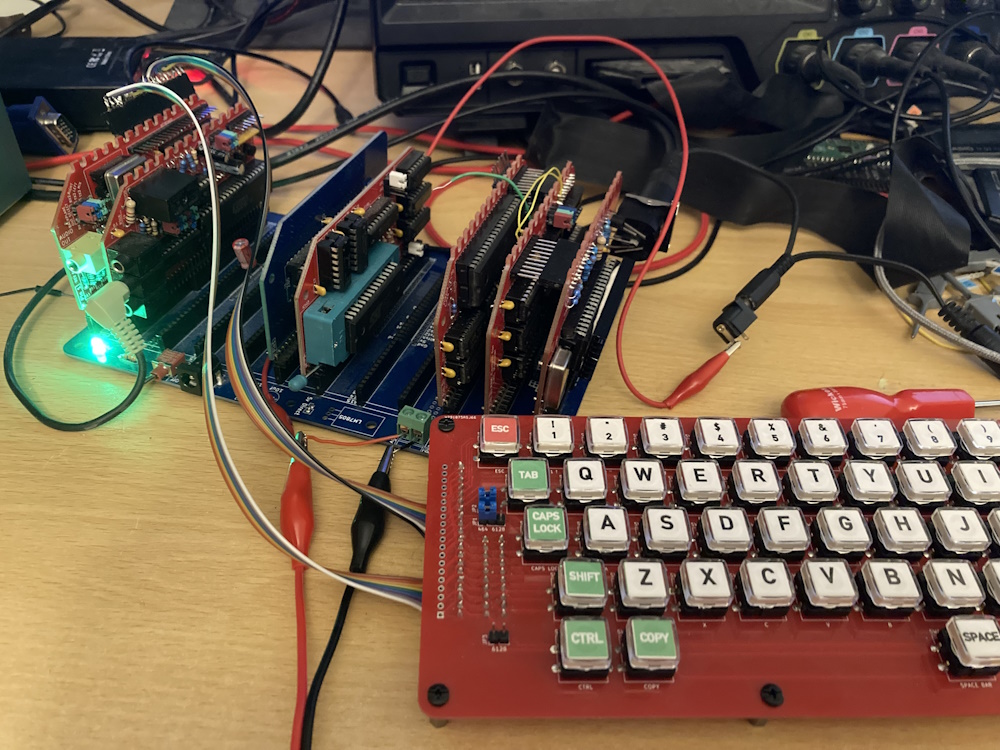

โมดูลปัจจุบันได้รับการออกแบบให้พอดีกับแบ็คเพลน RC2014 Pro ที่มีการปรับเปลี่ยนเล็กน้อย ในข้อความด้านล่าง ฉันจะอธิบายสถานะปัจจุบันของโปรเจ็กต์ วิธีแก้ไขปัญหาที่จำเป็นเพื่อให้โปรเจ็กต์ทำงานได้ และรายละเอียดการสร้างพื้นฐาน เนื่องจากสถานะงานอยู่ระหว่างดำเนินการของโครงการ เอกสารนี้จึงจะถูกเก็บไว้โดยเจตนา

โปรเจ็กต์นี้ใช้ส่วนหัวของพิน/ซ็อกเก็ตเพื่อเชื่อมต่อโมดูลภายในระบบย่อย (ระบบย่อย video-RAM และระบบย่อย IO-sound) ต้องใช้ส่วนหัวของพินที่ยาวกว่าปกติ

นี่คือแบ็คเพลน RC2014 Pro ที่ได้รับการแก้ไขเล็กน้อย CPC Modular ใช้สาย D8 ถึง D15 ทั้งภายในระบบย่อย video-RAM และระบบย่อย IO-Sound สำหรับบัสข้อมูลภายในเครื่อง ดังนั้น:

คุณจะต้องตัดเส้น D8 ถึง D15 ระหว่างส่วนเหล่านี้

นี่คือ RC2014 "Z80 CPU Module" ที่ได้รับการแก้ไขเล็กน้อย การปรับเปลี่ยน:

จะต้องเปลี่ยนตัวต้านทานบนบอร์ดด้วยค่าอื่น 2.2k โอห์มน่าจะทำงานได้ดี

บอร์ดนี้มี NORFLASH 512Kb ประกอบด้วยวงจรเพื่อให้สามารถเบิร์นแฟลชในแหล่งกำเนิดได้ (ยังไม่ได้ทดสอบ) กำหนดค่า:

จำเป็นต้องติดตั้งจัมเปอร์บริดจ์พิน 2 ของ LK4 และพิน 2 ของ LK5

หากต้องการเปิดใช้งานการเบิร์นแฟลช ให้ติดตั้งลิงก์ LK1, LK2 และ LK3 ไม่งั้นก็เปิดทิ้งไว้

บันทึกย่อของฉันสำหรับการเขียนลง Flash (นำมาจากไฟล์แผนผัง) คือ:

- ไม่มีวิธีปิดการใช้งานการเขียนหน่วยความจำบนระบบ CPC มาตรฐาน ดังนั้นหน่วยความจำใดๆ ที่เขียนลง ROM ในขณะที่ WRITE_EN ทำงานอยู่ก็จะเขียนลง RAM ด้วยเช่นกัน

อย่างไรก็ตาม เนื่องจาก ROM จะแมปกับคลังหน่วยความจำทุกแห่ง จึงเพิ่มความยืดหยุ่นในระดับหนึ่ง โปรดทราบว่าการอ่านจาก ROM ถูกปิดใช้งานในขณะที่เปิดใช้งานการเขียน ซึ่งหมายความว่าเราสามารถอ่านจาก RAM 'ใต้' ROM ในขณะที่ ROM ทำงานอยู่

ขั้นตอนการเขียนโปรแกรมที่แนะนำของฉันคือเขียนลงใน ROM โดยใช้ที่อยู่วิดีโอ RAM อย่างไรก็ตาม ROM สามารถเขียนโดยใช้ที่อยู่ในแบงค์ 1 (&4000-&7fff) หากช่วงหน่วยความจำนั้นไม่มีข้อมูลที่มีความหมาย (หากข้อมูลที่จะเขียนอยู่ในช่วงที่อยู่นี้อยู่แล้ว โปรแกรมเมอร์ก็สามารถอ่านข้อมูล (RAM) แล้วเขียน (ROM) ไปยังที่อยู่เดียวกันได้ แต่จะต้องระมัดระวังกับคำสั่งที่ส่งไปยัง ROM เนื่องจากสิ่งเหล่านี้ จะยังคงทิ้งข้อมูลไว้ข้างใต้)

อ่านไบต์ RAM ตามที่อยู่ที่จะตั้งโปรแกรม

เปิดการเปิดใช้งานการเขียนสำหรับ ROM

เขียนข้อมูลที่จำเป็นลงใน ROM

ปิดการเปิดใช้งานการเขียนสำหรับ ROM

เขียนข้อมูลต้นฉบับกลับไปยัง ROM

ROM (NORFLASH) สามารถรองรับ ROMS ได้สูงสุด 31 ROMS พร้อม ROM เฟิร์มแวร์ เมื่อตั้งโปรแกรมชิป เฟิร์มแวร์จะต้องไปที่ช่อง 31 (เริ่มต้นที่ที่อยู่ &7c000) BASIC (หากติดตั้ง) จะต้องเข้าไปในช่อง 0 (ที่อยู่ &00000) สล็อต ROM จะอยู่ทุก ๆ &4,000 ไบต์, เช่น &00000, &04000, &08000, &0C000, &10000 เป็นต้น

หากเบิร์น ROM ด้วยซอฟต์แวร์ XGPro:

ใช้ Select IC เพื่อเลือก IC ที่ใช้งาน (SST39FS040)

คลิกปุ่มแถบเครื่องมือโหลด

เลือกไฟล์ที่จะโหลด

รูปแบบไฟล์: ไบนารี่ (สำหรับไฟล์ .ROM)

ไปยังภูมิภาค: ค่าเริ่มต้น

โหมดโหลด: ปกติ

จากไฟล์เริ่ม Addr: 0000

To Buffer Start Addr: ที่อยู่เริ่มต้นของสล็อต ROM (&7C000 สำหรับเฟิร์มแวร์ &00000 สำหรับ BASIC)

ล้างบัฟเฟอร์เมื่อโหลดไฟล์: ตัวเลือก 'ล้างบัฟเฟอร์ด้วยค่าเริ่มต้น' จะ เขียนทับ ข้อมูลที่โหลดก่อนหน้านี้! ใช้สิ่งนี้สำหรับ ROM แรกที่โหลดลงใน XGPro (ซึ่งจะเริ่มต้น ROM ทั้งหมด) สำหรับ ROM อื่นๆ ทั้งหมด ให้เลือก 'ปิดใช้งาน' (ซึ่งจะโหลดข้อมูลลงในช่องที่เลือกเท่านั้น)

คลิก ตกลง และตรวจสอบว่าไฟล์ของคุณโหลดไปยังที่อยู่ที่ถูกต้องและไม่ถูกเขียนทับ

คลิก PROG (แถบเครื่องมือ)

คลิกโปรแกรม

บอร์ดนี้มีเกตอาร์เรย์และเอาต์พุตวิดีโอ

ใน JP901 สัญญาณ DISPEN และ HSYNC จะถูกสลับเมื่อเปรียบเทียบกับสัญญาณบนส่วนหัวที่เทียบเท่ากันบนบอร์ดควบคุม RAM วิธีนี้จะแก้ไขได้ดีที่สุดบนบอร์ดควบคุม RAM (ดูด้านล่าง)

วงจรวิดีโอเอาท์มาจาก CPC464 แต่อย่างใด ฉันเคยใช้ค่าส่วนประกอบจาก CPC6128 แต่ลบตัวเก็บประจุใน '6128 นี่อาจจะไม่สร้างความแตกต่างอย่างมีนัยสำคัญ

ในการทดสอบของฉัน ฉันใช้อะแดปเตอร์ SCART เป็น HDMI แบบเดียวกับที่ฉันใช้กับ Amstrads แต่ที่นี่แสดงภาพขาวดำหรือไม่มีภาพเลย ปัญหานี้ดูเหมือนจะเป็นปัญหาระหว่าง PSU ที่ใช้โดยสายเคเบิลและอะแดปเตอร์ สามารถแก้ไขได้โดยการจ่ายไฟ 5V ให้กับสายเคเบิลจากบอร์ด CPC Modular

บอร์ดนี้มีรอยเท้าสำหรับทั้งเกตอาร์เรย์ 40007 และ 40010 (และ 40008 ก็ควรใช้งานได้เช่นกัน) รอยเท้าทับซ้อนกันเพื่อประหยัดพื้นที่ คุณควรใส่ซ็อกเก็ตสำหรับทั้งสองแถวได้โดยแยกหมุดสองแถวออกและถอดสายรัดออก อย่างไรก็ตาม รอยเท้าจะอยู่ใกล้กันเกินไปเล็กน้อยจึงจะทำได้ง่าย

รูบนฐานสำหรับช่องเสียบ DIN มีขนาดเล็กเกินไปเล็กน้อย

บอร์ดนี้มีการเชื่อมโยงระหว่างบัสข้อมูลวิดีโอและบัสข้อมูล CPU นวดสัญญาณเพื่อให้เหมาะสำหรับหน่วยความจำ SRAM และเก็บส่วนประกอบเสริมที่จำเป็นสำหรับหน่วยความจำที่มากกว่า 64k (ยังไม่ได้ทดสอบ)

วงจรขับ /RAMOE ไม่ถูกต้อง วิธีแก้ไข:

ตัดรอยระหว่าง U192 พิน 1 และ 13

ตัดรอยระหว่าง U192 พิน 11 และ U193 พิน 1

ติดตั้งสายไฟระหว่าง U192 พิน 1 และ U195 พิน 9

ติดตั้งสายไฟระหว่าง U195 พิน 8 และ U193 พิน 1

ตามที่ระบุไว้สำหรับบอร์ดวิดีโอ พิน DISPEN และ HSYNC จะถูกสลับบนขั้วต่อระหว่างบอร์ด วิธีแก้ไขปัญหานี้:

ตัดร่องรอยระหว่าง J1 พิน 2 และ J2 พิน 2

ตัดร่องรอยระหว่าง J1 พิน 3 และ J2 พิน 3

ติดตั้งสายไฟระหว่าง J1 พิน 2 และ J2 พิน 3

ติดตั้งสายไฟระหว่าง J1 พิน 3 และ J2 พิน 2

หากต้องการใช้ <= 64k RAM ให้ติดตั้งลิงก์ LK5, LK6 และ LK7 หากเป็นเช่นนั้น อย่าใส่ IC118 และ U194

หากต้องการใช้ > 64k RAM ให้เปิด LK5, LK6, LK7 ไว้แล้วติดตั้ง IC118 และ U194 IC118 เป็นมาตรฐาน Amstrad HAL/PAL

วงจรที่ถูกต้องในการขับเคลื่อน /RAMOE คือ:

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

ในรูปแบบข้อความ: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD สามารถหาได้จาก U195 พิน 8

บอร์ดนี้มี 6845 CRTC, แอดเดรสมัลติเพล็กเซอร์ และ 512Kb SRAM ไม่มีปัญหาที่นี่ และไม่จำเป็นต้องกำหนดค่าใดๆ

สามารถติดตั้งส่วนหัวสำหรับ CURSOR และ LPEN ได้หากต้องการ พวกเขาอาจจะไม่

บอร์ดนี้มี 8255 PIO และอินเทอร์เฟซแบบเทป Solder link และจัมเปอร์ได้รับการติดตั้งเพื่อให้สามารถกำหนดค่าที่อยู่ I/O ได้:

บอร์ดได้รับการออกแบบเพื่อให้บอร์ด IO สามารถติดตั้ง 'ด้านบน/ด้านหน้า' ได้ แต่รีเลย์สูงเกินไปที่จะอนุญาต ดังนั้น: ฉันขอแนะนำให้คุณติดตั้ง J902 ที่ด้านหลังของบอร์ด (นี่คือขั้วต่อไปยังบอร์ดเสียง)

ที่ด้านหลังของบอร์ด ให้ค้นหาลิงค์บัดกรีที่อยู่เหนือหมุดที่อยู่ ในแต่ละลิงค์คุณจะต้องประสานแผ่นที่อยู่ 'สูง' (ชื่อ A7 (sic) ถึง A15) เข้ากับแผ่นกลาง แป้นที่อยู่ 'ต่ำ' (A0..A7) จะต้องไม่เชื่อมต่อกับแป้นที่อยู่ตรงกลาง

ที่ด้านหน้าของบอร์ดจะพบลิงค์ที่อยู่ระหว่าง U1 และ D302 คุณต้องจัมเปอร์ลิงก์ 'ต่ำ' (ไปยังพินตรงกลาง) สำหรับลิงก์ที่มีป้ายกำกับ A3 และลิงก์สูง (ไปยังพินกลาง) สำหรับลิงก์อื่นๆ (A2, A4, A5, A6, A7)

ค้นหาลิงก์ที่อยู่ระหว่าง C315 และ J901 การกำหนดค่าว่าสัญญาณใดจะส่งตรงไปยังช่องเสียบแจ็คและส่งสัญญาณไปที่แบ็คเพลน การตั้งค่าที่แนะนำคือ:

ติดตั้งลิงก์ระหว่าง INT(ernal) และพินกลางสำหรับ TO, TI และ /MO (Tape Out, Tape In และ Motor)

เปิดลิงก์ /EXP ทิ้งไว้

J901 อนุญาตให้เข้าถึงสัญญาณอินพุต 8255 ต่างๆ ตามค่าเริ่มต้น บรรทัดเหล่านี้ทั้งหมดจะมีการดึงขึ้นและสามารถละเว้นได้

RG0, RG1, RG2 เป็นการตั้งค่าภูมิภาค

VHz คือการตั้งค่า 50Hz/60Hz สำหรับเอาต์พุตวิดีโอ

/EXP คือสัญญาณ /EXP

PBSY คือสัญญาณ Printer Busy CPC Modular ไม่รวมพอร์ตขนาน สัญญาณนี้สามารถใช้สำหรับการขยายได้หากต้องการ

J1, J2 และ J3 เป็นแจ็คเทป I/O J3 (มอเตอร์) ควรเป็นช่องเสียบแจ็ค 2.5 มม. แต่ขนาดสำหรับช่องเสียบ 3.5 มม.

บอร์ดนี้มีเครื่องกำเนิดเสียง AY-3-8910 และเอาต์พุตที่เกี่ยวข้อง รวมถึงขั้วต่อแป้นพิมพ์และจอยสติ๊ก

ตามที่ระบุไว้สำหรับบอร์ด IO: คุณควรติดตั้งขั้วต่อระหว่างบอร์ด (J902) ที่ด้านบนของบอร์ดนี้ ไม่ใช่ที่ด้านหลังตามที่แสดงในซิลค์สกรีน

บอร์ดมีความสามารถในการใช้ออสซิลเลเตอร์ออนบอร์ดสำหรับอินพุตนาฬิกาของ AY ใน CPC Modular: ละเว้น X1 และติดตั้งจัมเปอร์ที่ปลาย CLK2 ของ JP3 (ซึ่งกำหนดค่าบอร์ดให้ใช้สัญญาณนาฬิกาจากอาร์เรย์เกตที่ส่งผ่านแบ็คเพลน)

จัมเปอร์ที่อยู่เหนือ J103 (แจ็คสัญญาณเสียงออก) อนุญาตให้ส่งสัญญาณเสียงต่างๆ ไปยังพินแบ็คเพลนที่หลากหลาย ในกรณีส่วนใหญ่สามารถเปิดทิ้งไว้ได้ โปรดทราบว่าการตั้งค่าบางอย่างอาจขัดแย้งกับสัญญาณเทปที่ส่งผ่านแบ็คเพลนบนบอร์ด IO

หากติดตั้งแจ็คเสียงไว้ สัญญาณซ้ายและขวาจะไม่ถูกส่งไปยังแบ็คเพลน (หากกำหนดค่าให้ทำเช่นนั้น - ดูรายการก่อนหน้า) อย่างไรก็ตาม เสียง MIX จะยังคงถูกส่งไป (หากกำหนดค่าไว้)

CP2 คือช่องเสียบคีย์บอร์ด สิ่งนี้ใช้ pinout เดียวกันกับ Amstrad CPC464 ดั้งเดิม (แป้นพิมพ์ PCB)

J102 เป็นขั้วต่อจอยสติ๊ก ตัวเชื่อมต่อที่นี่ถูกติดตั้ง 'ในบอร์ด' เล็กน้อยเกินไป และอาจทำให้ PCB สั้นในซ็อกเก็ตถัดไป

ฮาล/PAL:

รหัสสำหรับต้นฉบับ: https://www.cpcwiki.eu/index.php/PAL16L8

การแทนที่ WiP: https://github.com/Bread80/GreenHAL

การเปลี่ยน WiP: https://www.cpcwiki.eu/forum/index.php?msg=231084

อาร์เรย์เกท:

การทดแทนที่ใช้ WiP FPGA: https://github.com/codedchip/AMSGateArray

รูปภาพ ROM: https://www.cpcwiki.eu/index.php/ROM_List

ใบอนุญาต: CERN-OHL-P

ลิขสิทธิ์© ไมค์ ซัตตัน, 2023

เว็บไซต์: https://bread80.com

โซเชียลมีเดีย (มาสโตดอน): https://mstdn.social/@bread80

ไม่มีประโยชน์อะไรนอกเหนือจากนี้ แต่ถ้าคุณทำมาไกลขนาดนี้ คุณก็คงจะไปต่อได้

TX/RX=เสียง (ซ้าย, ขวา) **จัมเปอร์ (อุปกรณ์เสริม) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC (วิดีโอไปยัง IO) USR4=

/WAIT=READY (เป็นอยู่แล้ว!) CLOCK2=/CPU_ADDR (บอร์ด RAM; นาฬิกา 1MHz สำหรับเสียง) RX2=เทปเข้า **Jumpered (อุปกรณ์เสริม) TX2=เทปออก **Jumpered (อุปกรณ์เสริม) USR5=RAMDIS MOVED USR6=/ RAMRD ย้าย USR7=มอเตอร์ **จัมเปอร์ (อุปกรณ์เสริม)

D8-D15=บัสวิดีโอ

D8-D15=บัส IO ???สัญญาณควบคุม???

ตำแหน่ง=รูแถวบนสุด @ 45.72 มม. เหนือกึ่งกลางของพินส่วนหัว RC2014 พื้นฐาน พินซ้ายสุด = จุดกึ่งกลางระหว่าง A9 และ A8 พิน 1 ทางด้านขวา 1 GND 2 HSYNC (นิ้ว) 3 DISPEN (นิ้ว) 4 GND 5 /RAS ( ออก) 6 /CAS (ออก) 7 /MWE (ออก) 8 /CCLK (ออก) 9 /244EN (ออก) 10 จีเอ็นดี

ตำแหน่ง=รูแถวบนสุด @ 43.18 มม. เหนือกึ่งกลางของพินส่วนหัวที่ขยายออก พินซ้ายสุด = จุดกึ่งกลางระหว่างพิน D2 และ D3 พิน 1 ไปทางซ้าย บริเวณทั้งหมดอยู่ที่แถวบนสุด 1=GND 2=HSYNC (ใน) 3=DISPEN (ใน) 4=/CCLK (ออก) 5=/XCPU_ADDR (ออก) 6=/RAMCS (ออก) 7=GND 8=/RAMOE (ออก) 9=GND 10 =/RAMWE (ออก) 11=RAMA14 (ออก) 12=RAMA15 (ออก) 13=RAMA16 (ออก) 14=RAMA17 (ออก) 15=GND 16=RAMA18 (ออก)

1=GND 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=GND

พินเอาท์ของ Amstrad/MX4

GND เสียง Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK พร้อมแล้ว Y Y BRST รีเซ็ต Y? ใช่ไหม? ใช่ไหม? ใช่ไหม? ใช่ไหม? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS เคอร์เซอร์ Y LPEN Y EXP Y Y GND CLK4 Y Y

พิเศษ (วิดีโอ-RAM): RD7..RD0 มี Y Y RAS Y Y CAS Y Y MWE Y Y 244EN Y Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y (24 บรรทัด)

พิเศษ (Video-RAM และ IO-Sound): CPU_ADDR(1MHz) ใช่ ใช่ VSYNC ใช่ ใช่ (2 บรรทัด)

พิเศษ (เสียง IO): PA7..PA0 มี มี มอเตอร์ มี CASRD มี CASWR มี PRINTBUSY (Y) BC1 มี มี BDIR มี PC3..PC0 มี มี ซ้าย มี ขวา มี (20 บรรทัด)

ดิสก์: ต้องใช้ภายในประมาณ 14 บรรทัด

วิดีโอ/RAM: 50 + 24 + 2 = 76 บรรทัด! ทั้งหมด. ไม่จำเป็นน้อยลง: ทั้งหมด 69 บรรทัด (70 บวกหนึ่งสำรอง!) IO/เสียง: รวม 50 + 20 + 2 = 72 บรรทัด ไม่จำเป็นน้อยลง: รวม 50 รายการ (รวมอะไหล่สำรองสองสามรายการ) ดิสก์: 50 + 14 = รวม 64 บรรทัด

หมายเหตุ: ขั้วต่อขอบ 76 พิน: ความกว้างของบอร์ด = 99.06 มม

บอร์ด: ส่วน MX4: CPU ROM ขั้วต่อ RC2014 Edge สำรอง

ส่วนวิดีโอ (อาร์เรย์เกต): การควบคุม RAM วิดีโอ RAM

ส่วนวิดีโอ (RP2040): ตัวรับส่งสัญญาณ RAM สัญญาณวิดีโอ

ส่วนของดิสก์: ตัวเชื่อมต่อ/บัฟเฟอร์คอนโทรลเลอร์

ส่วนเสียง IO: แอมป์/มิกเซอร์เสียงเทป PPI AY