บันทึก:

เอกสารสำหรับโครงการนี้กำลังได้รับการอัปเดตเพื่อสะท้อนถึงการเปลี่ยนแปลงสำหรับ Caravel เวอร์ชันที่ออกแบบใหม่

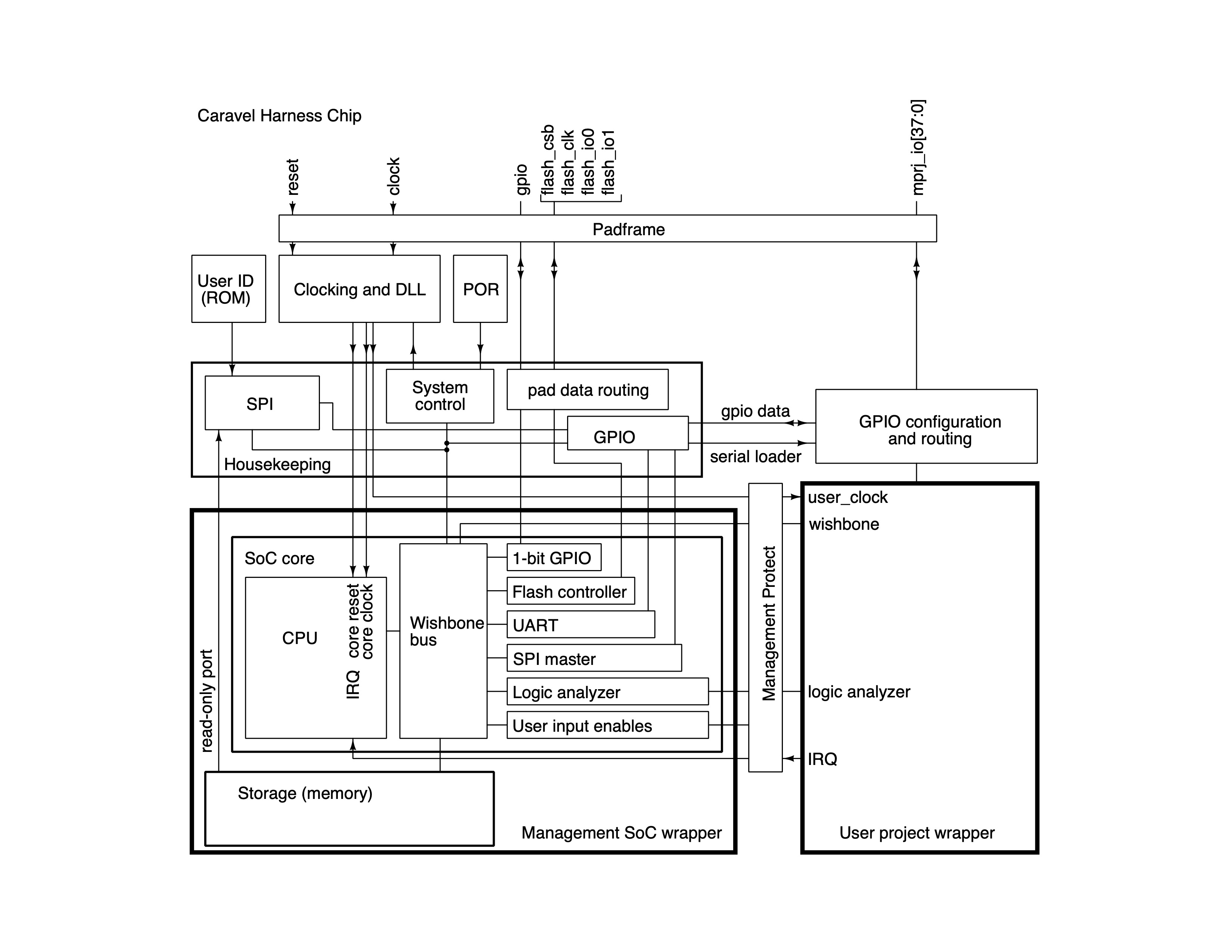

Caravel เป็นเทมเพลต SoC สำหรับ Efabless Open MPW และชิป Ignite ที่อิงตามโหนด Sky130 จาก SkyWater Technologies สถาปัตยกรรม SoC ปัจจุบันได้รับด้านล่าง

เอกสารข้อมูลและเอกสารโดยละเอียดมีอยู่ที่นี่

Caravel ประกอบด้วยโครงบังเหียนพร้อมเสื้อคลุม 2 อันสำหรับโมดูลแบบดรอปอินสำหรับ พื้นที่การจัดการ และ พื้นที่โครงการของผู้ใช้

ชุดสายรัดประกอบด้วยโมดูลการตอกบัตร, DLL, ID ผู้ใช้, SPI ดูแลทำความสะอาด, POR และการควบคุม GPIO

การจัดการ GPIO ย้ายออกจาก SoC การจัดการและเข้าสู่ SPI SPI ได้รับอินเทอร์เฟซแบบวิชโบน SoC การจัดการจะพูดคุยกับ SPI ผ่านทางปีกนก ไม่ใช่โดยการเข้ารับอินเทอร์เฟซ SPI 4 พิน

บล็อกใหม่เช่น ID มีโหมดการเพิ่มพลังสำหรับแต่ละ GPIO สามารถกำหนดค่าด้วยไฟล์ข้อความ หมุด SPI ได้รับการแก้ไขสำหรับการดำเนินการเมื่อเริ่มต้นระบบ

เมื่อเปิดเครื่อง SPI จะกำหนดค่า GPIO โดยอัตโนมัติ โหลดแบบแมนนวลสามารถทำได้จากทั้ง SPI และจากบัสวิชโบน

ฟังก์ชันทั้งหมดภายในชุดสายไฟแต่อยู่ภายนอก SoC การจัดการจะรวมอยู่ในโมดูลขนาดใหญ่โมดูลเดียวที่เรียกว่า "การดูแลทำความสะอาด" ซึ่งรวมถึงการลงทะเบียนจำนวนหนึ่งสำหรับฟังก์ชันที่รวมไว้ทั้งหมด โดยมีอินเทอร์เฟซ SPI "ประตูหน้า" ที่เชื่อมต่อกับเฟรมแพดผ่านพิน GPIO 1 ถึง 4 และอินเทอร์เฟซแบบปีกนก "ประตูหลัง" ที่เชื่อมต่อกับ SoC การจัดการ Soc การจัดการสงวนบล็อกหน่วยความจำไว้ที่ 0x26000000 สำหรับโมดูลการดูแลทำความสะอาด โมดูลการดูแลทำความสะอาดจะแลกเปลี่ยนข้อมูลกับ SoC การจัดการผ่านอินเทอร์เฟซที่ใช้ข้อมูลการลงทะเบียน SPI ทั่วทั้งไบต์ เครื่องสถานะขนาดเล็กจะอ่านที่อยู่ปีกนกสี่ที่อยู่ติดกัน และเครื่องถอดรหัสที่อยู่จะกำหนดการลงทะเบียน SPI ที่สอดคล้องกัน เครื่องสถานะจะหยุด SoC จนกว่าจะจัดการไบต์ทั้งสี่ก่อนที่จะส่งสัญญาณตอบรับกลับ

พื้นที่การจัดการเป็นโมดูลแบบดรอปอินที่ใช้งานเป็น repo แยกต่างหาก โดยทั่วไปจะมี SoC ที่ใช้ RISC-V ซึ่งมีอุปกรณ์ต่อพ่วงจำนวนหนึ่ง เช่น ตัวจับเวลา uart และ gpio พื้นที่การจัดการจะรันเฟิร์มแวร์ที่สามารถใช้เพื่อ:

พื้นที่การจัดการใช้ SRAM สำหรับ SoC การจัดการ

คุณสามารถดูอินสแตนซ์เริ่มต้นสำหรับแกนการจัดการได้ที่นี่ ดูเอกสารประกอบของแกนการจัดการสำหรับรายละเอียดเพิ่มเติม

นี่คือพื้นที่ผู้ใช้ มีพื้นที่ซิลิคอนจำกัด 2.92mm x 3.52mm เช่นเดียวกับแพด I/O จำนวนคงที่ 38 และพาวเวอร์แพด 4

พื้นที่ผู้ใช้สามารถเข้าถึงยูทิลิตี้ต่อไปนี้ที่ SoC การจัดการมอบให้:

38 พอร์ต IO128 หัววัดวิเคราะห์ลอจิก พื้นที่ของคุณคือพื้นที่ผู้ใช้เต็มรูปแบบ ดังนั้นคุณสามารถเพิ่มโปรเจ็กต์ของคุณที่นั่นหรือสร้างมาโครอื่นและทำให้แยกจากกัน จากนั้นแทรกลงใน user_project_wrapper สำหรับโปรเจ็กต์ดิจิทัล หรือแทรกลงใน user_project_analog_wrapper สำหรับโปรเจ็กต์แอนะล็อก

หากคุณกำลังสร้างโปรเจ็กต์ดิจิทัลสำหรับพื้นที่ผู้ใช้ ตรวจสอบโปรเจ็กต์ตัวอย่างได้ที่ caravel_user_project

หากคุณจะใช้ OpenLANE เพื่อทำให้การออกแบบของคุณแข็งแกร่งขึ้น ให้ทำตามคำแนะนำใน README นี้

โครงการผู้ใช้ดิจิทัลควรปฏิบัติตามข้อกำหนดต่อไปนี้:

user_project_wrapperuser_project_wrapper ปฏิบัติตามลำดับพินที่กำหนดไว้ในลำดับพินของ Digital Wrapperuser_project_wrapper ปฏิบัติตามการกำหนดค่าการออกแบบคงที่ที่ Digital Wrapper Fixed Configurationหากคุณกำลังสร้างโปรเจ็กต์แอนะล็อกสำหรับพื้นที่ผู้ใช้ ให้ตรวจสอบโปรเจ็กต์ตัวอย่างที่ caravel_user_project_analog

โปรเจ็กต์ผู้ใช้แบบอะนาล็อกควรปฏิบัติตามข้อกำหนดต่อไปนี้:

user_analog_project_wrapperuser_analog_project_wrapper ใช้ wrapper อะนาล็อกที่ว่างเปล่าuser_analog_project_wrapper ยึดตามลำดับพินและตำแหน่งของ wrapper อะนาล็อกที่ว่างเปล่า โปรดตรวจสอบให้แน่ใจว่าได้เรียกใช้ make compress ก่อนที่จะส่งข้อมูลใดๆ ไปยังพื้นที่เก็บข้อมูลของคุณ หลีกเลี่ยงการมี gds/user_project_wrapper.gds 2 เวอร์ชัน เวอร์ชันหนึ่งถูกบีบอัดและอีกเวอร์ชันไม่บีบอัด

สำหรับข้อมูลเกี่ยวกับเครื่องมือและการกำหนดเวอร์ชัน โปรดดูที่ tool-versioning.rst

gds/ : รวมไฟล์ gds ทั้งหมดที่ใช้หรือผลิตจากโปรเจ็กต์def : รวมไฟล์ def ทั้งหมดที่ใช้หรือผลิตจากโปรเจ็กต์lef/ : รวมไฟล์ lef ทั้งหมดที่ใช้หรือผลิตจากโปรเจ็กต์mag/ : รวมไฟล์ mag ทั้งหมดที่ใช้หรือผลิตจากโปรเจ็กต์maglef : รวมไฟล์ maglef ทั้งหมดที่ใช้หรือผลิตจากโครงการspi/lvs/ : รวมไฟล์เครื่องเทศทั้งหมดที่ใช้หรือผลิตจากโปรเจ็กต์verilog/dv : รวมม้านั่งทดสอบการจำลองทั้งหมดและวิธีการใช้งานverilog/gl/ : รวม netlists ที่สังเคราะห์/ซับซ้อนทั้งหมดverilog/rtl : รวม Verilog RTL และไฟล์ต้นฉบับทั้งหมดopenlane/<macro>/ : รวมไฟล์การกำหนดค่าทั้งหมดที่ใช้ในการรัน openlane บนโปรเจ็กต์ของคุณinfo.yaml : รวมข้อมูลทั้งหมดที่จำเป็นในตัวอย่างนี้ โปรดตรวจสอบให้แน่ใจว่าคุณกำลังชี้ไปที่รายการ caravel netlist ที่ละเอียด รวมถึงรายการ netlist ระดับเกทที่สังเคราะห์แล้วสำหรับ user_project_wrapperบันทึก:

หากคุณใช้ openlane เพื่อทำให้การออกแบบของคุณแข็งแกร่งขึ้น ไดเร็กทอรีverilog/gldef/lef/gds/magmaglefควรได้รับการเติมข้อมูลโดยอัตโนมัติโดย openlane

ตรวจสอบ mpw-one-final เพื่อหาคาราเวลที่ใช้สำหรับเทปเอาท์ mpw-one

-make ship อีกต่อไป