***该项目是一项未完成的正在进行中的工作。目前它存在错误,并且尚未测试所有功能!

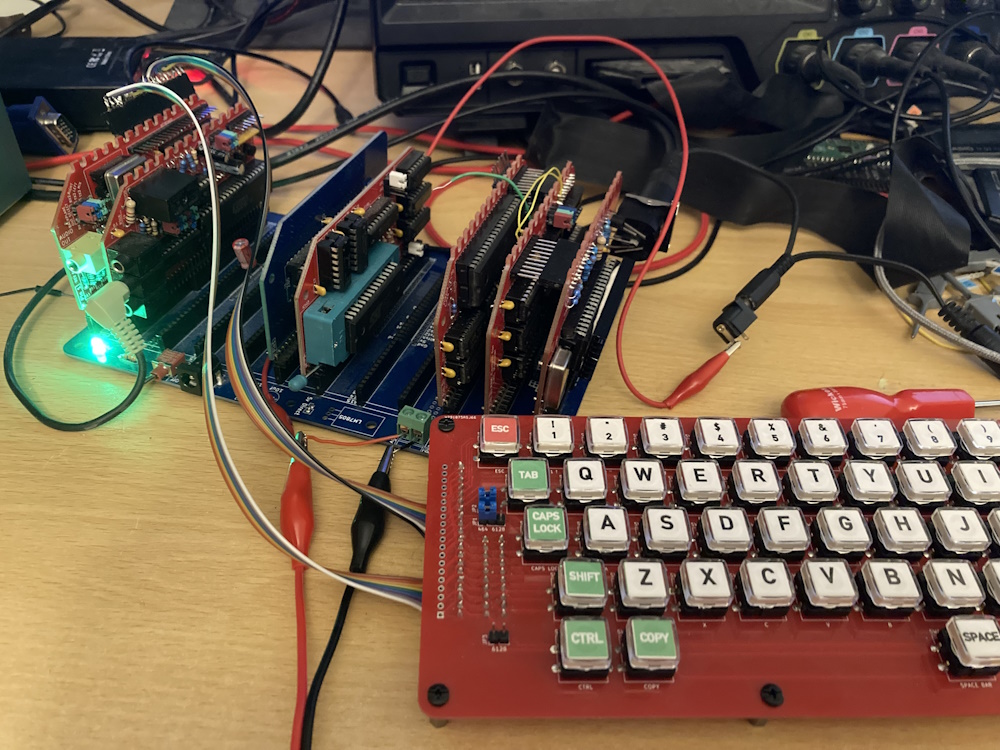

当前模块设计用于安装稍作修改的 RC2014 Pro 背板。在下面的文字中,我将解释该项目的当前状态、使其运行所需的解决方法以及基本的构建细节。由于该项目的进展状态,本文档将刻意简洁。

该项目使用排针/插座连接子系统(视频 RAM 子系统和 IO 声音子系统)内的模块。这需要比平常更长的排针。

这是经过稍微修改的 RC2014 Pro 背板。 CPC Modular 在视频 RAM 子系统和 IO-声音子系统中使用 D8 至 D15 线作为本地数据总线。所以:

您需要切断这些路段之间的 D8 至 D15 线。

这是一个稍微修改的RC2014“Z80 CPU模块”。修改:

板上的电阻器需要更换为不同的值。 2.2k 欧姆应该可以正常工作。

该板包含 512Kb NORFLASH。它包括使闪存能够就地烧录的电路(未经测试)。配置:

需要安装跳线来桥接 LK4 的引脚 2 和 LK5 的引脚 2。

要启用闪存刻录,请安装链接 LK1、LK2 和 LK3。否则保持打开状态。

我写入闪存的注释(取自原理图文件)是:

!!!无法在标准 CPC 系统上禁用内存写入。因此,当 WRITE_EN 处于活动状态时,我们对 ROM 进行的任何内存写入也将写入 RAM。

然而,由于 ROM 映射到任何和所有存储体,这增加了一定程度的灵活性。另请注意,从 ROM 读取被禁用,而写入被启用。这意味着当 ROM 处于活动状态时,我们可以从 ROM“下方”的 RAM 中读取数据。

我推荐的编程过程是使用视频 RAM 地址写入 ROM,但是如果该内存范围不包含有意义的数据,则 ROM 可能会使用存储体 1 (&4000-&7fff) 中的地址写入。 (如果要写入的数据已经在此地址范围内,则程序员可以简单地读取数据(RAM),然后在同一地址写入(ROM)。不过,需要小心发送到 ROM 的命令,因为这些命令仍然会丢弃下面的数据)。

读取要编程地址处的 RAM 字节。

打开 ROM 的写入使能

将所需数据写入 ROM。

关闭 ROM 的写入使能

将原始数据写回ROM。

ROM (NORFLASH) 最多可容纳 31 个 ROM 以及固件 ROM。对芯片进行编程时,固件需要进入插槽 31(从地址 &7c000 开始)。 BASIC(如果已安装)需要进入插槽 0(地址 &00000)。 ROM 插槽位于每 &4000 字节,即 &00000、&04000、&08000、&0C000、&10000 等。

如果使用 XGPro 软件刻录 ROM:

使用 Select IC 选择正在使用的 IC (SST39FS040)。

单击“加载”工具栏按钮。

选择要加载的文件。

文件格式:二进制(对于 .ROM 文件)

至区域:默认

负载模式:正常

从文件开始地址:0000

To Buffer Start Addr:ROM 插槽起始地址(&7C000 对于固件,&00000 对于 BASIC)

加载文件时清除缓冲区:“默认情况下清除缓冲区”选项将覆盖任何以前加载的数据!将其用于加载到 XGPro 中的第一个 ROM(这将初始化整个 ROM)。对于所有其他 ROM,选择“禁用”(这将仅将数据加载到选定的插槽中)。

单击“确定”并验证您的文件已加载到正确的地址并且未被覆盖。

单击 PROG(工具栏)

单击程序。

该板包含门阵列和视频输出。

与 RAM 控制板上的等效接头上的信号相比,JP901 上的 DISPEN 和 HSYNC 信号被交换。这最好固定在 RAM 控制板上(见下文)。

视频输出电路来自 CPC464,但不知何故,我使用了 CPC6128 的元件值,但减去了 '6128 上的电容器。这可能不会产生显着差异。

在我的测试中,我使用与 Amstrads 通常使用的相同 SCART 转 HDMI 适配器,但这里它显示黑白图像,或者根本没有图像。这似乎是电缆使用的 PSU 和适配器之间的问题。它可以通过从 CPC 模块化板向电缆馈送 5V 电源来固定。

该板包含 40007 和 40010 门阵列的封装(40008 也应该可以使用)。足迹重叠以节省空间。您应该能够通过分离两排引脚并移除它们之间的织带来包含两者的插座,但是,足迹太靠近,无法轻松做到这一点。

DIN 插座底座上的孔有点太小。

该板容纳视频数据总线和 CPU 数据总线之间的链路,处理信号以使它们适合 SRAM 存储器,并容纳大于 64k 的存储器所需的可选组件(未经测试)。

驱动/RAMOE 的电路不正确。要修复它:

剪断 U192 引脚 1 和 13 之间的走线

剪断 U192 引脚 11 和 U193 引脚 1 之间的走线

在 U192 引脚 1 和 U195 引脚 9 之间安装电线

在 U195 引脚 8 和 U193 引脚 1 之间安装电线

如视频板所述,DISPEN 和 HSYNC 引脚在板之间的连接器上交换。要解决此问题:

剪断 J1 引脚 2 和 J2 引脚 2 之间的走线

剪断 J1 引脚 3 和 J2 引脚 3 之间的走线

在 J1 引脚 2 和 J2 引脚 3 之间安装电线

在 J1 引脚 3 和 J2 引脚 2 之间安装电线

要使用 <= 64k RAM 安装链接 LK5、LK6 和 LK7。如果是这样,请勿插入 IC118 和 U194

要使用 > 64k RAM,请保持 LK5、LK6、LK7 打开并安装 IC118 和 U194。 IC118 是标准 Amstrad HAL/PAL。

驱动/RAMOE 的正确电路是:

XCPU_AD-----| |-- /XCPU_AD-- AND---/ROMOE OR--- /RAMRD----

文本形式: /ROMOE := XCPU_AD AND (/XCPU_AD OR /RAMRD)

XCPU_AD 可源自 U195 引脚 8。

该板包含 6845 CRTC、地址多路复用器和 512Kb SRAM。这里没有问题,也不需要配置。

如果需要,可以为 CURSOR 和 LPEN 安装标头。他们可能不是。

该板包含 8255 PIO 和磁带接口。安装焊线和跳线以使 I/O 地址可配置:

该板的设计使得 IO 板可以安装在它的“上方/前面”,但继电器太高而不允许这样做。因此:我建议您将 J902 安装在板的背面(这是声音板的连接器)。

在板的背面,找到地址引脚上方的焊点。在每个链接上,您需要将“高”地址焊盘(标记为 A7(原文如此)至 A15)焊接到中央焊盘。 “低”地址焊盘 (A0..A7) 不得连接到中心焊盘。

在板的正面找到位于 U1 和 D302 之间的链接。您需要为标记为 A3 的链路跳接“低”链路(到中心引脚),为其他链路(A2、A4、A5、A6、A7)跳接高链路(到中心引脚)。

找到位于 C315 和 J901 之间的链接。配置哪些信号被引导至插孔,哪些信号被引导至背板。推荐的设置是:

在 TO、TI 和 /MO(流带输出、流带输入和电机)的 INT(外部)和中间引脚之间安装链接。

将 /EXP 链接保持打开状态。

J901 允许访问各种 8255 输入信号。默认情况下,所有这些线都有上拉电阻,可以忽略。

RG0、RG1、RG2 为区域设置。

VHz 是视频输出的 50Hz/60Hz 设置。

/EXP 是 /EXP 信号。

PBSY 是打印机忙信号。 CPC Modular 不包含并行端口。如果需要,该信号可用于扩展。

J1、J2 和 J3 是磁带 I/O 插孔。 J3(电机)应该是 2.5mm 插座,但封装适用于 3.5mm 插座。

该板包含 AY-3-8910 声音发生器和相关输出,以及键盘和操纵杆连接器。

如 IO 板所述:您应该将板间连接器 (J902) 安装在该板的顶部,而不是丝印所示的背面。

该板能够使用板载振荡器作为 AY 的时钟输入。在 CPC 模块中:省略 X1 并在 JP3 的 CLK2 端安装跳线(将板配置为使用通过背板发送的门阵列时钟信号)。

J103(音频输出插孔)上方的跳线允许将各种音频信号发送到各种背板引脚。在大多数情况下,这些可以保持打开状态。请注意,某些设置可能与通过 IO 板上的背板路由的磁带信号冲突。

如果安装了音频插孔,则左信号和右信号将不会发送到背板(如果配置为这样做 - 请参阅上一项)。但是,音频 MIX 仍将被发送(如果如此配置)。

CP2是键盘连接器。它使用与原始 Amstrad CPC464(PCB 键盘)相同的引脚排列。

J102 是操纵杆连接器。这里的连接器安装得有点太“内侧”,可能会导致下一个插座中的 PCB 短路。

哈尔/帕尔:

原始代码:https://www.cpcwiki.eu/index.php/PAL16L8

在制品替换:https://github.com/Bread80/GreenHAL

在制品更换:https://www.cpcwiki.eu/forum/index.php?msg=231084

门阵列:

基于 WiP FPGA 的替换:https://github.com/codedchip/AMSGateArray

ROM 图片:https://www.cpcwiki.eu/index.php/ROM_List

许可证:CERN-OHL-P

版权所有 © 迈克·萨顿,2023

网站:https://bread80.com

社交媒体(乳齿象):https://mstdn.social/@bread80

除了这里没有什么有用的。但如果你已经做到了这一步,你可能会继续前进。

TX/RX=声音(左、右) **跳线(可选) USR1=ROMDIS USR2=/ROMEN USR3=VSYNC(视频到 IO) USR4=

/WAIT=READY(已经准备好了!) CLOCK2=/CPU_ADDR(RAM 板;1MHz 声音时钟) RX2=磁带输入 **跳线(可选) TX2=磁带输出 **跳线(可选) USR5=RAMDIS已移动USR6=/ RAMRD MOVED USR7=电机 **跳接(可选)

D8-D15=视频总线

D8-D15=IO总线???控制信号???

位置=顶排孔 @ 基本 RC2014 接头引脚中心上方 45.72mm,最左侧引脚 = A9 和 A8 之间的中点 引脚 1 向右 1 GND 2 HSYNC(输入) 3 DISPEN(输入) 4 GND 5 /RAS( 6 /CAS(输出) 7 /MWE(输出) 8 /CCLK(输出) 9 /244EN(输出) 10 GND

位置 = 顶排孔 @ 延伸接头引脚中心上方 43.18 毫米,最左边的引脚 = D2 和 D3 引脚之间的中点,引脚 1 位于左侧,所有接地均位于最顶行。 1=GND 2=HSYNC(输入) 3=DISPEN(输入) 4=/CCLK(输出) 5=/XCPU_ADDR(输出) 6=/RAMCS(输出) 7=GND 8=/RAMOE(输出) 9=GND 10 =/RAMWE(输出) 11=RAMA14(输出) 12=RAMA15(输出) 13=RAMA16(输出) 14=RAMA17(输出) 15=GND 16=RAMA18(输出)

1=接地 2=BC1 3=BDIR 4=PC0 5=PC1 6=PC2 7=PC3 8=接地

Amstrad/MX4 引脚排列

GND 声音 Y A15 Y Y Y A14 Y Y Y A13 Y A12 Y A11 Y Y A10 Y Y A9 Y Y A8 Y Y Y A7 Y Y A6 Y A5 Y A4 Y A3 Y A2 Y A1 Y A0 Y Y

D7 Y Y Y D6 Y Y Y D5 Y Y Y D4 Y Y Y D3 Y Y Y D2 Y Y Y D1 Y Y Y D0 Y Y Y (CRTC) VCC MREQ Y M1 Y Y RFSH IORQ Y Y Y Y RD Y Y Y Y WR Y Y Y Y HALT INT Y NMI BUSRQ BUSAK READY Y Y BRST RSET Y?是吗?是吗?是吗?是吗? ROMEN Y ROMDIS Y RAMRD Y Y RAMDIS 光标 Y LPEN Y EXP Y Y GND CLK4 Y Y

额外(视频 RAM): RD7..RD0 Y Y Y RAS Y Y CAS Y Y MWE Y Y 244EN Y Y XCPU_AD(?) Y Y RAMCS Y Y RAMOE Y Y RAMWE Y Y RAMA18..RAMA14 Y Y HSYNC Y Y DISPEN Y Y CCLK Y Y(24 行)

额外(视频 RAM 和 IO 声音):CPU_ADDR(1MHz) Y Y Y VSYNC Y Y Y(2 行)

额外(IO-声音):PA7..PA0 Y Y MOTOR Y CASRD Y CASWR Y PRINTBUSY (Y) BC1 Y Y BDIR Y Y PC3..PC0 Y Y LEFT Y RIGHT Y(20 行)

光盘:内部需要约 14 行

视频/RAM:50 + 24 + 2 = 76 行!全部的。不需要的较少:总共 69 条(70 条加上 1 条备用线!) IO/声音:总共 50 + 20 + 2 = 72 条线。不需要的较少:总共 50 个(包括几个备用) 光盘:总共 50 + 14 = 64 行

注:76 针边缘连接器:板宽 = 99.06mm

主板:MX4 部分:CPU ROM 备件 RC2014 边缘连接器

视频部分(门阵列):Video RAM RAM Control

视频部分 (RP2040):视频信号 RAM 收发器

光盘部分:控制器连接器/缓冲器

IO 声音部分:PPI AY 磁带音频放大器/混音器