The UDP Offload Engine is an IP VHDL used for FPGA hardware programming.

This IP is an UDP-IP stack accelerator and is able to send and receive data through Ethernet link. This stack is highly configurable to be used with Ethernet rates up to 40Gb/s thanks to its configurable bus size. Moreover it is modular. It implements different protocols and integrated testing tools that can be deactivated in order to save resources.

This IP is based on Building Blocks following the Thales Strategy in engineering. They perform basic functions and allow to be independent from the platform/target. No manufacturer primitive are used on this design, all are inferred.

Tables of contents

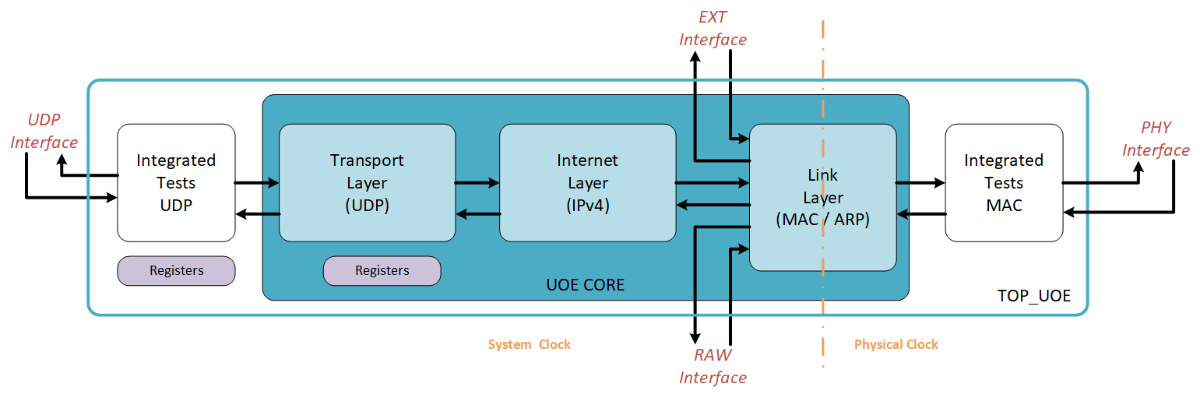

This figure describe the internal architecture of the IP. The main entity is the module uoe_core. It was encapsulated in a top wrapper top_uoe which additionally instantiate some integrated tests functions.

Functional part

Built-In-Test part (Optional)

The Full documentation of the stack is available on the architecture guide.

Configurable bus size

Handle the following protocols

Address Resolution Protocol (ARP)

Internet Control Message Procotol (ICMP)

Take into account buffers on the MAC interface and clock domain crossing

Filtering option for incoming traffic

Use of standard bus

The design has been synthesized and implemented with different generics parameters and for several target in out of context. Result are available on the Performance page.

This repo integrate the following design example :

Coming soon ...

If you are interested in contributing to this project, start by reading the Contributing guidelines.